### **SYNOPSYS**<sup>®</sup>

# AI: Trailblazing the Path of Semiconductor

#### Vishal Khandelwal

Chief Architect, Design Technology Group October 2024

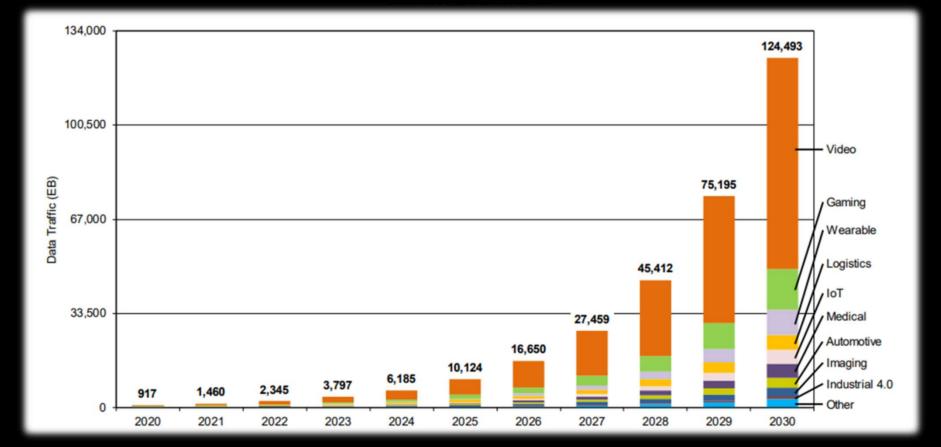

## World is Becoming More Data Intensive

Courtesy: IBS, Impact of Generative AI on Semiconductor Industry, Jan 2024

synopsys<sup>®</sup>

© 2023 Synopsys, Inc.

#### 1011 0100

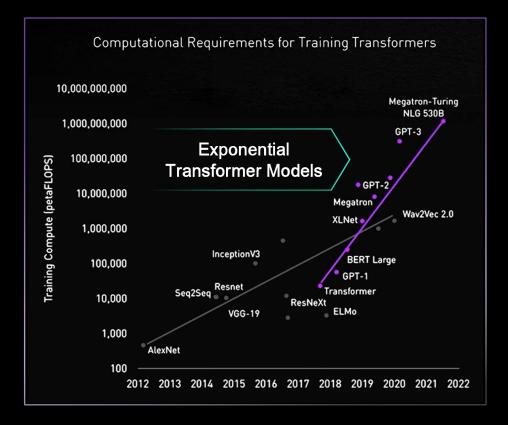

## Newer Models Further Pushing Limits of Compute

Source: https://blogs.nvidia.com/blog/2022/03/25/what-is-a-transformer-model/

#### All Models Excluding Transformers: 8X / 2 years

Transformer AI Models: 275X / 2 years

Context-Aware Transformer Models Come at a Price

synopsys<sup>®</sup>

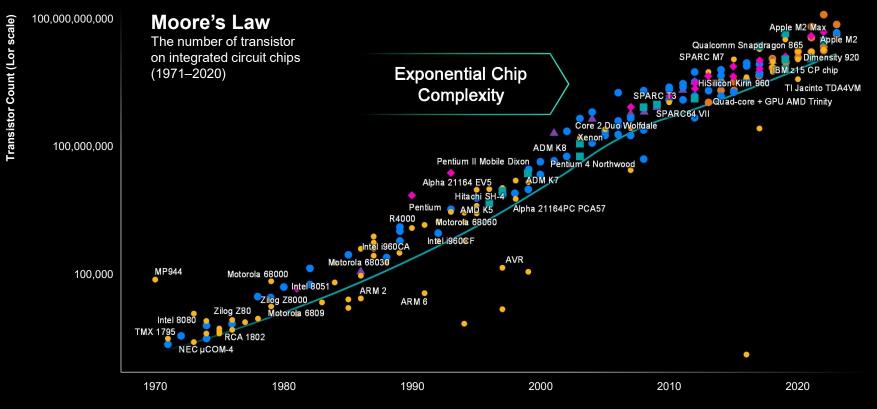

### In Turn, Pushing the Limits of Chip Design

Source: Wikipedia - Transistor Count: https://interludeone.com/posts/2021-04-21-chips/chips\_files/figure-html/unnamed-chunk-4-1.png

#### **Synopsys**®

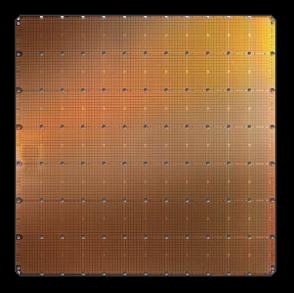

#### The Fourth Industrial Revolution – Powered by Silicon

# Hardware is at the heart of the Al revolution

#### Examples of AI "Super-chips"

#### Cerebras WSE - 2

2.6 trillion transistors TSMC 7nm 850,000 Al-optimized cores

#### Graphcore GC200 IPU

59.4Bn transistors TSMC 7nm @ 823mm<sub>2</sub> 1472 independent processor cores

#### Data center chips for deep learning training and inference

- Trillions of transistors

- Hundreds of thousands of processing elements

## Edge IP (primarily) for deep learning inference

- Mixed scalar/vector/spatial compute

- Ultra energy efficient: Several TOP/s/**W**

#### **Synopsys**®

### Why AI, Why Now?

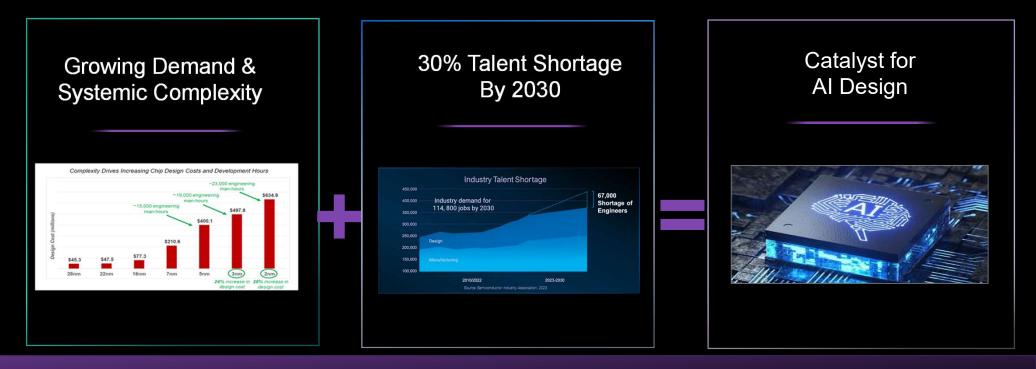

Chip Design Complexity, Cost and Labor Shortage Drive the need for Productivity

Chip Design Complexity, Cost and Labor Shortage Drive the Need for Productivity

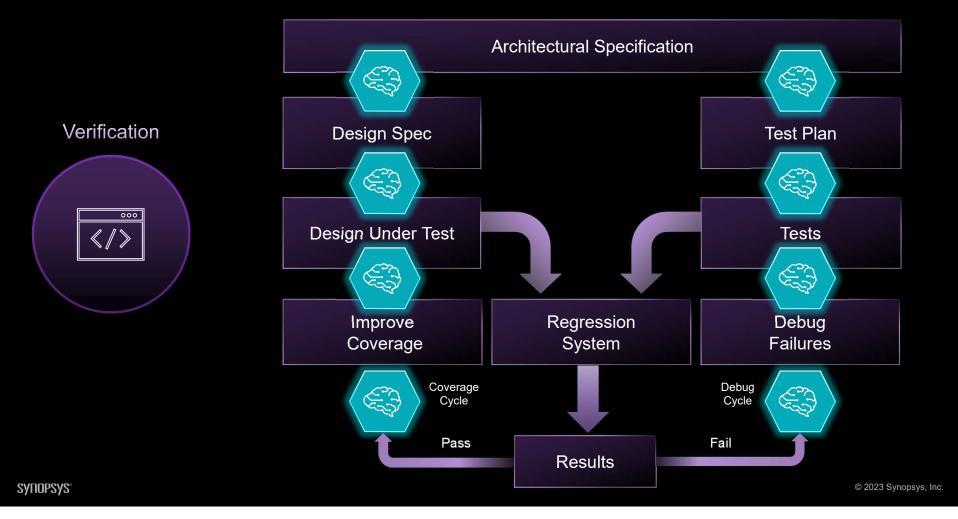

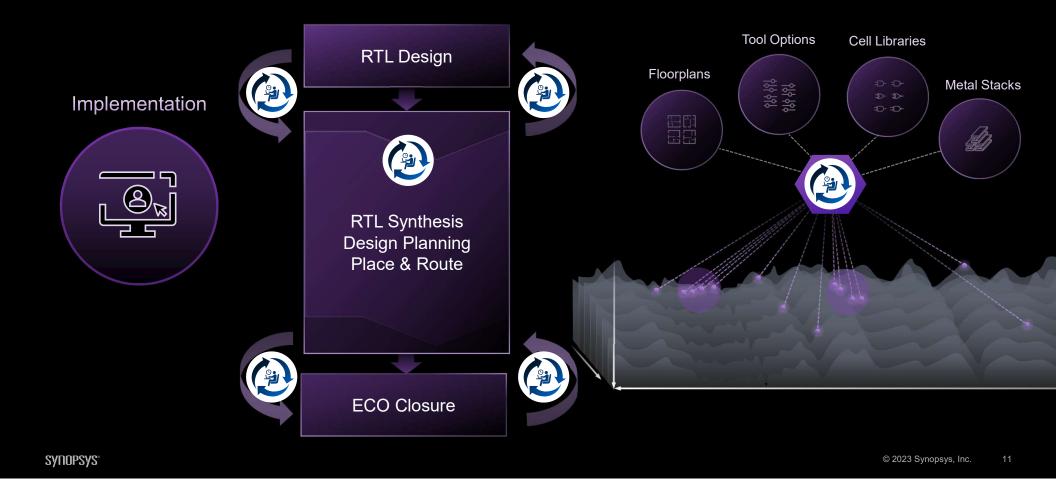

## EDA Workflow Offers Opportunities for Al

#### EDA Workflow Offers Opportunities for AI

#### EDA Workflow Offers Opportunities for AI

#### EDA Workflow Offers Opportunities for AI

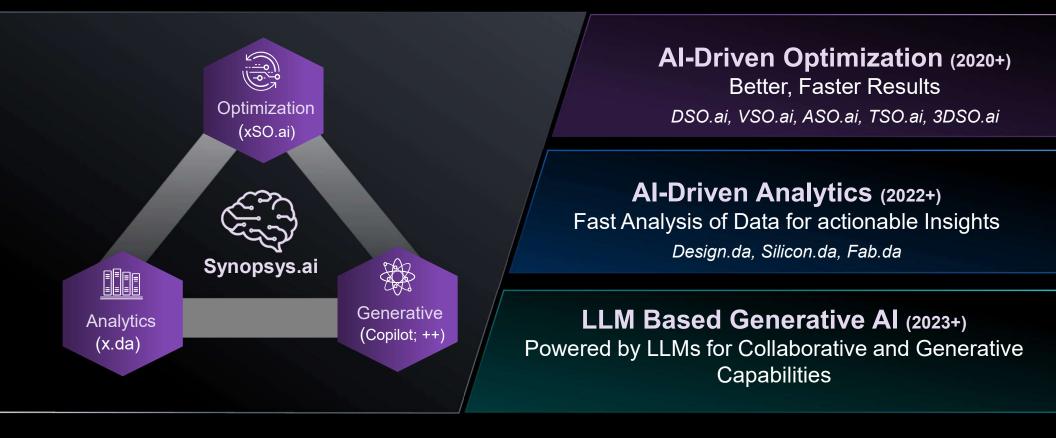

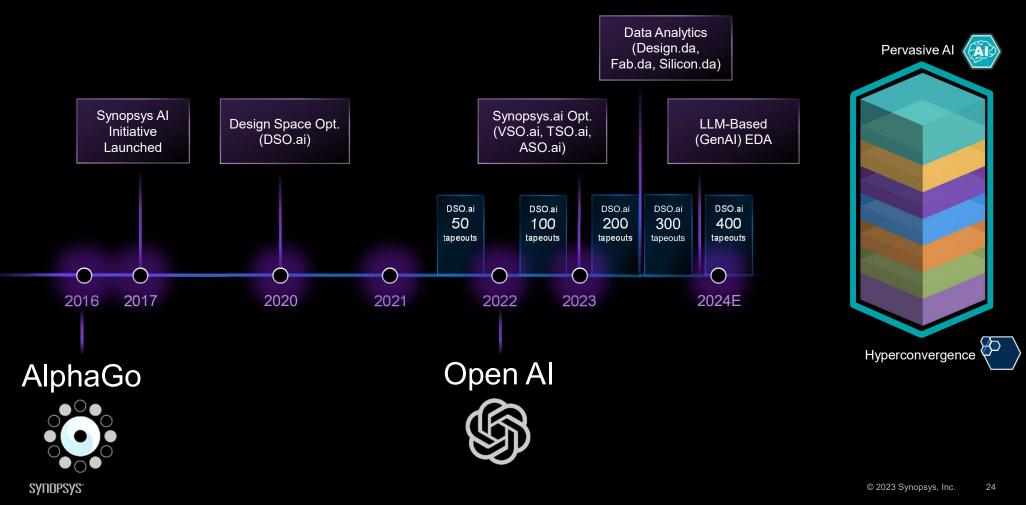

#### Pervasive AI: Synopsys Pioneered AI Driven Chip Design

synopsys<sup>®</sup>

### Trillions of Devices: Evolving to System(s) OF Chips

Highly heterogeneous, multi-die systems

#### Motivation for Multi-Die Systems

Accelerated scaling of system functionality at a cost-effective price

Reduced risk & time-to-market by re-using proven designs/die

Lower system power while increasing throughput

Rapid creation of new product variants for flexible portfolio management

## New Dimensions, Expanding Challenges...

**Synopsys**<sup>®</sup>

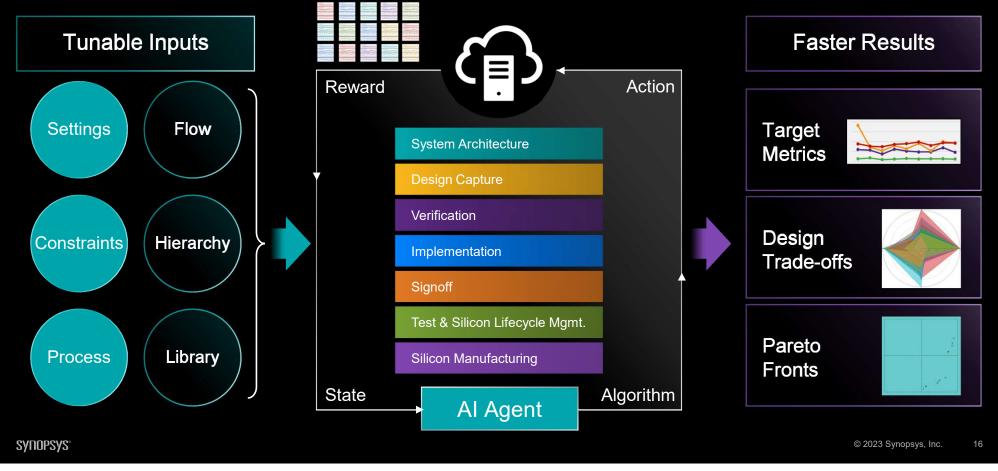

| Architectural<br>Design | System Architecture            | <ul> <li>Performance</li> <li>Frequency, WNS, TNS,</li> </ul>                            |  |  |

|-------------------------|--------------------------------|------------------------------------------------------------------------------------------|--|--|

|                         | Design Capture                 | CTS latency,                                                                             |  |  |

| Structural<br>Design    | Verification                   | <ul> <li>Area</li> <li>Die area, std cell area,</li> <li>Area by cell VT,</li> </ul>     |  |  |

| Logic<br>Design         | Implementation                 | <ul> <li>Power Leakage</li> <li>Leakage</li> <li>Leakage by cell type, by VT,</li> </ul> |  |  |

|                         | Signoff                        |                                                                                          |  |  |

| Layout<br>Design        | Test & Silicon Lifecycle Mgmt. | Example : 10 <sup>25</sup> for latest Arm CPU                                            |  |  |

|                         | Silicon Manufacturing          | Can Al Help?                                                                             |  |  |

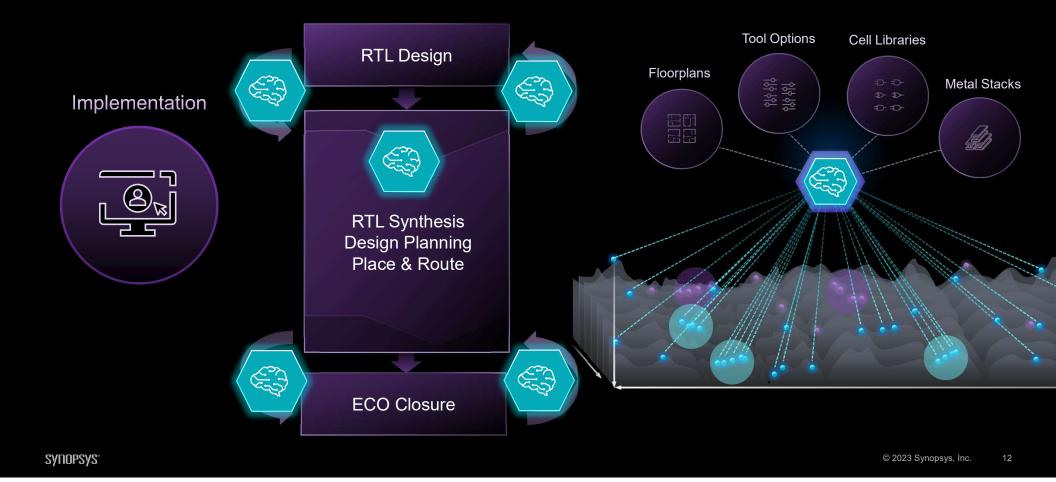

## Digital Implementation: Applying AI to Navigate Chip Design Solution Space

## Digital Implementation: High Performance CPU Core

#### Al-driven Optimization Results

RISC-V based "Big Core" targeted Perf. Power Area for data center applications Size: 426um x 255um (single core only) Target Technology process: 5nm 1.95Ghz 30mW MET **User Expectation Baseline** 1.75Ghz 29.8mW MET **OOTB RISC-V Reference Flow** 2 days, 90 runs, 0 human! DSO.ai 1.95Ghz 27.9mW MET Al-Driven RISC-V **Reference Flow**

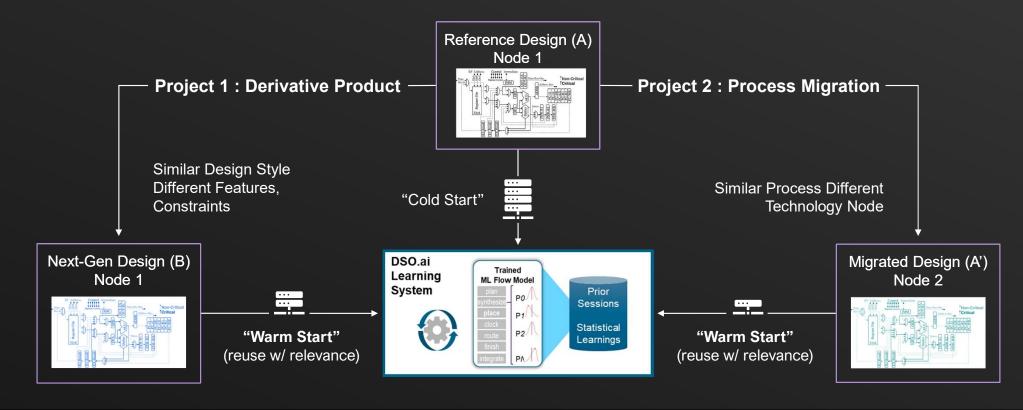

# Digital Implementation: Cross-Design Learning for Project

synopsys°

## **Digital Implementation: Node Migration using AI**

| <ul> <li>RISC-V based "Big Core" targeted<br/>for data center applications</li> </ul>      | Perf.                                               | Power                     | Area   |      |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------|--------|------|

| <ul> <li>Size: 404um x 242um (10% shrink)</li> <li>Technology: <u>5nm → 4nm</u></li> </ul> | <b>Target</b><br>User Expectation                   | 2.1Ghz                    | 30mW   | -10% |

|                                                                                            | <b>Baseline</b><br>OOTB RISC-V<br>Reference Flow    | 1.85Ghz                   | 28.4mW | -10% |

|                                                                                            |                                                     | 1 days, 15 runs, 0 human! |        |      |

|                                                                                            | <b>DSO.ai</b><br>Al-Driven RISC-V<br>Reference Flow | 2.15Ghz                   | 29.4mW | -10% |

synopsys®

Synopsys Confidential Information

## What's next in Digital Implementation?

EDA R&D perspective

- Design Learning Driven Auto-Convergence

- Graduate from point AI/ML applications

- EDA tools become a fully learning-driven system to drive end-end convergence

- Auto-convergence to target different user personas

- Virtual designers

- "Green" designers

- "Expert" designers

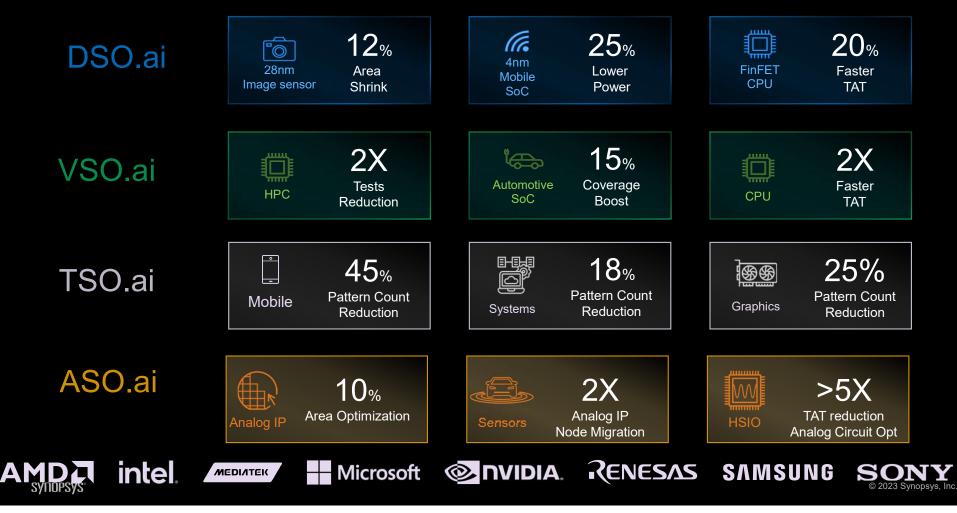

#### Market Leaders Realizing Significant Gains from Synopsys.ai

life2duamented

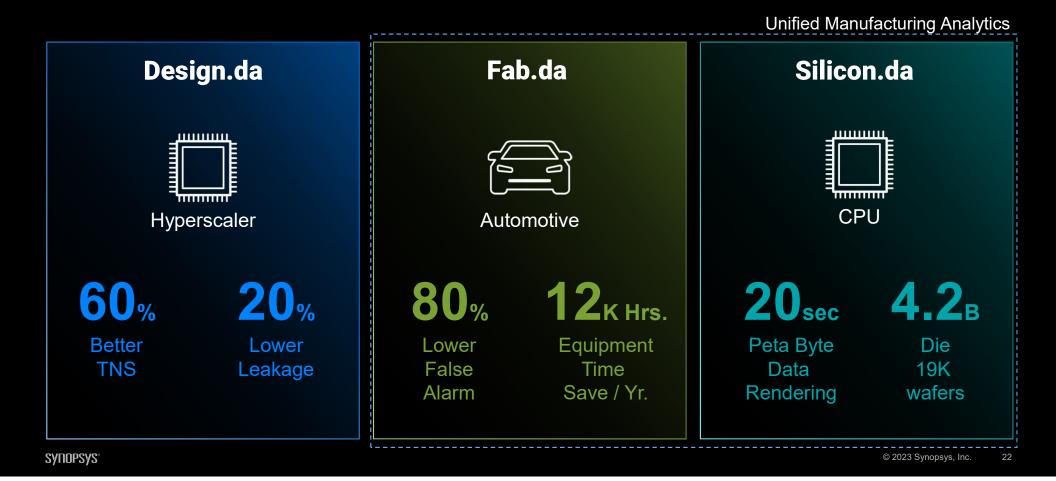

### Al-Driven Data Analytics Improving Productivity and QoR

#### GenAl-based EDA Apps Driving Wide Scale Productivity

"30% faster ramp-time for junior engineers without having to depend on expert engineers"

"We can focus on the critical tasks while GenAI is taking care of the mundane stuff"

"The responses are at least 2x faster to expert queries than the search process"

intel. AMDZ Microsoft

#### Blistering Pace of Al Innovations

## AI, The Only Way Forward

© 2023 Synopsys, Inc. 25

# Thank You