# Design-for-Test in 2D is hard! What can you expect for 3D?

Dr. Martin Keim Senior Engineering Director Tessent Test

SIEMENS

EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

### **Motivation**

Design-for-Test is always challenged by latest design complexities

- Today: AI Chips

- Example

- ~1 GB of on-chip memory across >60k memory instances

- 4000 Memory BIST controllers

- 1200 Logic BIST controllers

- 1500 Embedded compression logic test controllers

- 2500 OCCs

- 2000 Test mode control bits

- 50 embedded 1149.1 TAP controllers

- Loads of on-chip monitors and sensors

• ...

A single test setup might take 7-10M cycles at JTAG speed

Not counting actual test patterns

### **Motivation**

Design-for-Test is always challenged by latest design complexities

- Today: AI Chips

- Example

- ~1 GB of on-chip memory across >60k memory instances

- 4000 Memory BIST controllers

- 1200 Logic BIST controllers

- 1500 Embedded compression logic test controllers

- 2500 OCCs

- 2000 Test mode control bits

- 50 embedded 1149.1 TAP controllers

- Loads of on-chip monitors and sensors

- ...

Unfortunately, one driver for 3D are those high-demand designs

### Agenda

Requirements of multi-die (2.5D / 3D) DFT

State-of-the-art 2D DFT

Expanding into multi-die

Role of test standards, actual and industry published

Summary

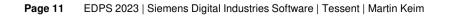

## **Requirements of multi-die DFT**

Ensure the assembled product is defect free

- Each 2D die (chiplet, tile, ...) is defect free

- The 3D stack, 2.5D assembly is defect free

Cost considerations and trade-offs

- Known Good Die (KGD)

- Wafer-level die interconnect test

- Partial stack test

- Stack-level interconnect test & repair

- Reuse die-level DFT as much as possible for stack-level

- Hardware and test patterns

- Allow heterogenous 3D integration also for DFT

**3D device**

# State-of-the-art 2D DFT What is important for 3D ?

EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

### State-of-the-art 2D DFT – What is important for 3D ?

### 1. Test time

- Test delivery to die

- Test response off die

- Diagnosis volume data collection, logic and memory

### 2. Test access

- Wafer-level die IO access is very narrow

- 3. Tool compute resources

- Inability to represent the entire die in memory

- Compute pattern once, map to die test access architecture

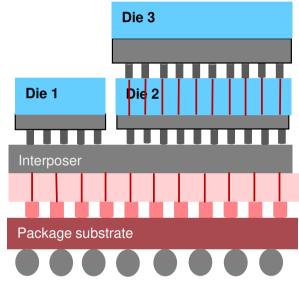

Narrow, high bandwidth interface at die IO

High bandwidth test distribution method on chip

Configurable for wafer / package

Hierarchical test methodology

Page 16 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

# Scan

- Developed to fully automate test pattern generation

- Necessary for debugging and diagnosis

# **Test compression**

- Developed to reduce the cost of test

- Two orders of magnitude reduction of test data volume and time

- Based on scan DFT

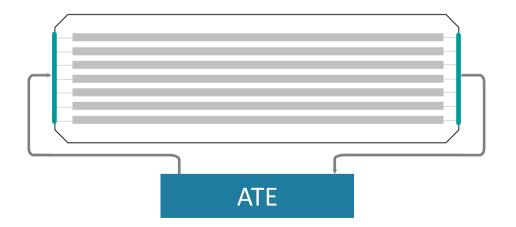

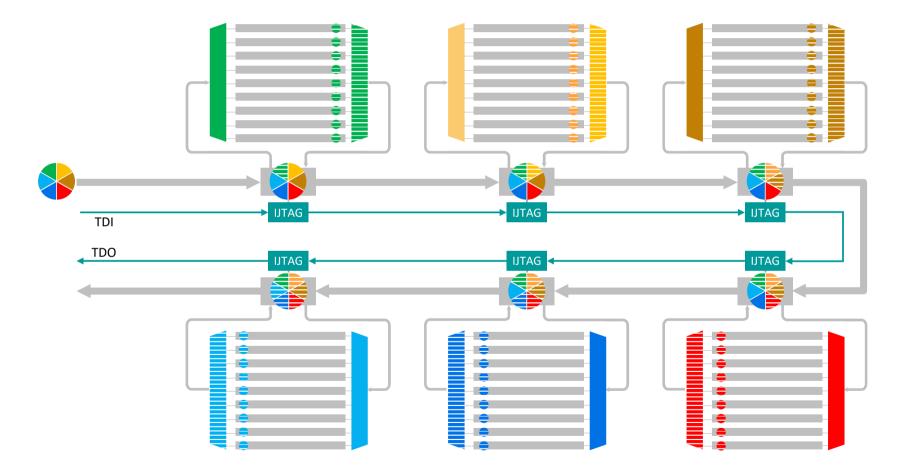

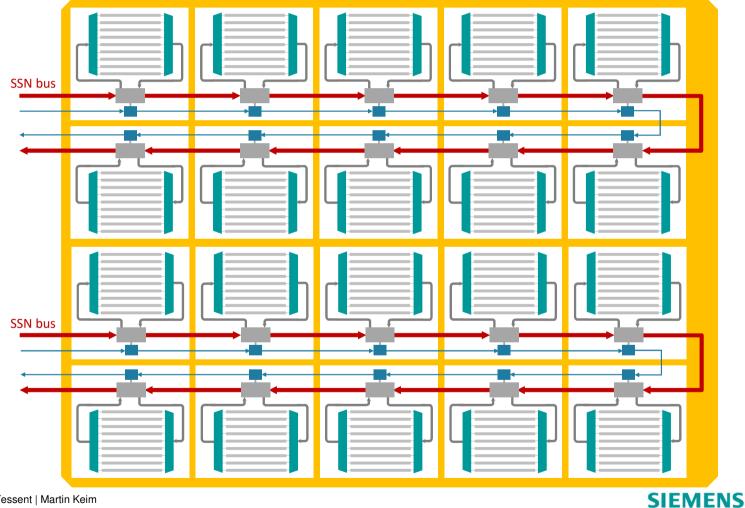

# Streaming Scan Network (SSN)

## **SoC-level DFT**

- Additional compression

- Identical cores

- Input-only streaming

- Reduced test time

- 400 MHz

- Simplified DFT implementation

- More balanced power

- Universal streamer

# **Packetized scan data distribution**

Page 20 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

# **Hierarchical DFT**

| → |  |  | T |

|---|--|--|---|

|   |  |  |   |

|   |  |  |   |

- Patterns for cores

- Retargeted to SoC level

- Formed into packets

- Allows change of SSN bus width after the fact

- Adjusts to available wafer

/ package resources

Page 21 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

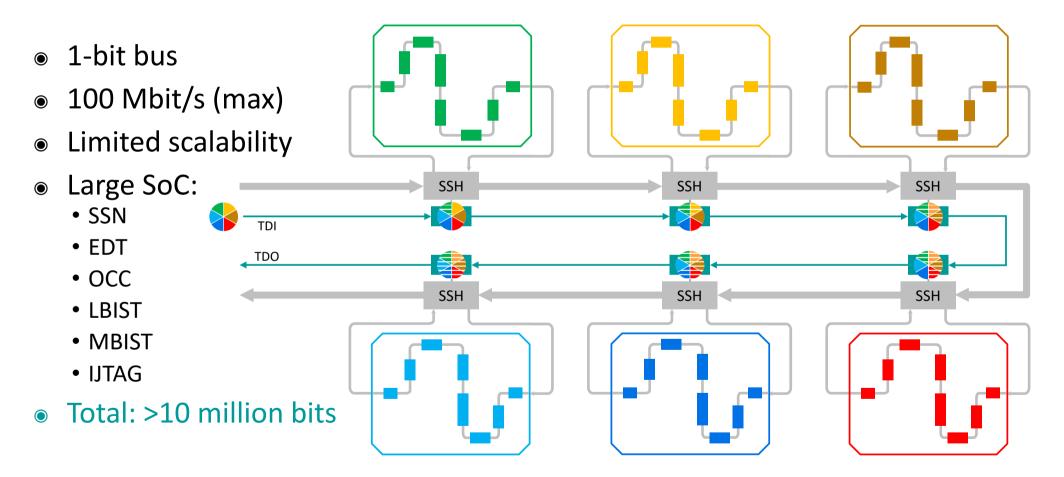

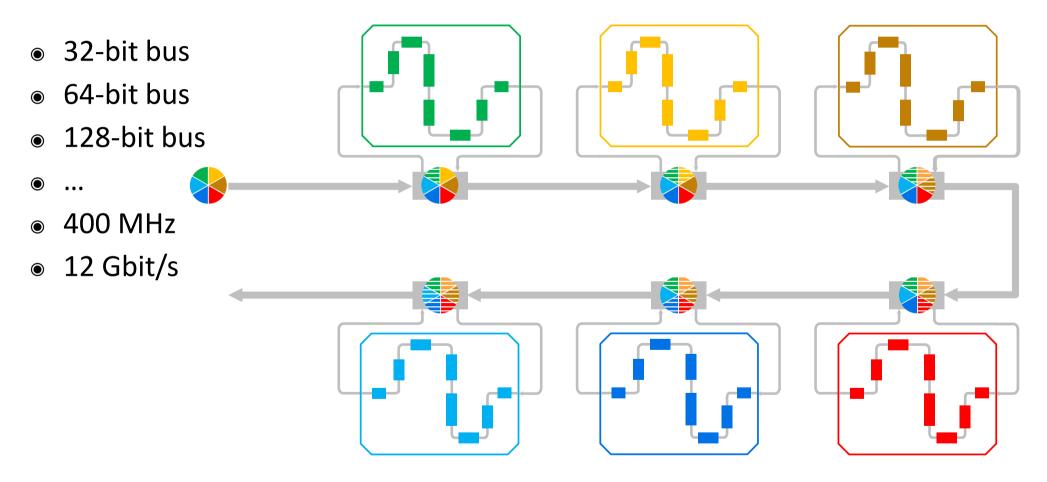

# Standard IJTAG

# High-bandwidth IJTAG

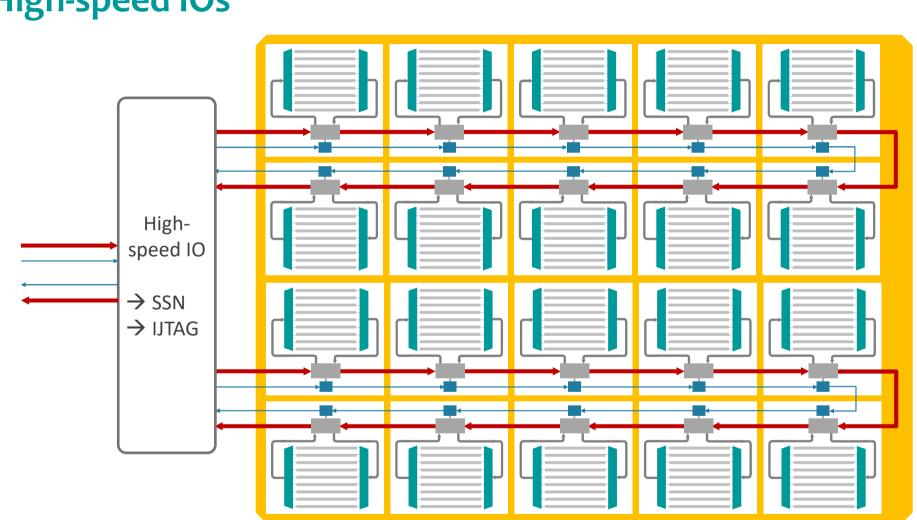

# High-speed IOs

Page 24 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

### **State-of-the-Art 2D DFT – What is important for 3D ?**

### 1. Test time

- Test delivery to die

- Test response off die

- Diagnosis volume data collection, logic and memory

#### 2. Test access

- Wafer-level die IO access is very narrow

- 3. Tool compute resources

- Inability to represent the entire die in memory

- Compute pattern once, map to die test access architecture

Narrow, high bandwidth interface at die IO

High bandwidth test distribution method on chip

Configurable for wafer / package

Full hierarchical test methodology

Page 25 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

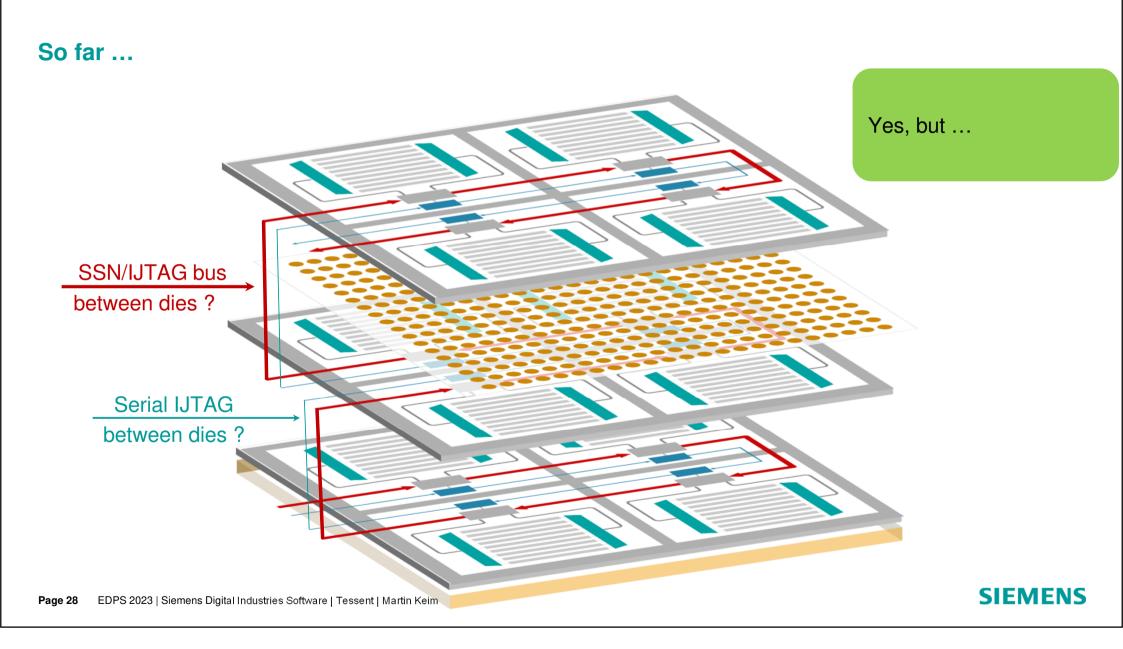

# Expanding 2D DFT into 3D

EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

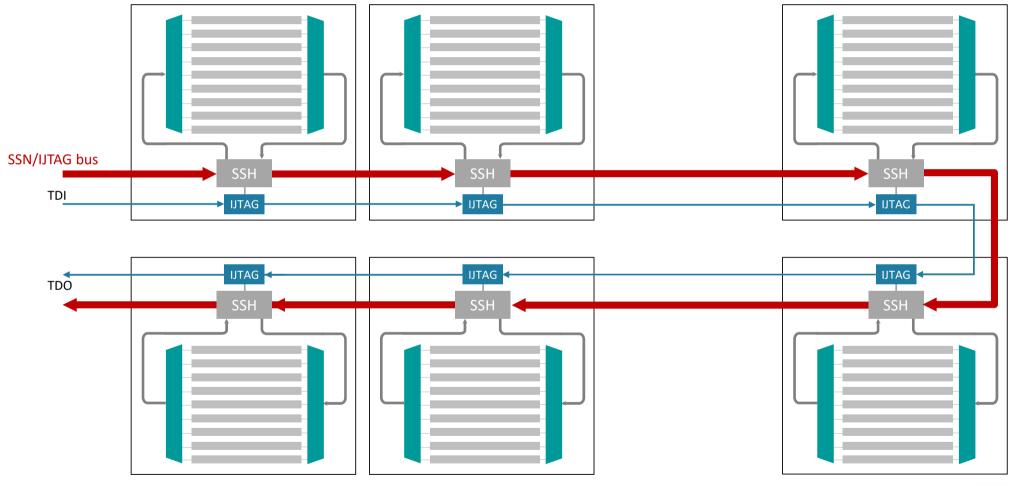

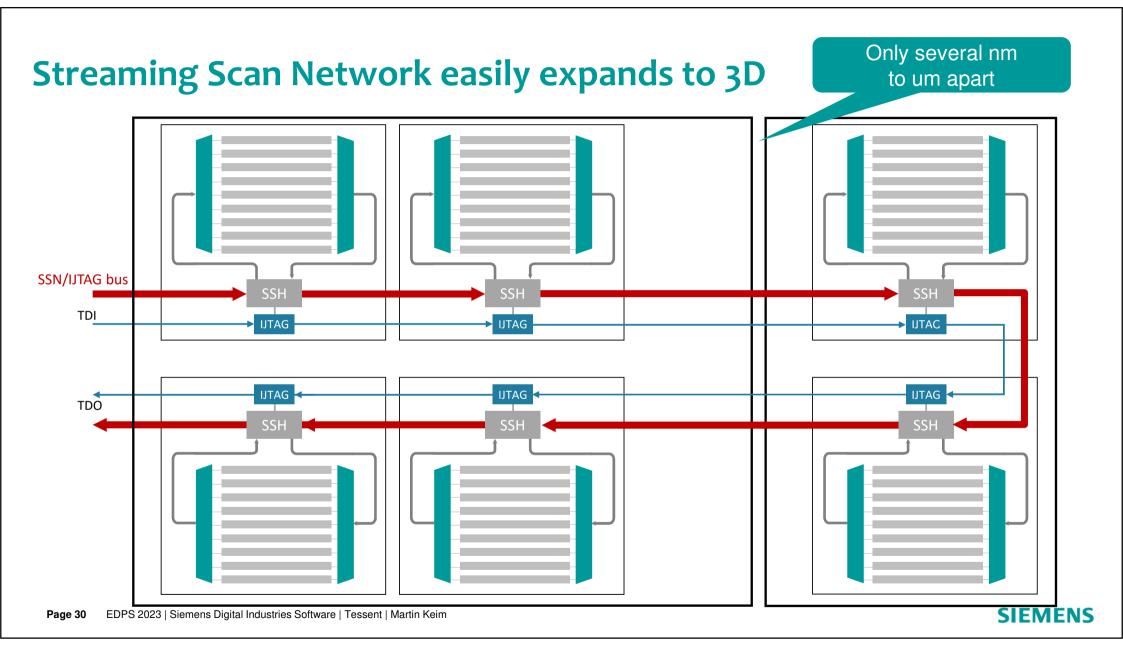

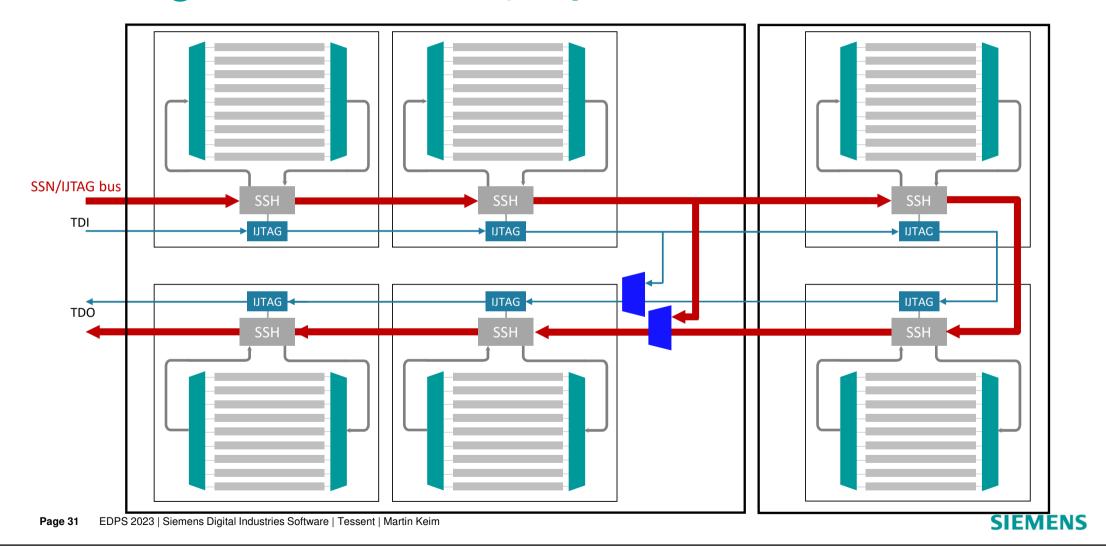

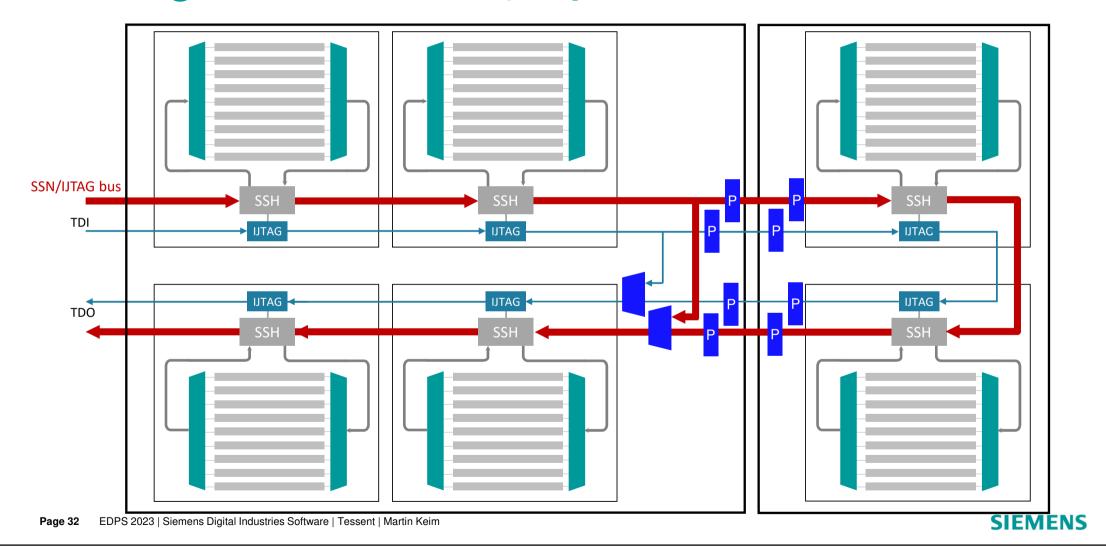

# **Streaming Scan Network easily expands to 3D**

Page 29 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

# **Streaming Scan Network easily expands to 3D**

# **Streaming Scan Network easily expands to 3D**

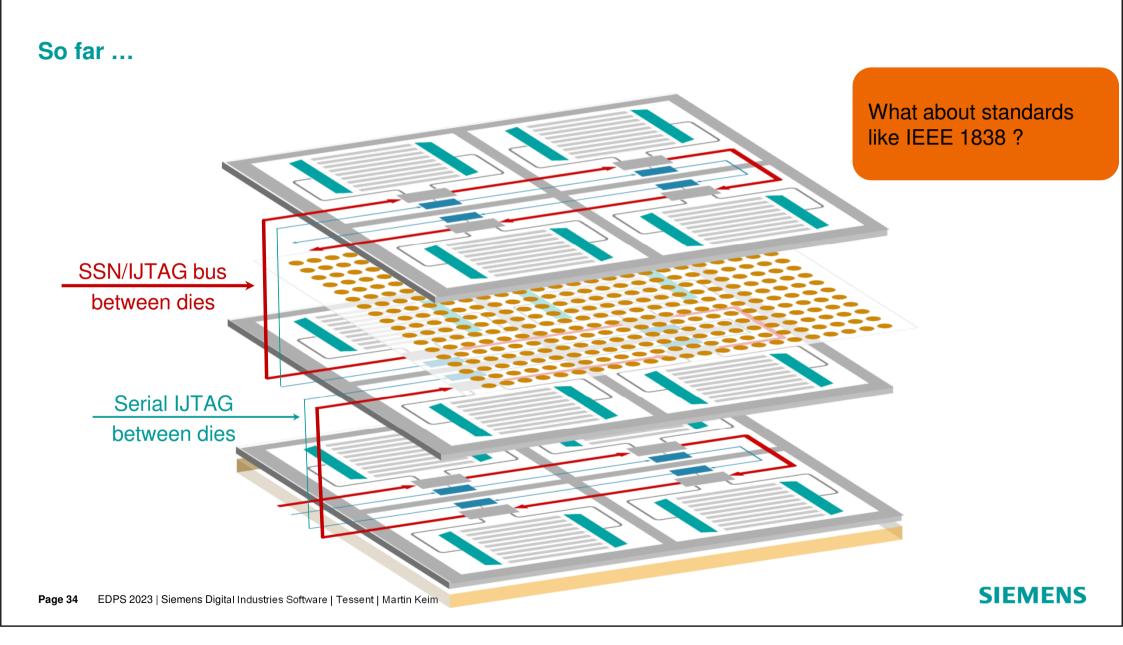

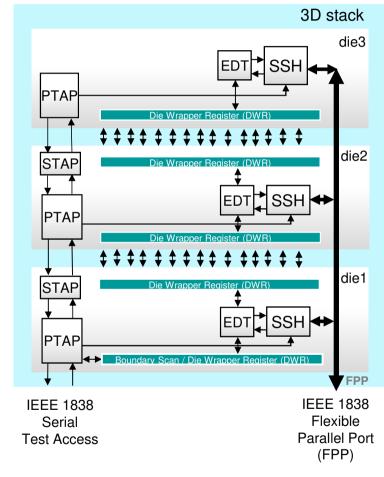

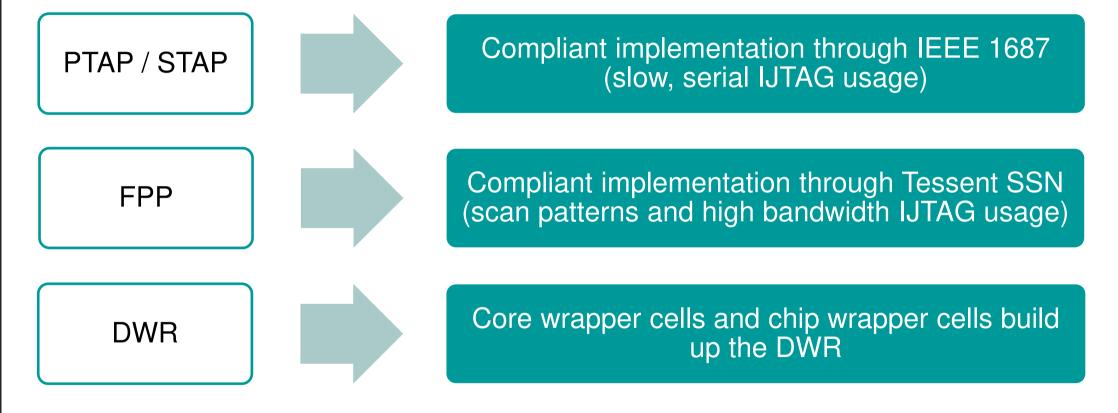

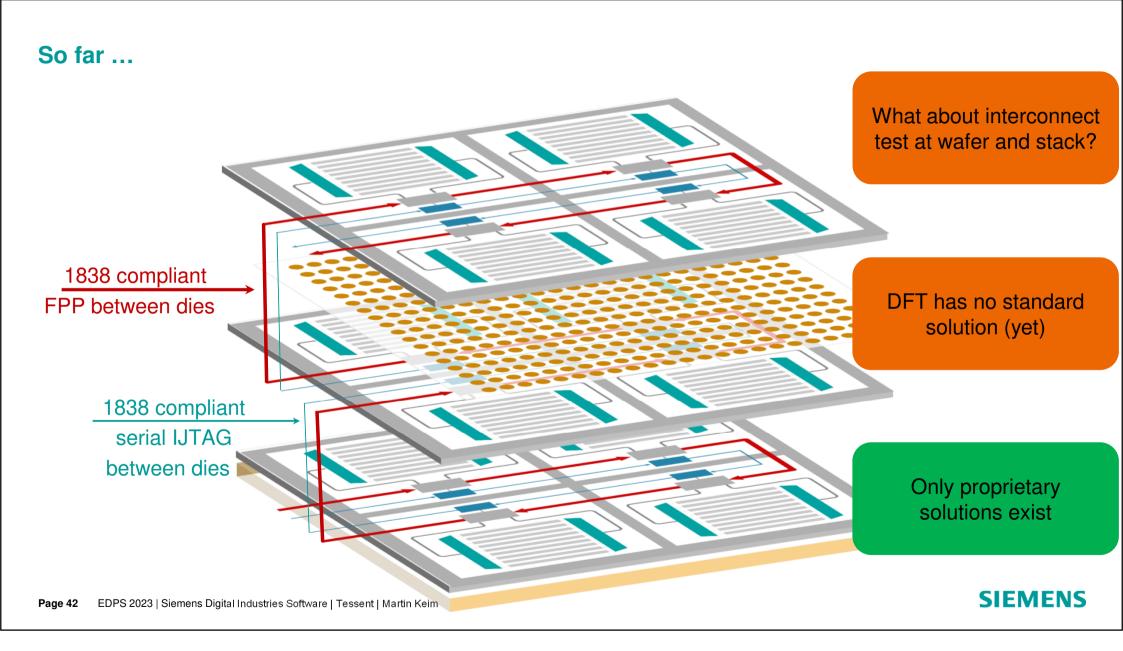

## **IEEE 1838 Standard**

Test access architecture for three-dimensional stacked integrated circuits

- Hardware and protocol for control and data signal transportation

- Required serial test access via PTAP / STAP

- Primary Test Access Port (PTAP) = 1149.1 TAP with 3D registers

- Secondary Test Access Port (STAP) = to connect to the next die

- One PTAP per die, one STAP per next die

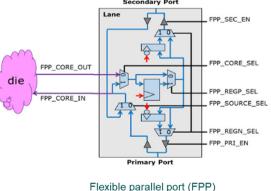

- Optional Flexible Parallel Port (FPP)

- Die Wrapper Register (DWR)

- Suggested usage die-to-die test

#### Page 35 Tessent Shell Multi-die flow for 3D Stacks | Restricted | © Siemens 2023 | Siemens Digital Industries Software

SIFMENS

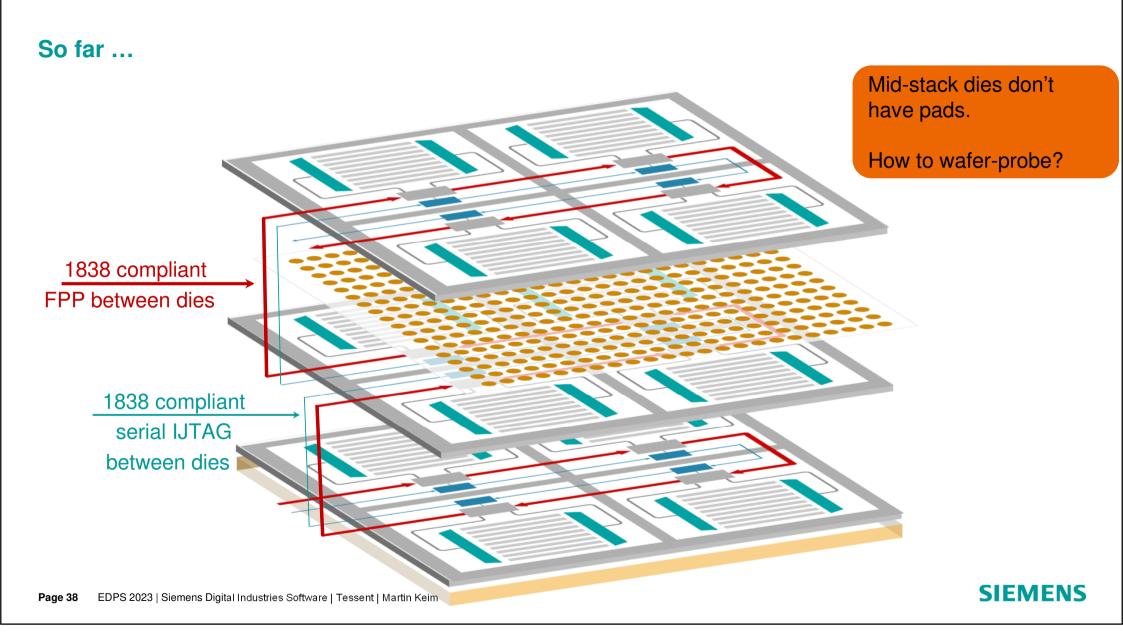

### Wafer probe: Muxed probe pads

Microbump probe is difficult due to fine microbump spacing

Additional "sacrificial" probe pads with standard bump pitch

- Test IO's, functional clocks, resets and sampling of power/ground for each supply

- Critical to have flexibility in number of test IOs (wafer vs. package)

- Without redo of the entire scan ATPG pattern generation

Probe Enable & multiplexer can automatically be added during DFT insertion

# Looking at test standards Actual and industry published

EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

#### **IEEE Test Standards**

1149.1-2001 / 2013 / 202x (JTAG) \*

- Base for serial access

- 2013 expands to embedded IP

1500-2005 / 2022

Embedded cores

#### 1687-2014 / 2024 (?) (IJTAG) \*

- Embedded IP

- Defines pattern (PDL) and hardware (ICL) description languages

- Retargeting through design hierarchy

#### 1838-2019

- 3D assembly

- No test

- No information transfer language

#### P3405

Die-to-die test & repair

#### P1838a

Boundary Scan for Multi-Die devices

#### Industry making standards

Industry is filling in the gaps

- Design methodology

- Data exchange

- Die-to-die test, repair

Example: TSMC published their "3DBlox"

#### Many, many interface standards

2.5D standards are emerging like UCle

Most use a PHY with tests like:

- IP-specific tests, PLL/DLL tests

- DFT, scan, memory BIST, boundary scan

Many support 1000's of IO's between dies

- · IO BIST with hard/soft lane redundancy

- Use of "spare" lanes

UCle – Universal Chiplet Interconnect Express

OpenHBI – Open High Bandwidth Interconnect

BoW – Bunch-of-Wires

HBM – High-Bandwidth Memory

USR/XSR Serdes – Ultra Short Reach / Extra Short Reach Serdes

\*: IEEE Standard currently under revision

Page 46 EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim

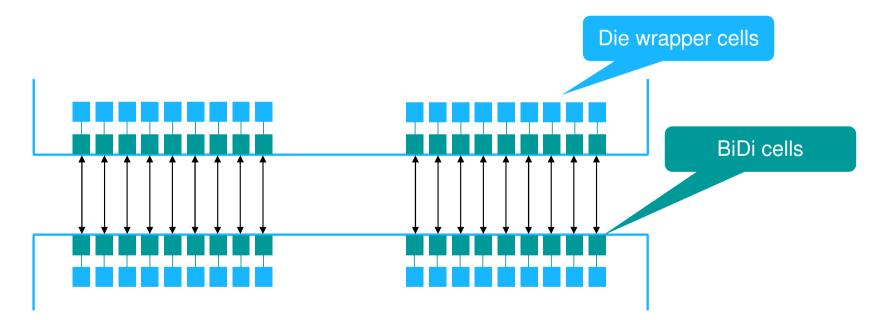

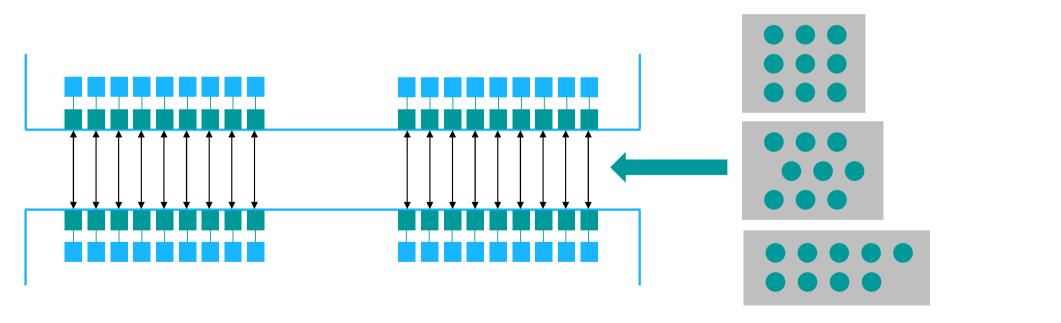

### 3D direct die-to-die interconnect & test

Bidirectional connection for (most) interconnects

- Allows wafer-level (short) loop-back test

- Allows stack-level short & long loop-back test

- Stuck-at, delay (shorts, opens)

### 3D direct die-to-die interconnect & test

Bidirectional connection for (most) interconnects

- Allows wafer-level (short) loop-back test

- Allows stack-level short & long loop-back test

- Stuck-at, delay (shorts, opens)

Test needs to know the topology (BIST, ATPG)

- Higher quality test

- Information for diagnosis

- Information for repair

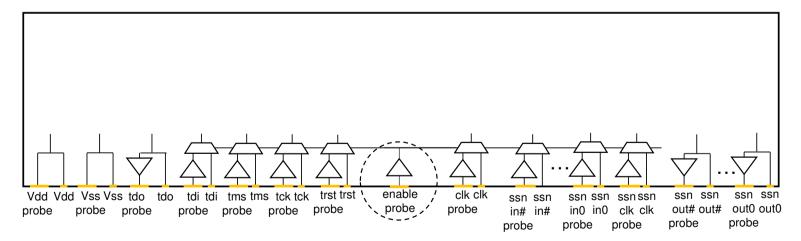

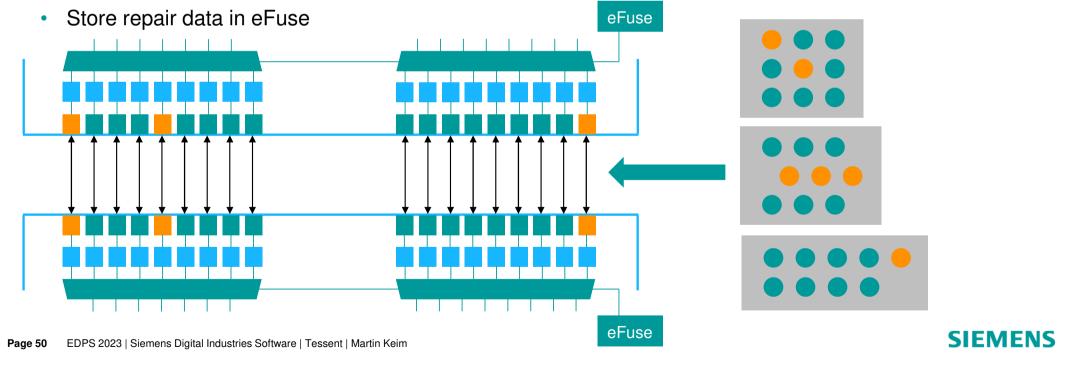

### 3D direct die-to-die interconnect & repair (IEEE P3405)

### Repair of (TSV) interconnect

- Assume some (TSV) interconnects are broken

- Deploy "some" spare interconnects

- Implementation similar to Memory IO repair

- For 2D TSV array, same solution on both sides

### IEEE P3405: Information exchange files

- How many spares per TSV group?

- Assignment of spare to TSV within a group?

- Ensure compatible repair for both dies

## Summary of Design-for-Test for 3D

Ensure the assembled product is defect free

- Each 2D die (chiplet, tile, ...) is defect free

- The 3D stack, 2.5D assembly is defect free

Cost considerations and trade-offs

- Known Good Die (KGD)

- Wafer-level die interconnect test

- Partial stack test

- Stack-level interconnect test

- Stack-level interconnect repair

- Reuse die-level DFT as much as possible for stack-level

- Hardware and test patterns

- Allow heterogenous 3D integration also for DFT

No support from standards

# Thank you

SIEMENS

EDPS 2023 | Siemens Digital Industries Software | Tessent | Martin Keim