# Si2: Value and Velocity with You

Robert Aslett

CEO Silicon Integration Initiative (Si2)

https://si2.org

Electronic Design Process Symposium

Oct. 5 Sunnyvale CA.

# or.. Planes, Trains and Automobiles

# Outline

# "I am he as you are he as you are me And we are all together"

- I am the Walrus by John Lennon / Paul McCartney

### Prologue ... in other words

# Si2 is us

When industry-wide collaboration is needed, the Si2 community provides the means to deliver more value to its members than they can achieve alone.

# Key Messages

- Si2's vision is to apply its purpose to the entire scope of semiconductor design.

- Our ideal state is when we deliver the greatest value, when it is needed, and then increase it through virtuous cycles of value creation (VC)<sup>2</sup>.

- The relative success of OpenAccess and Compact Model Coalitions have not been replicated. The reason for this is our velocity lags that of the industry.

- We must rethink our approach, so critical programs covering UPM, 3D multi-die, processed data, AI/ML, data mgmt. and other opportunities deliver value sooner.

- Our strategy is evolving but there are three things we should do now: 1) deepen member engagement; 2) shorten learning cycles, and 3) harmonize our roadmaps.

Provide collaborative technology and services which enable advanced semiconductor design integration, leading to industry-accepted standards.

Offer these standards, technology, and services to all interested organizations and individuals at a fair and reasonable cost.

# Si2 is driven by its members

Not shown: the Si2 Board of Directors and the Technology Steering Group

# **TITAN** Roadmap, SIG and WG Oversight

### SIGs

- Socialize the topic

- Narrow the area of focus

- Publish results

### **OpenStandards WGs**

- Define the initial standard

- Build a protype implementation

- Conduct POCs on practical problems

### Coalitions

Improve while ensuring compatibility

- Innovate on top of the standard

- Redistribution rights

# Vision: Address the growing scope of semiconductor design

many to many: interoperability is critical

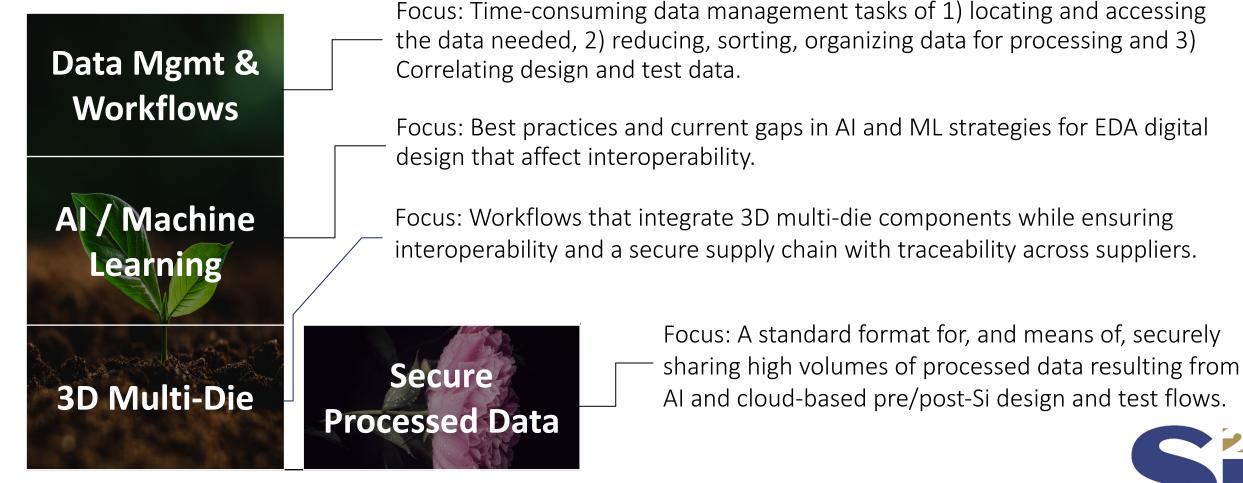

# Current SIGs and OpenStandards Working Groups

OpenStandards WGs

SIGs

# **Current Coalitions**

A collaborative environment based on an extensible reference API that defines classes and member functions to create, access & manage design databases throughout the design process.

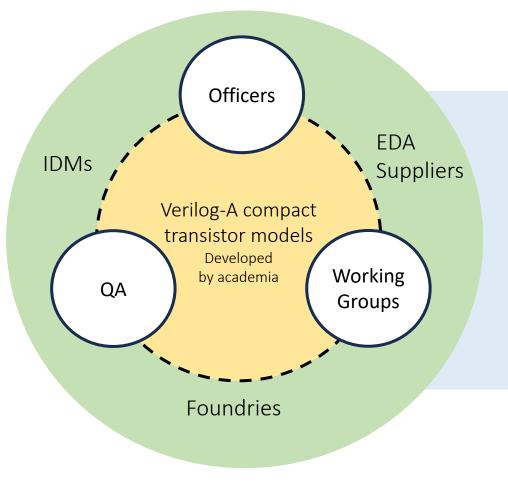

A collaborative environment focused on selecting, standardizing and then developing Verilog-A descriptions of standard SPICE device models and useful APIs.

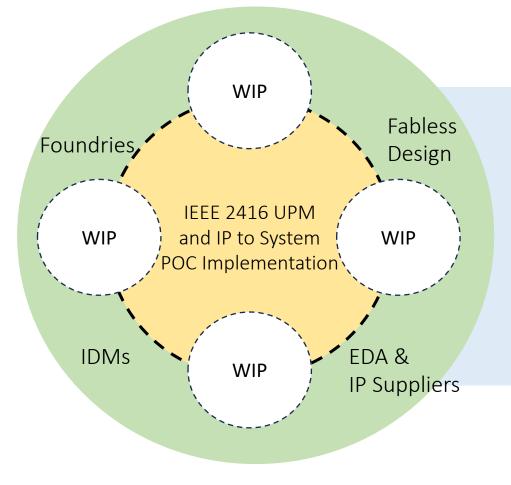

*Forming:* A collaborative environment focused on helping member companies benefit from the UPM/IEEE-2416 power standard by integrating the standard into their workflows via development of IP-to-system power models, tools & methods.

### Si2 Ideal State

# Deliver the greatest value, when it is needed, and then increase it through virtuous cycles of value creation

#### Value

Results have value if they contribute to Si2's purpose in a way that members will pay Note: Members pay with their time, technology contributions and dues

Virtuous Cycles of Value Creation (VC)<sup>2</sup>

Collaboration cycles that build on previous results and deliver increasing value.

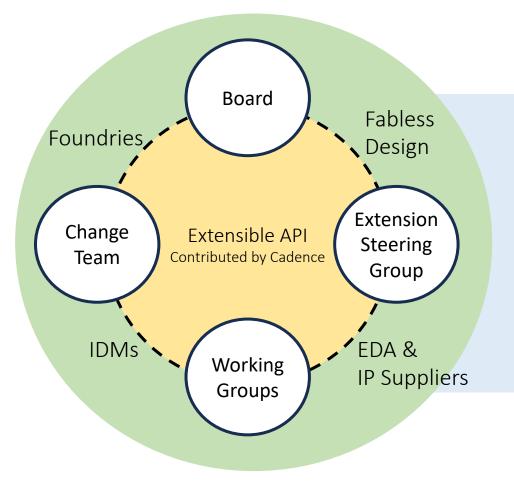

# OAC: An example of Virtuous Cycles of Value Creation

A collaborative environment based on an extensible API; supported by Si2 staff

#### 47 corporate members; 20+ years of innovation

- Continuous development of extensions in a way that assures compatibility with related applications.

- Rapid prototyping and innovation on top of the trusted industry standard

- Set development priorities for the reference implementation

- Redistribution rights for executables developed using SW developed by Si2 staff and contributed by members.

# OAC: A sampling of extensions

Source: James Masters & Benjamin Hoefer (Intel) - Si2 OA Workshop (9/28/2023)

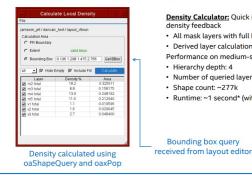

#### Density Calculator

#### oaScript + oaxPop : Density Calculator

| All mask layers with full hierarchy depth suppo                     | rted  |

|---------------------------------------------------------------------|-------|

| B in the second state with the first state                          |       |

| <ul> <li>Derived layer calculations available (not shown</li> </ul> | here) |

| Performance on medium-size block                                    |       |

| Hierarchy depth: 4                                                  |       |

| <ul> <li>Number of queried layers: 19</li> </ul>                    |       |

| <ul> <li>Shape count: ~277k</li> </ul>                              |       |

| <ul> <li>Runtime: ~1 second* (with C++ helper class)</li> </ul>     |       |

#### Node Highlighting

#### oaxPop: Node Highlighting

#### **Block Signal Extraction**

#### oaxPop : Block Signal Extraction

#### Layout Netlist Creation

Bounding box query

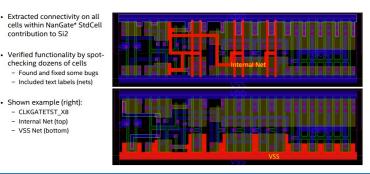

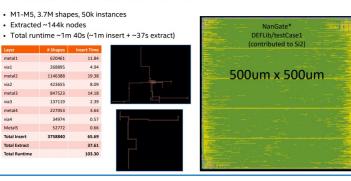

#### oaxPop: Layout netlist creation OA Design Objective: extract connectivity and create a SPICE\* layout netlist Application: Layout-versus-schematic (LVS) Code Profile:

- Python code, 335 lines total (w/comments) - YAML config - derived layers, connectivity, device formation and terminals

- Demonstrated on several NanGate\* standard cells, contributed to Si2

- Example will be included in oaxPop v2.0 release

YAML Config [contact, ngate, pgate]

: [contact]

: [contact]

[contact] devices: nmos: layer: ngate d: [ndiff\_sd, left] g: ngate s: [ndiff\_sd, right] w: width l: height layer: pgate rminals: d: [pdiff\_sd, left] g: pgate s: [pdiff\_sd, right] arameters: w: width l: height Note: for brevity the derived layers definitions in this YAML config are not shown here. Output .subckt AND2\_X1 A1 A2 ZN MNO VDD A1 \_\_NO pnos w=0.05 1=0.315 Mn1 \_\_NO A1 \_\_N1 mos w=0.05 1=0.21 Mn2 VSS \_\_N0 ZN mnos w=0.05 1=0.415 Mn3 VDD \_\_N0 ZN pnos w=0.05 1=0.63 Mn4 \_\_N1 A2 VSS nnos w=0.05 1=0.21

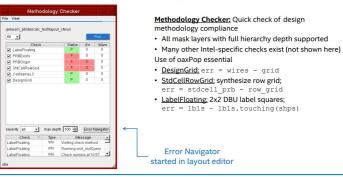

#### Methodology Checker

err = stdcell prb - row grid

Error Navigator

err = lbls - lbls.touching(shps)

#### oaScript + oaxPop : Methodology Checker

#### Color Shifting

#### oaxColor Overview

metal1

metal2

via1

via2

via3

metal4

- In 2012 Cadence authored a Data Model Specification for "Multi-Pattern Technology Support" document

- oaxColor WG has released an OpenAccess extension implementing an API to read/write coloring information according to the Cadence specification

- C++ reference implementation

- Scripting support with oaScript (python, ruby)

- Developed on top of the extension framework (oaxPop, oaxConn, etc)

- Goal: Standardize how OpenAccess users interact with MPT Coloring information in an accessible and extensible API.

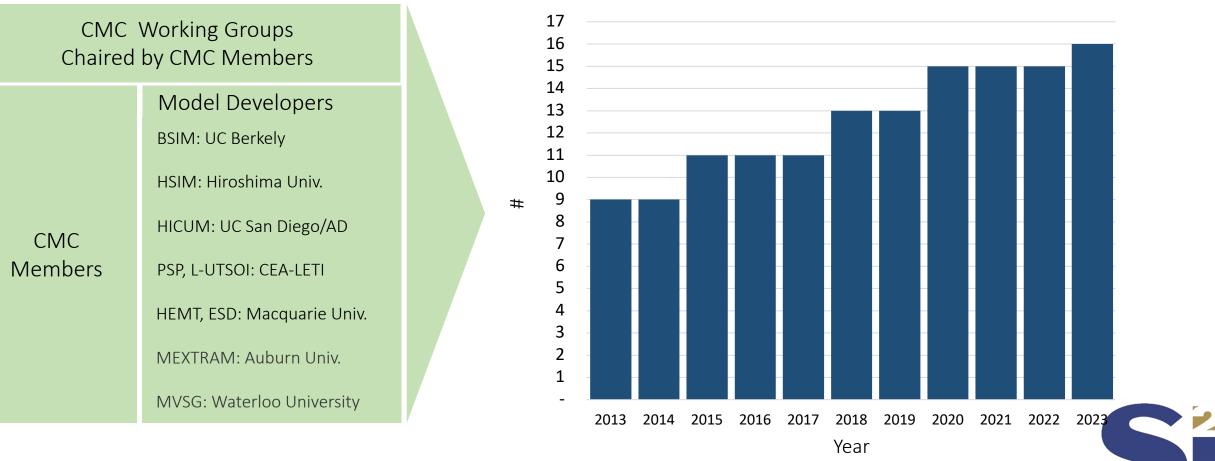

# CMC: An example of Virtuous Cycles of Value Creation

A collaborative environment based on compact model R&D; supported by Si2 staff

32 corporate members; 28 years of innovation

- Selection of standard models, APIs and related utilities.

- Alignment of R&D worklists with member priorities.

- Continuous refinement in a way that assures compatibility and accuracy with target applications (e.g., circuit simulators).

- Redistribution rights for executables developed using released Verilog-A descriptions.

# CMC: The growth of standard compact models

CMC Standard Models

However, we have not replicated this in other areas

# The primary issue is velocity, where:

# Velocity = $\Delta$ Value/ $\Delta$ time

measured from SIG or WG start to production usage by an engineer.

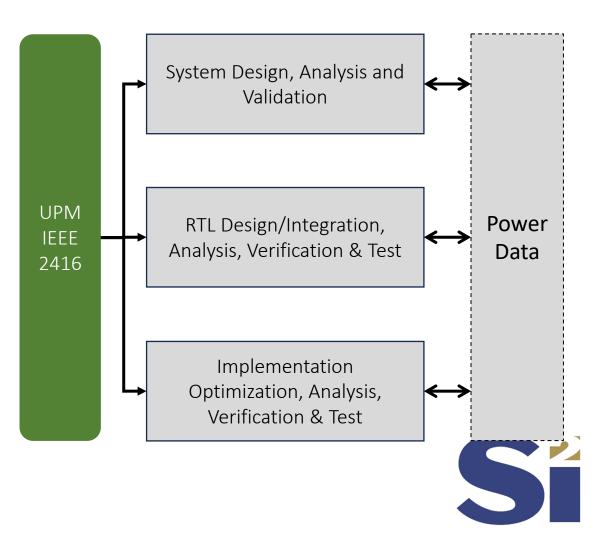

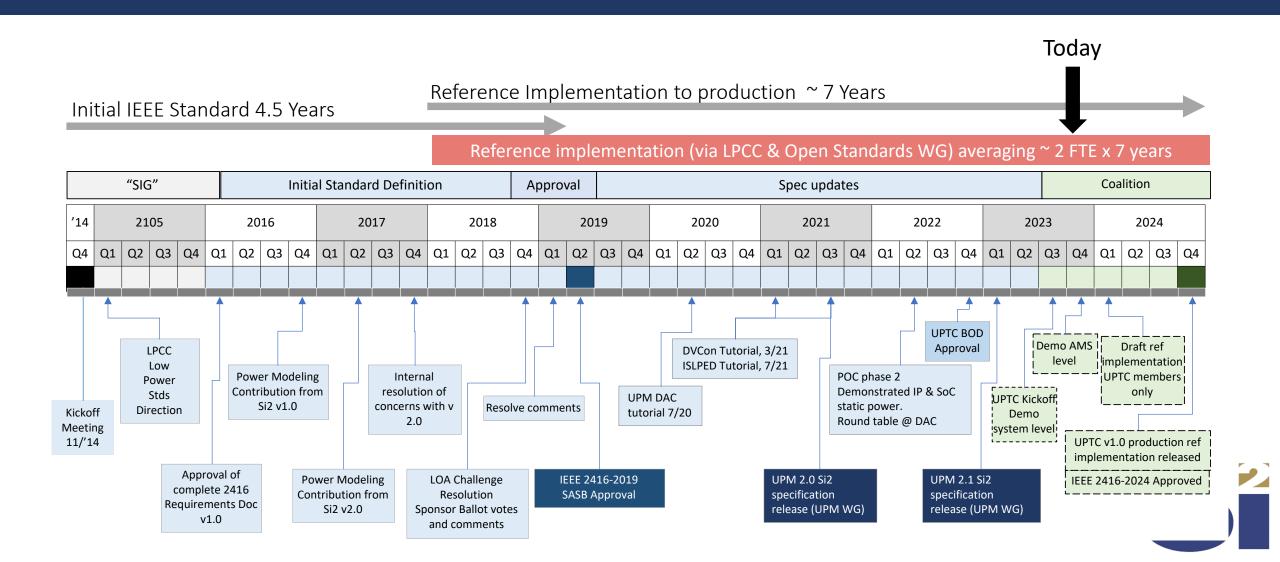

## Example: The Unified Power Model (UPM)

#### IEEE 2416-2019

" This standard describes a parameterized and abstracted power model enabling system, software, and hardware intellectual property (IP)-centric power analysis and optimization.

It defines concepts for the development of parameterized, accurate, efficient, and complete power models for systems and hardware IP blocks usable for system power analysis and optimization.

These concepts include, but are not limited to, process, voltage, and temperature (PVT) independence; power and thermal management interface; and workload and architecture parameterization. "

## Example: Unified Power Model (UPM)

#### IEEE 2416-2019

" This standard describes a parameterized and abstracted power model enabling system, software, and hardware intellectual property (IP)-centric power analysis and optimization.

It defines concepts for the development of parameterized, accurate, efficient, and complete power models for systems and hardware IP blocks usable for system power analysis and optimization.

These concepts include, but are not limited to, process, voltage, and temperature (PVT) independence power and thermal management interface; and workload and architecture parameterization. "

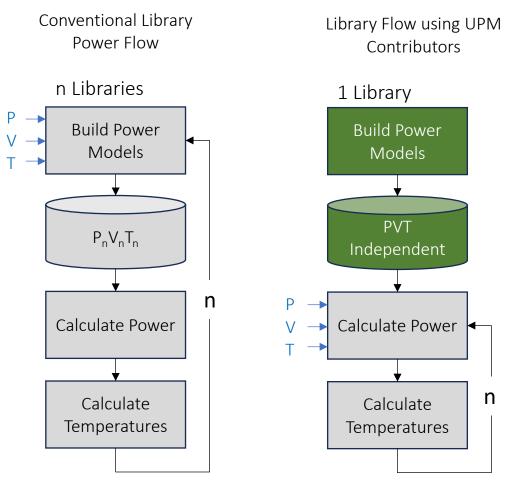

Long, slow, compute intensive

Short, fast, compute efficient

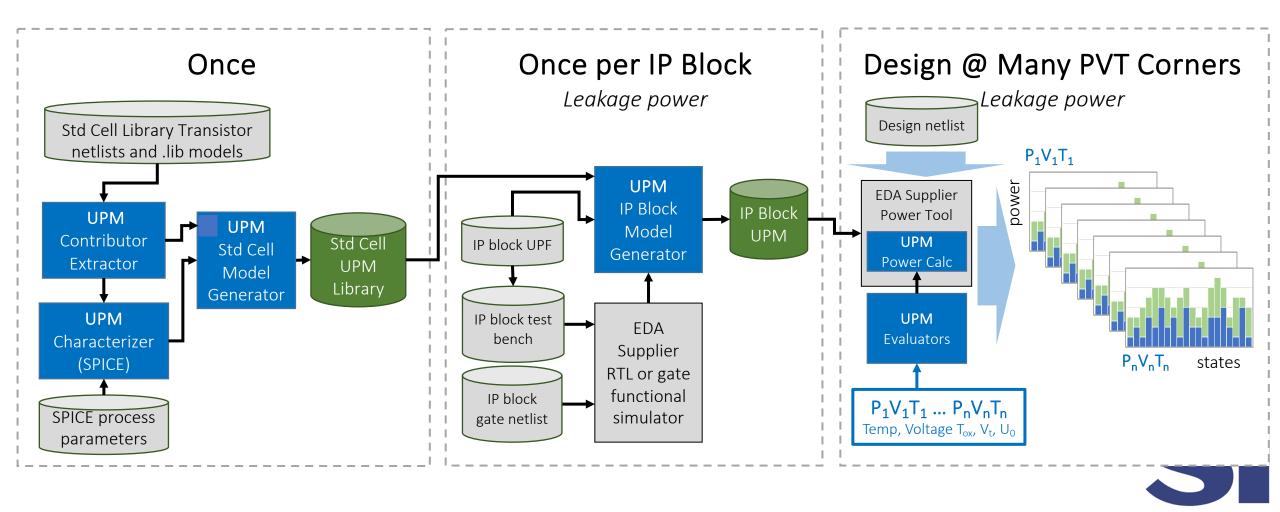

## Example: UPM for an IP Block

The UPM Model

**Existing Capabilities**

# The New Unified Power and Thermal Coalition

A collaborative environment based on IEEE 2416 UPM; facilitated by Si2 staff

5  $\rightarrow$  9 corporate members; just starting

- Prototyping and innovation on top of a trusted industry standard

- Continuous development of related technology in a way that assures compatibility

- Collective influence on development priorities of the reference POC implementation and related EDA tools

- Redistribution rights for executables & products developed using the software developed by Si2 and contributed by others

## Sounds good, but it took 9 years to get to this point.

## How do we increase our velocity?

We must rethink how we identify and co-develop new Si2 standards, related collateral and POCs.

While we have those conversations there are three things we should do now that will help....

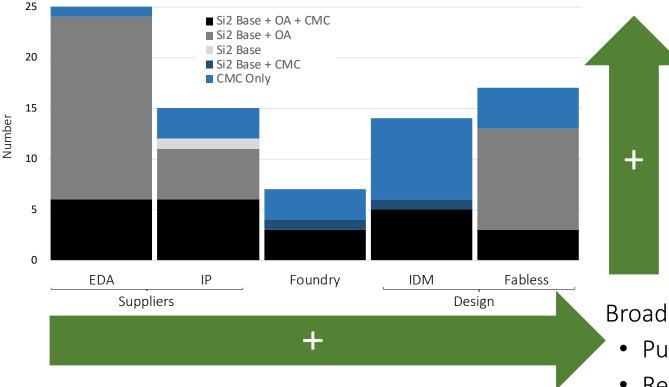

# 1. Broaden, deepen member engagement to obtain strong agreement on value – increase the numerator

#### 65 Current Si2 Corporate Members

Add missing members per segment and deepen participation from those already here by:

- Increasing collaboration return (value)

- Decreasing collaboration cost

- Factoring in opportunity cost

Broaden expertise represented in Si2 by:

- Pursuing new adjacencies (e.g., Assembly & Test, CSPs..)

- Re-invigorating academic memberships

- Engaging with relevant gov't programs

# 2. Shorten learning cycles to get to the best implementation sooner – reduce the denominator

#### Special Interest Groups

- Socialize, hypothesize, publish

- Report out to TITAN on a regular cadence for re-commitment

#### **OpenStandards Working Groups**

- Apply "Look, Ask, Model, Discuss, Act (LAMDA)" for rapid POCs

- Release min. viable features/POCs on a set cadence for early, frequent feedback

- Hire and apply Si2 funded engineers or contractors at critical points

#### Coalitions

- Invest in systems to enable continuous integration of member contributed code

- Employ systems/processes to collect usage information for continuous improvement

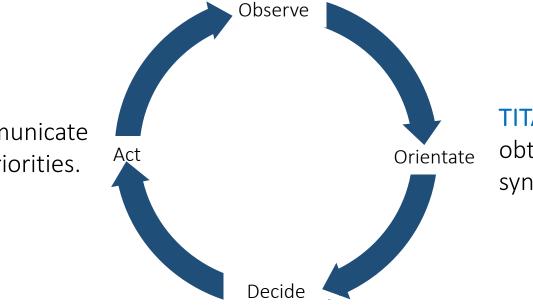

# 3. Harmonize our roadmaps to avoid strategic dissonance on the question of value

**TITAN:** Discover relevant induced or autonomous changes to the current state of public member roadmaps and priorities via conversations with Si2 members

**Si2 Staff:** Publish and communicate revised Si2 roadmap and priorities.

**TITAN:** Analyze the information obtained through observation and synthesize into a recommendation.

**Si2 BOD:** Provide feedback on relative value/priority of recommendations. Make decision.

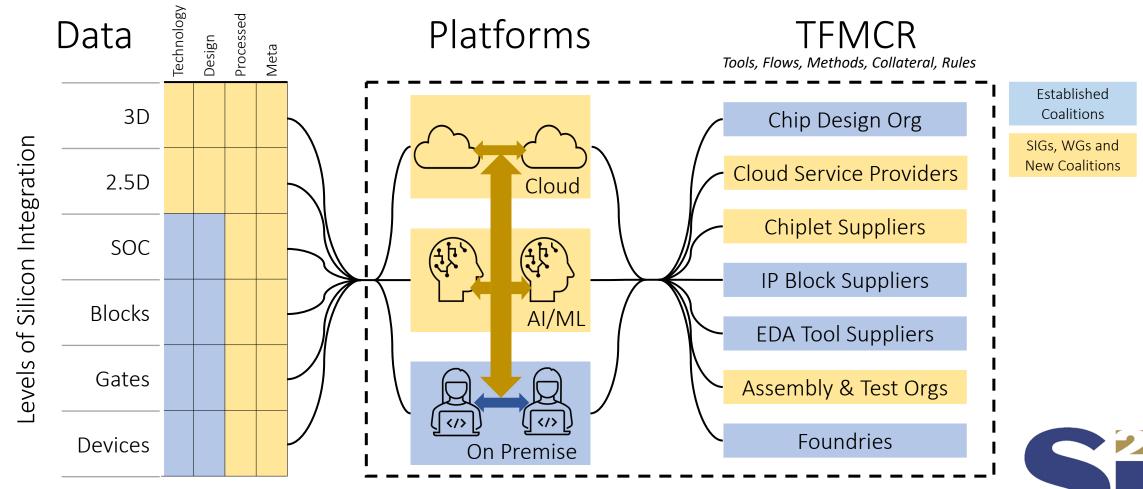

# Si2 Strategy 1.1 (2.0 will be in Q1 2024)

- Intercept new levels of integration (3D), pre-post Si data management (DMW), processed data (SPEED), and new design platforms (AI/ML).

- Increase velocity by investing in the means to broaden/deepen member engagement, shorten learning cycles, and a harmonize roadmaps.

- Make UPTC the next (VC)<sup>2</sup>. Follow the lead of our members and invest in the engineering resources needed to succeed.

- Continuously extend and innovate on top of OAC and CMC standards and technology. Use them to help solve interoperability issues in adjacent areas.

# "I am he as you are he as you are me And we are all together"

- I am the Walrus by John Lennon / Paul McCartney

# Hop on the bus. If you are not a member of Si2, you should be.

Source: Adobe Stock