# Passage—A Wafer-Scale, Programmable Photonic Communication Substrate

Steve Klinger, VP Product Lightmatter

TEAM

2 OFFICES

**Boston**

### **Investors**

GV (Google Ventures) Mountain View

Spark Capital

Matrix Partners

Viking Global

Hewlett-Packard Enterprise

Massachusetts Institute of Technology

Stanford University

3 PRODUCZS

Envise

### Passage

Idiom

105 EMPZOYEES

Nicholas Harris, PhD Founder, CEO

Thomas Graham Founder, Biz/Ops

Ritesh Jain VP, System Engineering

Steve Klinger VP. Product

Jessie Zhang VP, Finance

Darius Bunandar, PhD Founder, Chief Scientist

Richard Ho, PhD VP, HW Engineering

Ayon Basumallik, PhD VP. SW Engineering

Aravind Kalaiah, PhD Director, ML Science

Bob Turner VP, Sales

## 115 PATENTS

| - L      |                | 110-         | DÇ.           | 東京         | (東)<br>(東)<br>(東) | **         | 事業                 |

|----------|----------------|--------------|---------------|------------|-------------------|------------|--------------------|

|          | 16             | 166)<br>166) |               |            | ¥                 |            | ,<br>primiti       |

| Ö        | -@F            |              |               |            | 5995<br>5995      | Glight     |                    |

| -        | -              | -            | -             | Ų.         | يَّةً اليَّة      |            |                    |

| e fre    | DATE:          |              | TULU.         | \<br>\\-   |                   | (JE        |                    |

| 900 P    | # # #<br># # # |              |               |            |                   |            |                    |

| =(#)=    |                | PPF          | PPP           | paran.     | \$ <del> </del>   |            |                    |

| 198      | -0.384         |              |               |            |                   | - <u>-</u> | [17]<br>101<br>101 |

| - (Webs) |                | -56          |               |            |                   |            |                    |

| 財施       | býk            | - 12         | Zij-          |            | -                 | -          | <u></u>            |

| A.A.     |                | 7            | ii.           |            | Mi.               | <u> </u>   | Ħ.                 |

|          |                | Ţ            | U             | <b>W</b> . |                   | -21114     | 188                |

|          | -4-            | -44          | <del>**</del> | 11         | ÷                 | 24         | <u> </u>           |

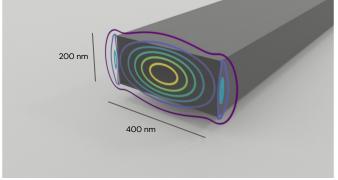

# Let's talk about silicon photonics.

### 300mm CMOS Fab

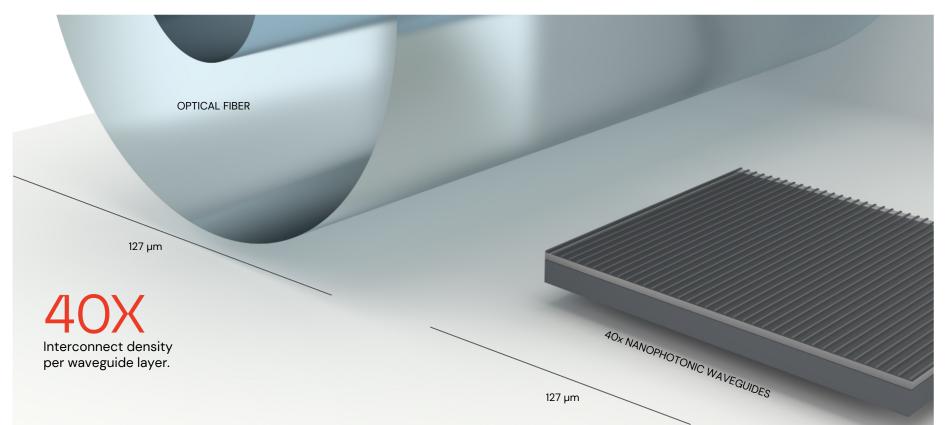

### A Sense of Scale

Optical fibers versus nanophotonic waveguides

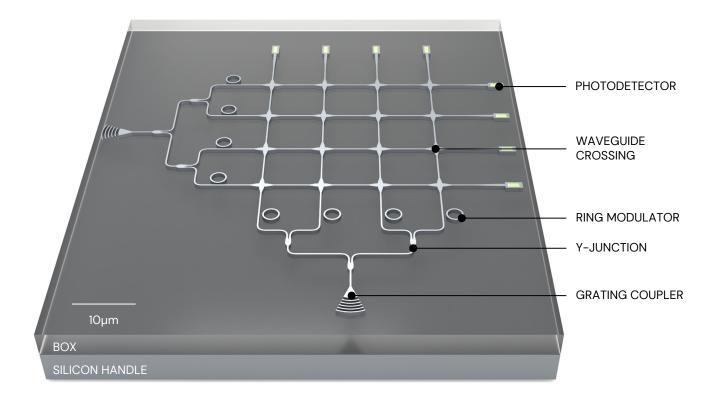

### What does silicon photonics look like?

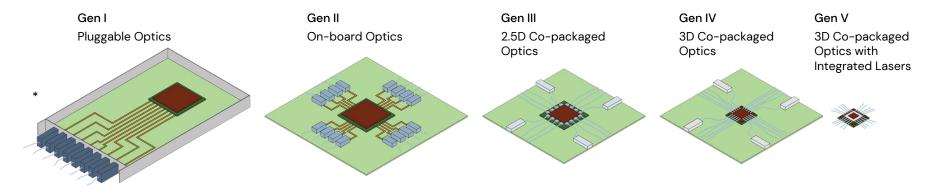

### Enabling new communications technologies

Closer and closer to the chip

### Why bring optics closer to the SoC?

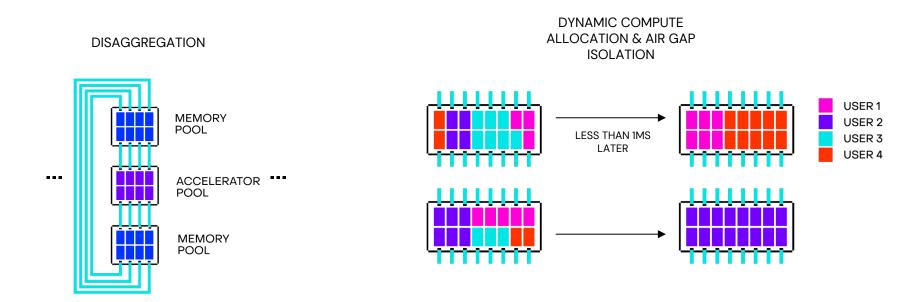

- Disaggregation

- Data closer to compute

- PCB trace losses too high for long, high-speed links

- SoC die sizes max'd out, can't accomodate large #'s of LR SerDes

- Reduction in interconnect power

- Increased bandwidth over pluggables

- Higher bandwidth density at die edge

- Bypass intermediate stages (PCIe)

<sup>\*</sup>Used with permission from Dr. John Bowers and adapted from an article in Applied Physics Letters (2021)

# Challenges at chip and system level with co-packaged optics.

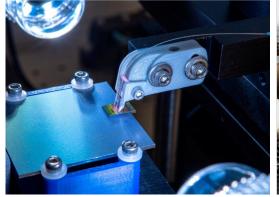

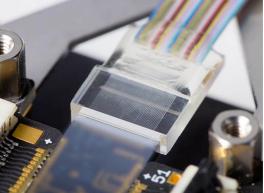

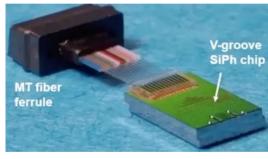

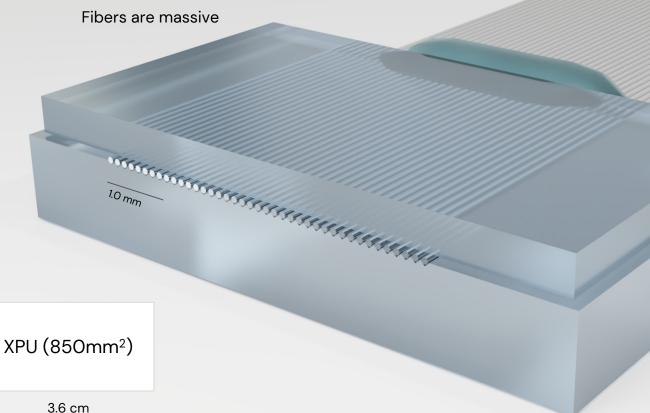

### Optical Fiber Attach

Expensive, low throughput

2.4 cm

### Optical Fiber Beachfront Density

Max Fiber Count

200

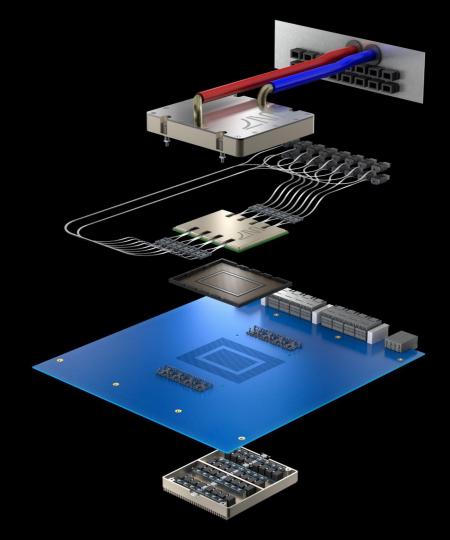

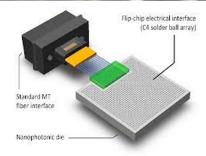

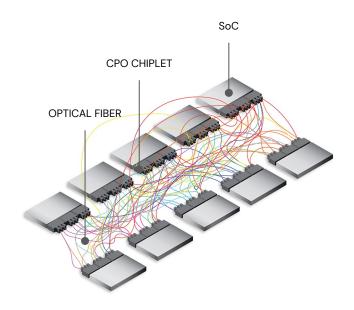

### Chiplets and Co-packaged Optics

Scaling challenges

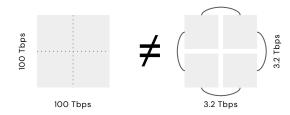

#### CHIPLET BISECTION BANDWIDTH

Beachfront and bandwidth are fundamentally linked in chiplet processors. Big chips are at odds with high yield.

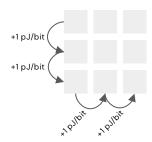

### MORE HOPS, MORE ENERGY

Each chiplet hop adds to communications energy consumption. Building large chiplet arrays this way will incur significant energy costs.

### CHIPLET XPU & CPO

- Fibers have low beachfront density

- More wavelengths, more BW

- Static interconnect

### System Level

Serviceability, manufacturability, yield

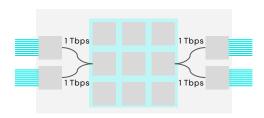

CO-PACKAGED OPTICS ALL-ALL

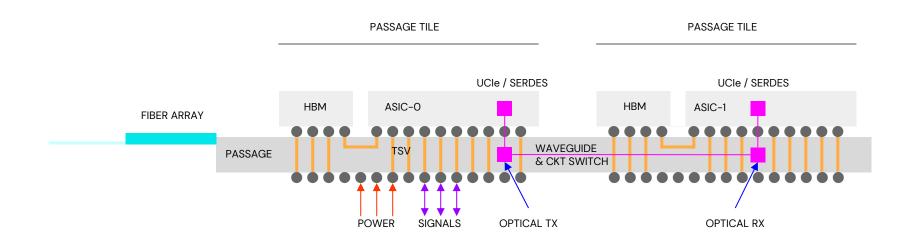

### PASSAGE™

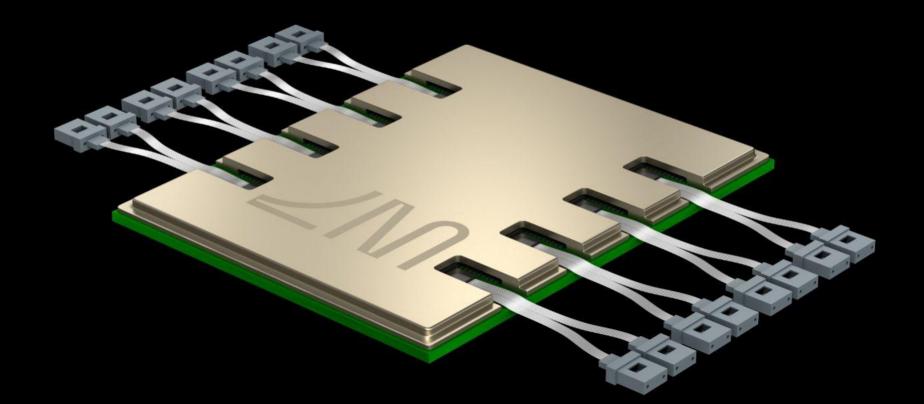

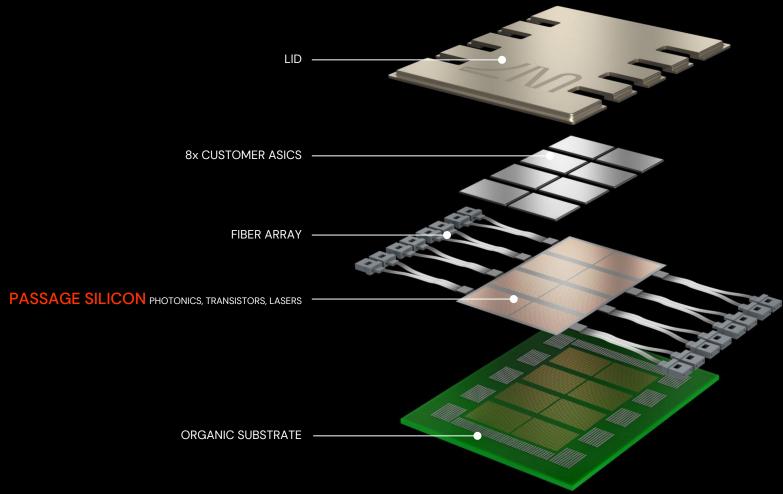

### Passage™

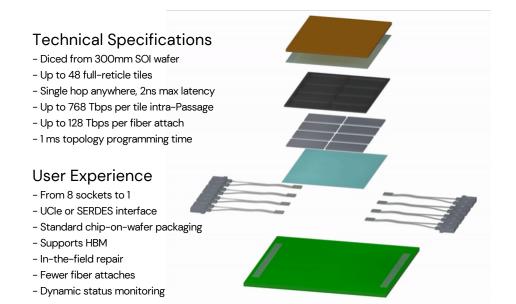

### At a high level

PHOTONIC WAVEGUIDES

40x

3um PITCH

Uniform architecture allows flexible dicing based upon end application

Directly compatible with SERDES PHYs and targeting UCle support 2023.

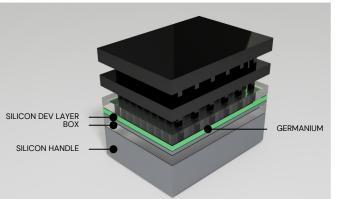

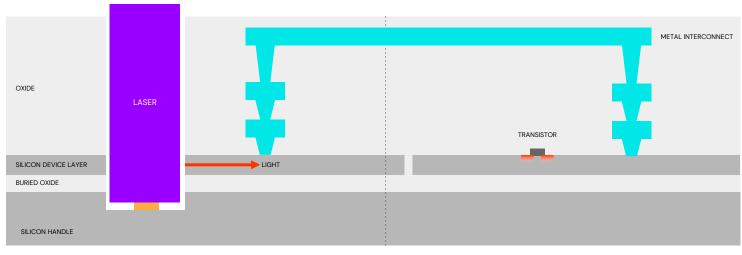

### **Cross Section**

Chip-on-wafer Packaging

### What Makes It Possible

(Stitching Waveguides and Metal) + (Lasers and Transistors)

RETICLE BOUNDARY

### What Makes It Possible

**Optical Circuit Switching**

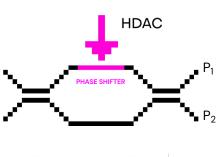

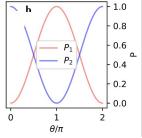

### MACH-ZEHNDER INTERFEROMETER

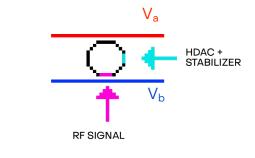

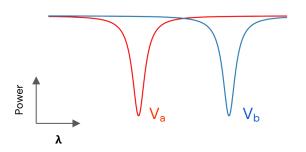

### **RING RESONATOR**

### What Does Switching Look Like?

NIR Microscopy of an array of optical circuit switch elements

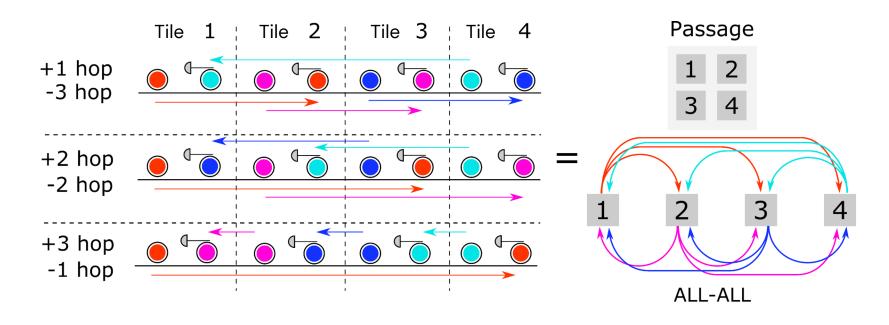

### Dynamic Topologies

All-All

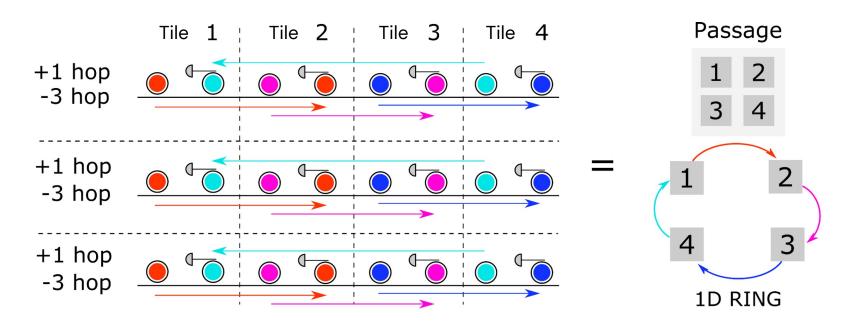

### Dynamic Topologies

1-D Ring

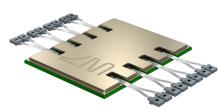

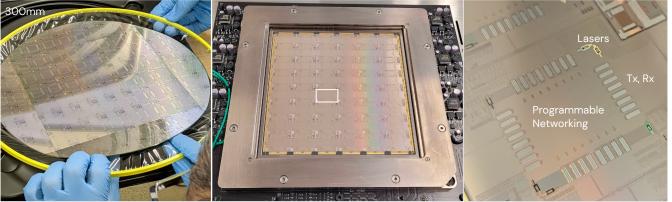

### First Silicon Success

The world's first photonic wafer-scale interconnect

### Passage™ Alpha Silicon

- <50 Watts

- 32 channels per site, 1.024 Tbps

- 32 Gbps per channel NRZ

- 48 x 800mm<sup>2</sup> tiles

- 288x 50 mW Lasers

- 6.144 DACs

- 6,144 MZIs

- 150,000 photonic components

- JTAG interface

- Integrated Lasers, transistors, photonics

- Programmable interconnect topologies

Photonic waveguides with ~4 µm pitch.

### Solutions LM is Driving

A variety of applications

# THANK YOU