#### Outline

#### **Market Trends**

Multi-Die Design Challenges

The EDA Solution Driving Innovation

Summary

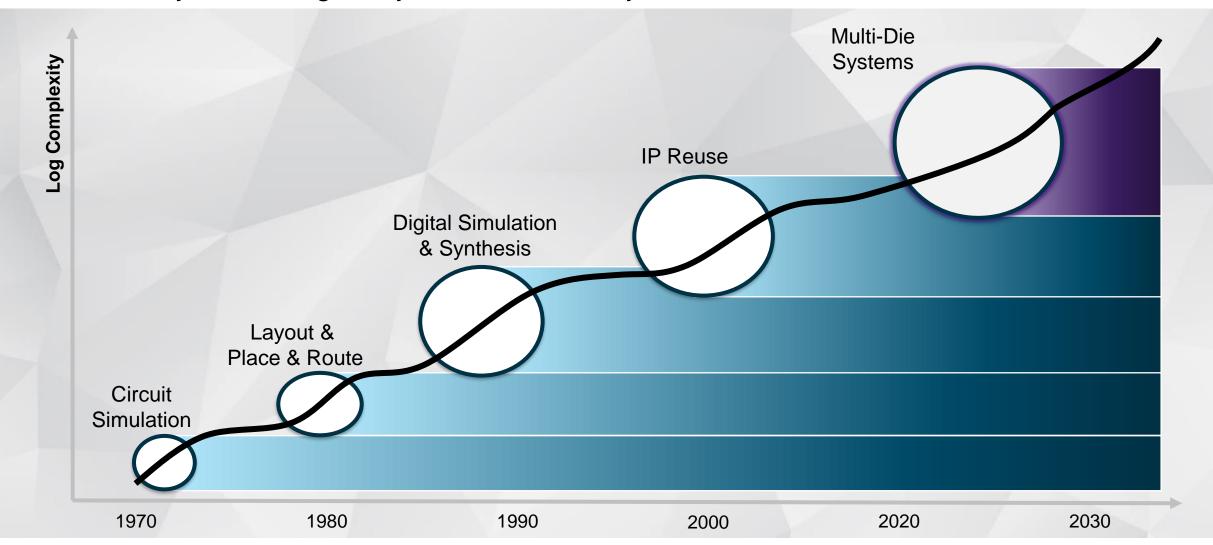

## Semiconductor Design Productivity Waves

Multi-die system design: key enabler of the SysMoore era

### The Era of Multi-Die System Design is Already Here

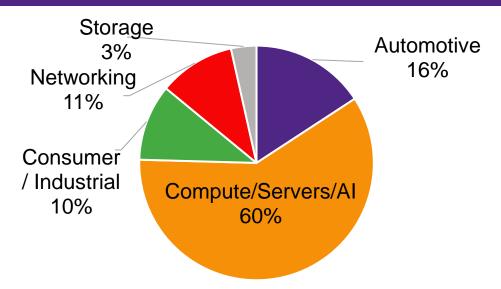

#### Designs by Application

- The datacenter Servers / AI dominate

- NICs, Switches common use case

- Smartphone / Graphics / PC primarily proprietary

- Co-packaged Optics, Automotive ramping

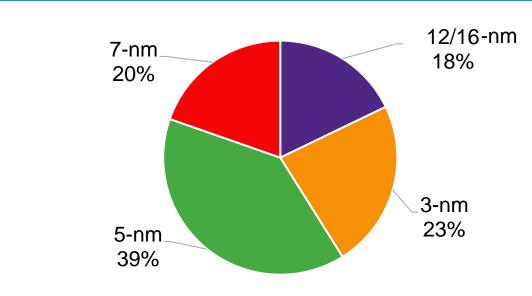

#### Designs by Process Technology

- CPU/Processors driving down Moore's law

- I/O chiplets typically in N-2, N-1 processes (e.g., 7-nm or 12-nm)

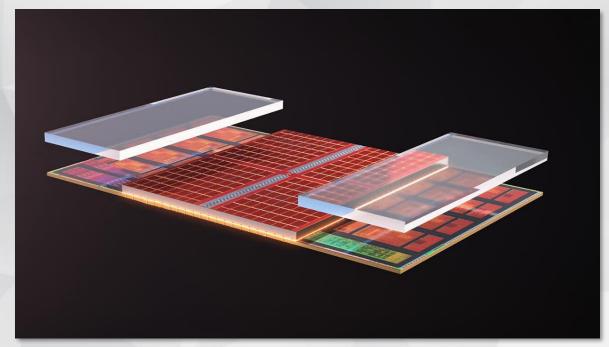

### **Enabling Truly Transformative Products**

Examples of commercial high-performance, high-density multi-die systems

#### **AMD**

3D V-Cache: Hybrid Bonded

3x Energy Efficiency, 15x Interconnect Density (vs. Micro-bumps)

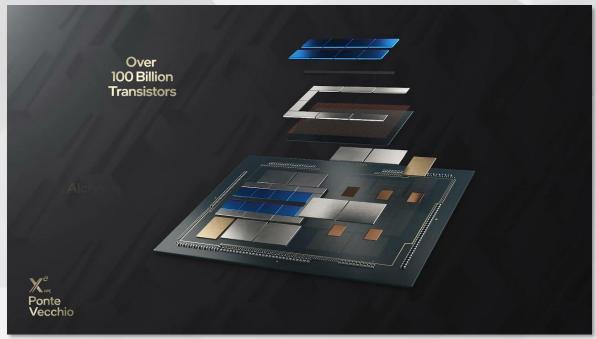

#### INTEL

**Exascale Computing / Al**

100B+ Transistors, 47 Active Tiles, 5 Process Nodes

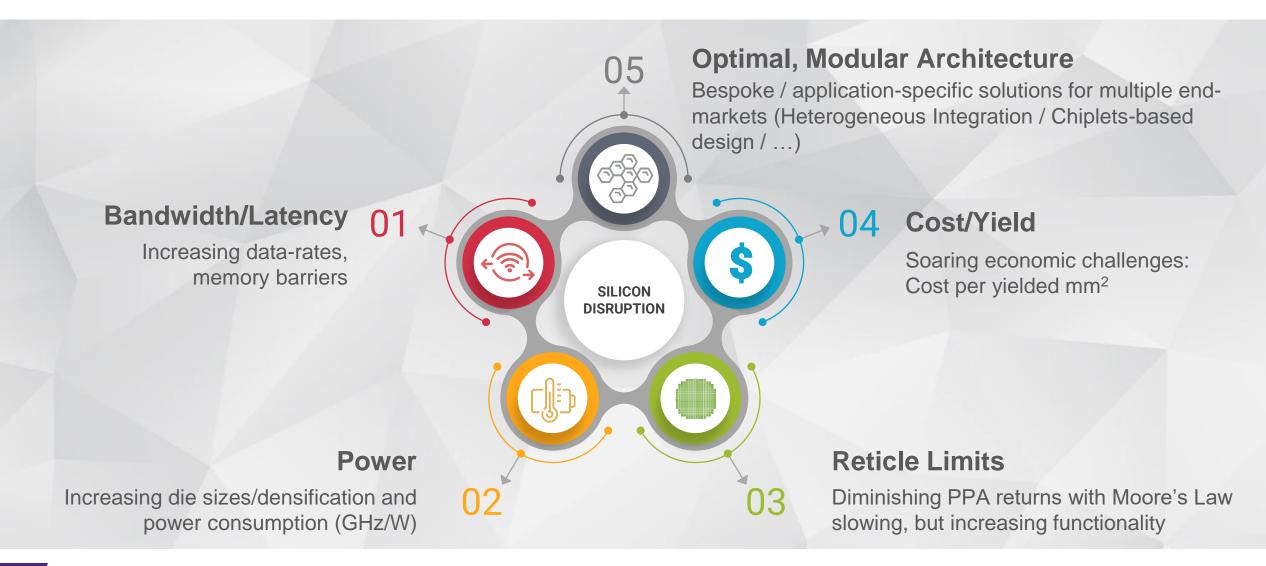

### The Drivers of Multi-Die System Design

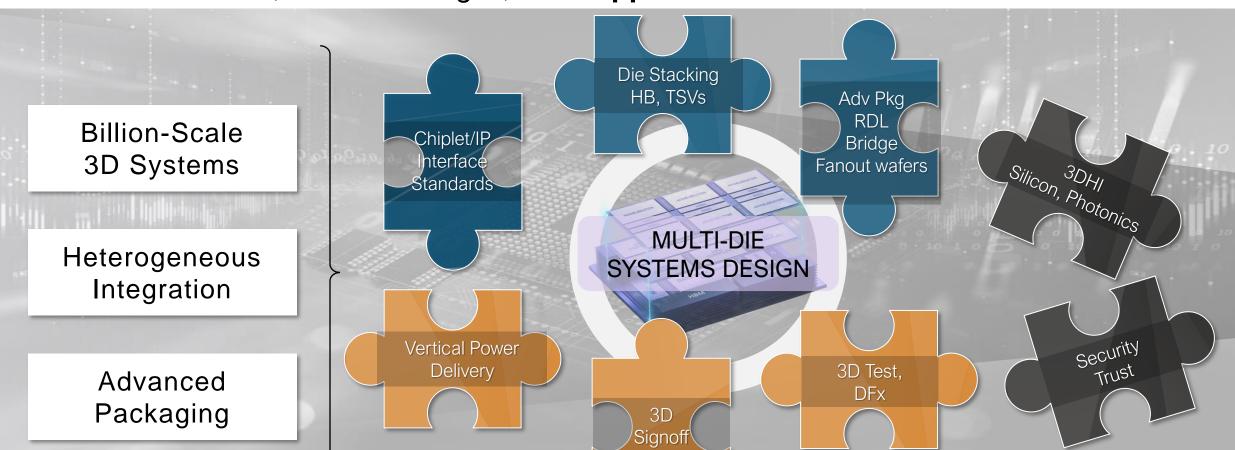

## New Dimensions Bring New Opportunities... and Challenges

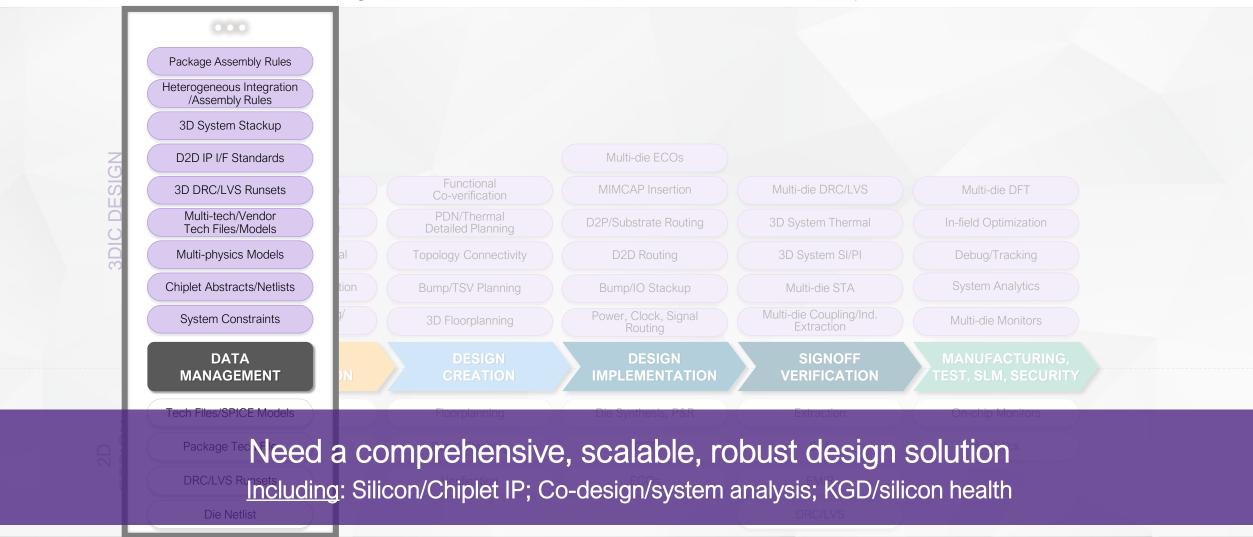

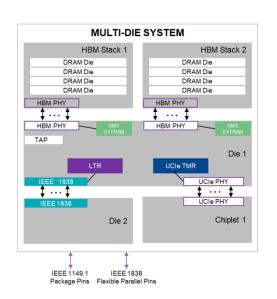

The multi-die/3DHI design flow is expansive – data consistency is critical

### Key Facets of a Multi-Die System-Design Solution

#### Robust Die-to-Die Interface IP at the Heart of Multi-Die Growth

UCle: Emerging as a preferred D2D I/F

- Technical Merits (Most compelling PPAs)

- Energy efficiency <0.3pJ/Bit</li>

- Edge efficiency >5Tbps/mm

- Latency ~2ns from pin to FDI

- Comprehensive and Futureproof

- All use cases

- All package types

- Complete protocol stack

- Future proof with support up to 32Gbps data rate per pin

- Broad Ecosystem

- Wide range of promoters and contributors spanning all industry segments

#### Robust Die-to-Die Interface IP at the Heart of Multi-Die Growth

Synopsys' IP solutions for broad-market applications

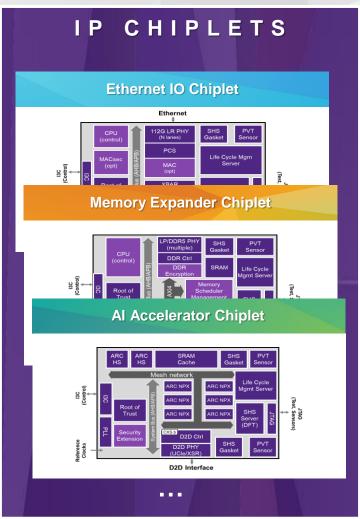

#### SYNOPSYS IP CHIPLETS

- Built on Synopsys' silicon-proven, high-quality IP portfolio

- Flexibility to support multiple package types

- Customizable to target application

- Key features

- Standards-compliant interfaces

- Hierarchical test

- Built-in security

- SLM support

- Yield enhancement functionality

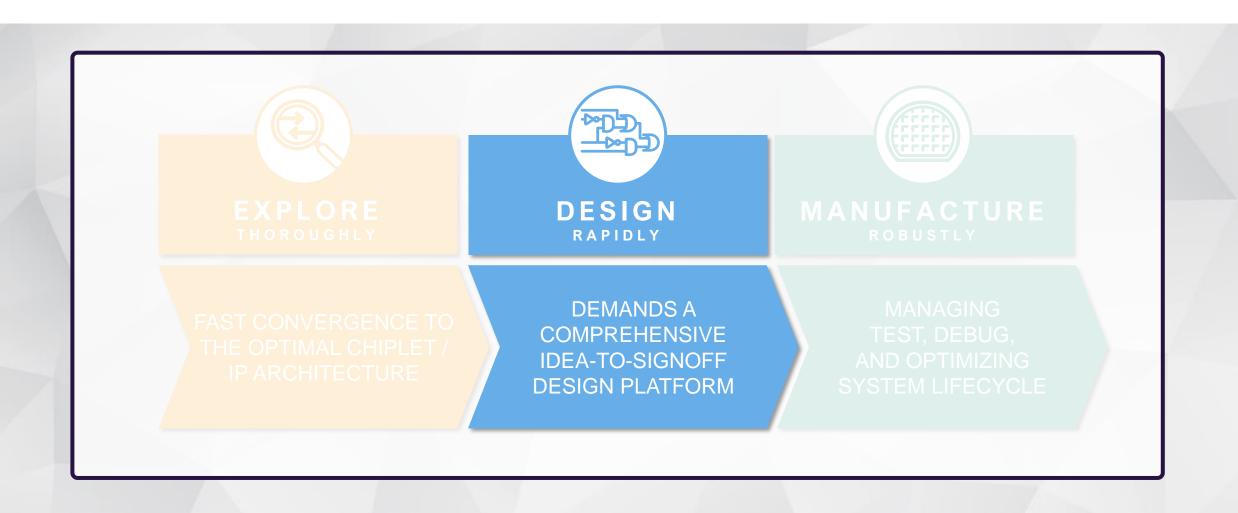

## Key Facets of a Multi-Die System-Design Solution

### Multi-Die Design Requires a Re-Evaluation of Needs

A broader scope of challenges and demands

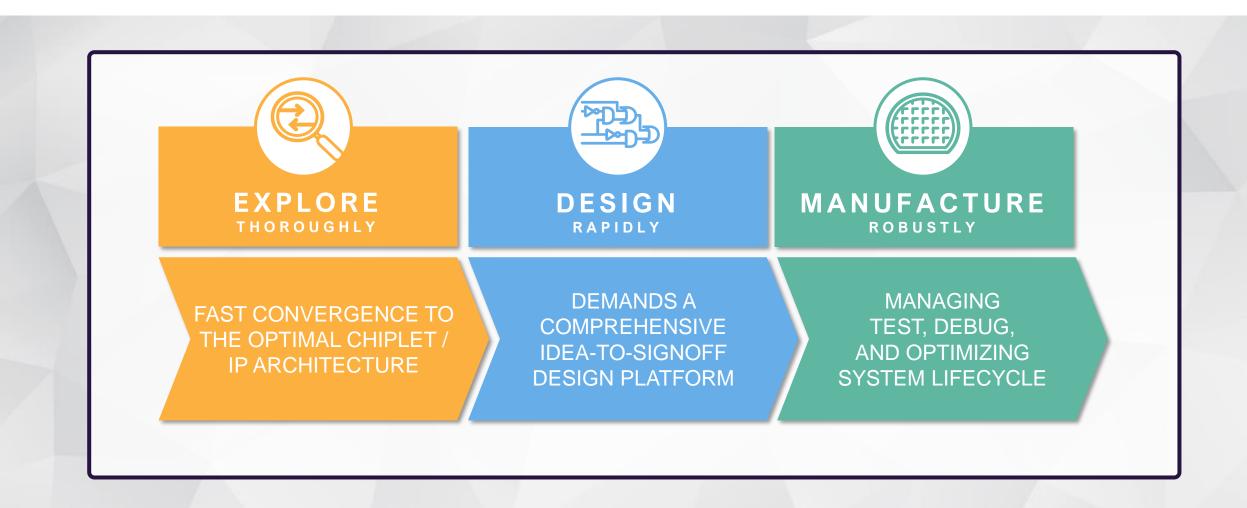

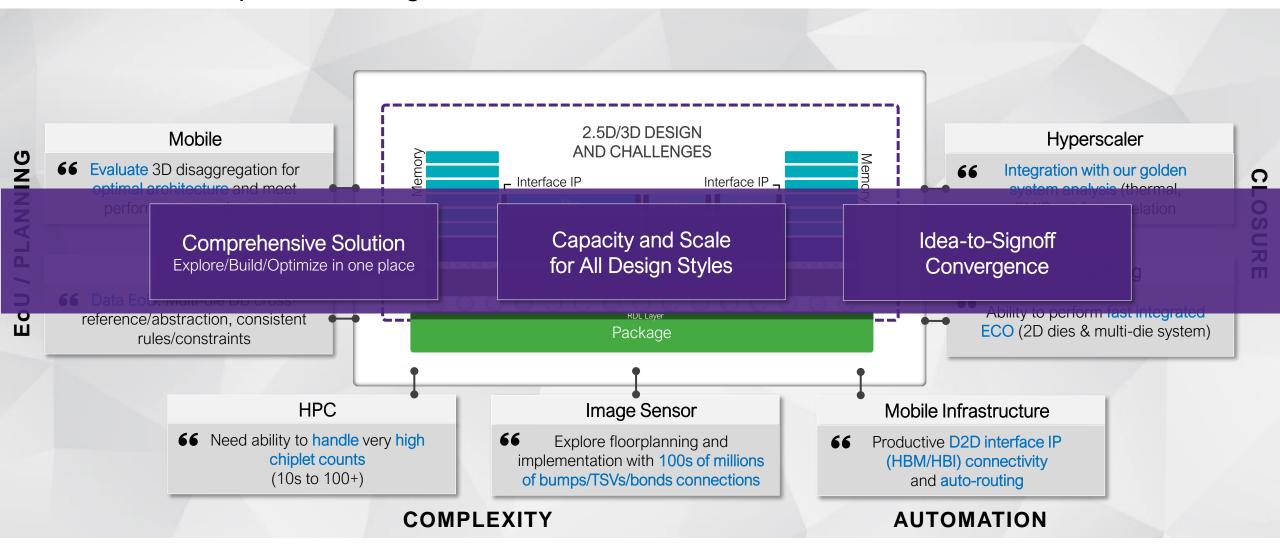

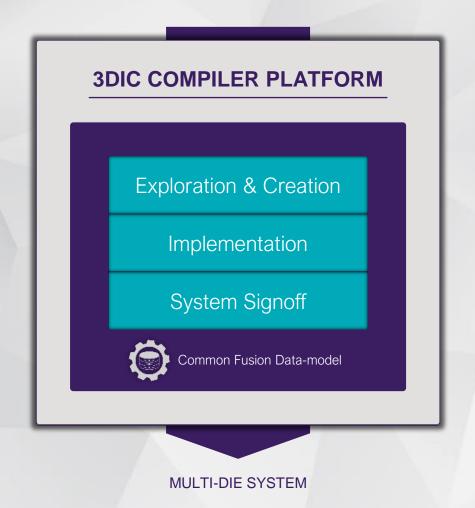

### The Synopsys Unified Platform for Multi-Die System Design

Full-scope system-level co-design and analysis

#### A Highly Scalable Platform

Heterogeneous integration of 100s of billions of transistors

Billion+ inter-connections in a few hours

#### **Seamless 2D to 3D Design Continuity**

Common data-model and tech-files

Efficient, concurrent workflow for faster closure

#### **Unified Full-Flow Productivity**

Single environment for full system design Full breadth engines: design, test, analysis, verification

#### **Trusted, Golden-Signoff Analysis**

Industry-leading technologies – STA, Thermal, EMIR, SI/PI Fast convergence to optimal PPA/mm<sup>3</sup>, accelerate tapeout

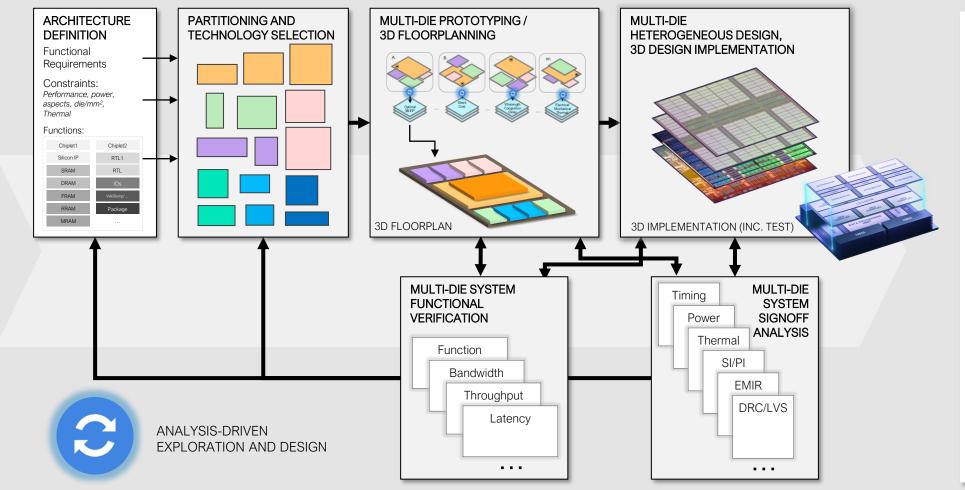

### Convergence and Closure Demands Analysis-Driven Design

Create, Implement, Refine, Converge – A 3DHI example

- Full, partial, or zero netlist design entry for multi-die feasibility analysis

- Auto extraction / abstraction of IP and connectivity from existing 2D dies/modules

- Multi-fab/-node IP and block management support

- Fast floor-planning and connectivity optimization using 3D analytical assessment

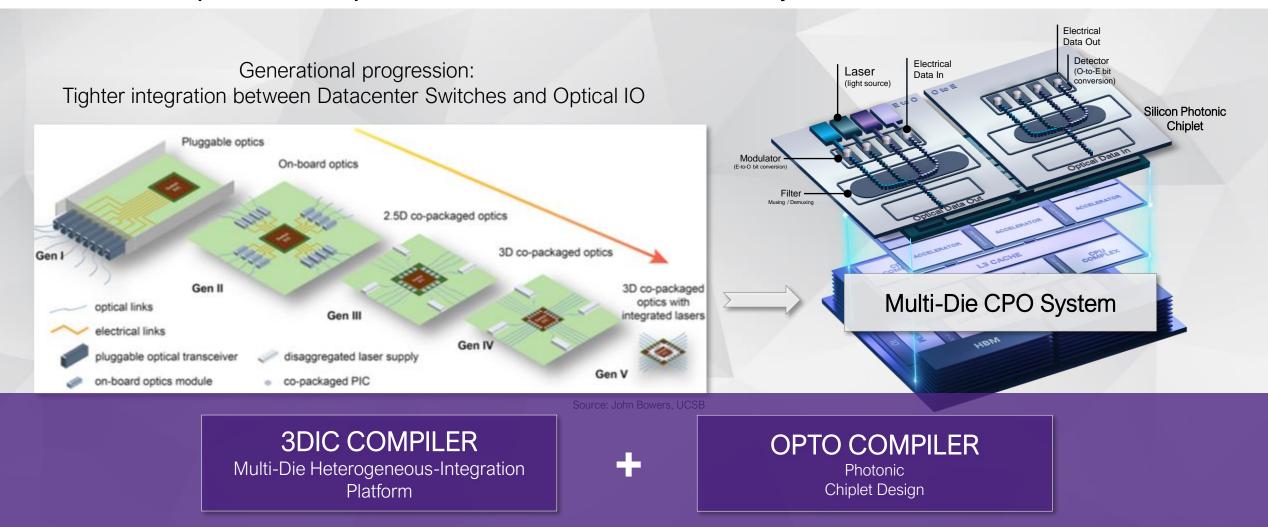

## The Co-Packaged Optics (CPO) Solution to Performance

The silicon-photonic chiplet – Another die in a multi-die system

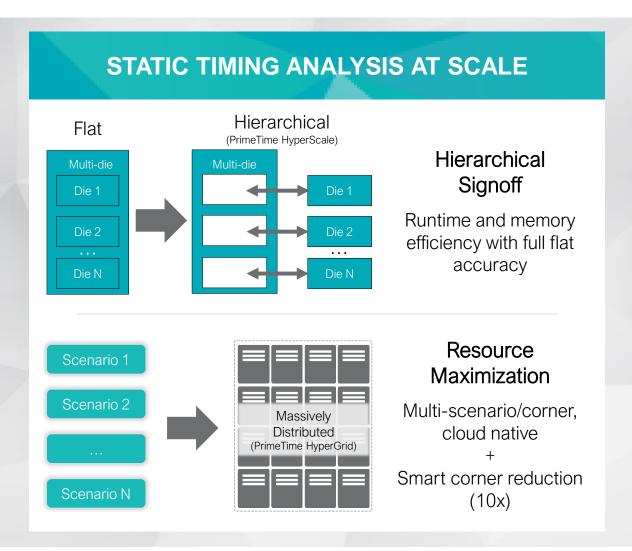

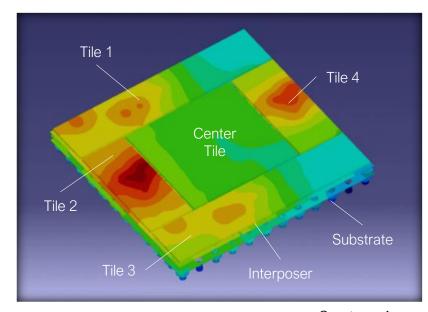

### Achieving Golden Signoff for Multi-Die Systems

#### THERMAL ANALYSIS AT SCALE

Integrated System-level Hierarchical Thermal Analysis

Courtesy: Ansys

### Key Facets of a Multi-Die System-Design Solution

### Enabling the Manufacturing Ramp and Product Reliability

Synopsys' TestMAX and the SLM Family of products

#### **MULTI-DIE SYSTEM TEST AND REPAIR**

PRODUCT QUALITY (KGD, Package, System)

Ensure quality with comprehensive test, debug, repair for multi-die systems

Integrated Test for:

Multiple Dies, Memories,

Interconnects, and

Full-system

Test

Access

IEEE 1838

Logic-to-Logic PHY Monitor, Test & Repair Logic-to-Memory Ext. Memory BIST & Repair Via / Bump / Interconnect

High volume Lane Test & Repair

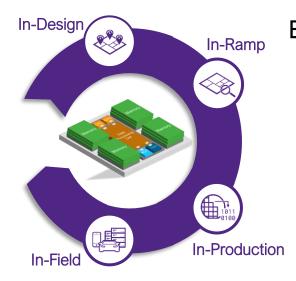

### SILICON LIFECYCLE MANAGEMENT RELIABILITY, YIELD, HEALTH

Enhance multi-die system operational metrics through environmental, structural, functional monitoring

Solution comprises:

Silicon IP

EDA Software, and

Analytics Insights

In-Design

Power/Performance

Optimization

In-Ramp Yield, Failure

ïeld, Failure Diagnosis In-Production

Volume Test, Quality and Traceability

In-Field

Optimization, Safety, Security, Maintenance

# Summary

## Multi-Die Systems: The Next Wave in Semiconductor Design

New Dimensions, New Challenges, New Opportunities...

Need a holistic solution for efficient multi-die system design, and industry-wide collaborations to catalyze *SysMoore Era* innovations