EDPS, HIR Reliability PresentationTWG, Nov 5, 2021

# HIR Package Reliability Roadmap and Co-packaged Optics

Abhijit Dasgupta Center for Advanced Life Cycle Engineering (CALCE) University of Maryland, College Park, MD 20742 dasgupta@umd.edu

#### **Acknowledgment:**

Richard Rao (Marvell Corporation), Shubhada Sahasrabudhe (Intel)

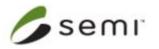

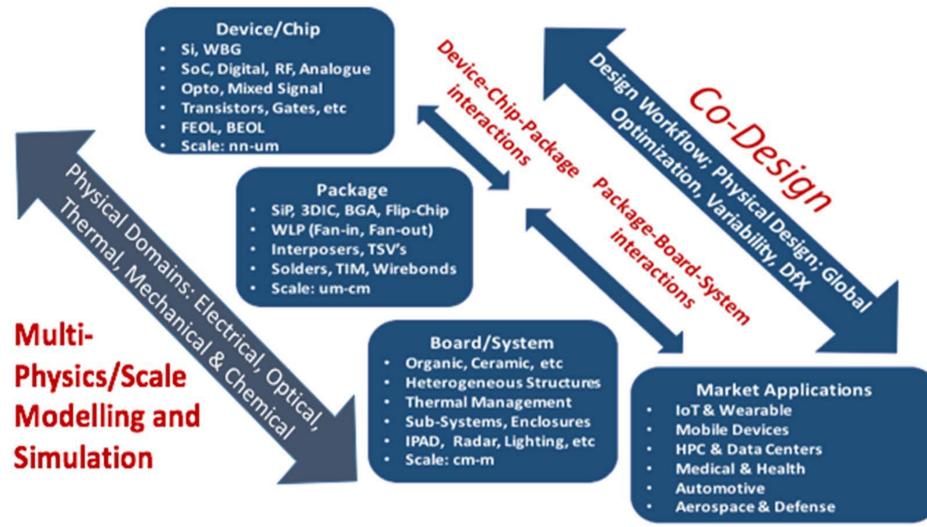

#### Heterogeneous Integration: SysMoore ('More than Moore')

## **Heterogenous integration**

- Electronic (Passive/Active)/Photonic/MEMS/Sensor devices

- Digital; Analog; Logic; Memory; Power; RF

- System, Package (Chiplets) and Wafer levels, including Interconnects and Substrates

- 2.5D and 3D Packaging technologies

semi

# HIR Technical Working Groups

#### HI for Market Applications

- Mobile

- IoT

- Medical, Health & Wearables

- Automotive

- High Performance Computing & Data Center

- Aerospace & Defense

#### Heterogeneous Integration Components

- Single Chip and Multi Chip Packaging (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- RF and Analog Mixed Signal

#### Cross Cutting topics

- Materials & Emerging Research Materials

- Emerging Research Devices

- Interconnect

- Test

- Supply Chain

- Security

- Thermal Management

#### Integration Processes

- <u>SiP</u>

- 3D +2.5D

- WLP (fan in and fan out)

#### **Design & Reliability**

- Co-Design

- Modeling and Simulation

- Reliability

# **Reliability is a cross-cutting TWG: Cross-TWG interactions**

|                        | Reliability<br>Targets                             | Life Cycle<br>Conditions | Design for Reliability                                                                                                                                               | Manufacturing for<br>Reliability                      | Qualification for<br>Reliability                      | Sustaining for<br>Reliability                                | Supply<br>Chain     | Life Cycle<br>Economics<br>& Cost |

|------------------------|----------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|---------------------|-----------------------------------|

| Applications           | Mobile; IoT; MHW;<br>Automotive; HPC;<br>Aerospace |                          | Electromigration;<br>Materials; Co-Design<br>and Simulation; SCMCI;<br>WLP; 2.5D/3D;<br>Interconnects; SIP;<br>Photonics;<br>MEMS/Sensors; Power;<br>RF/Analog; Test | Mobile; IoT; MHW;<br>Automotive; HPC;<br>Aerospace    | Mobile; IoT; MHW;<br>Automotive; HPC;<br>Aerospace    | Mobile; IoT; MHW;<br>Automotive; HPC;<br>Aerospace           |                     |                                   |

| Package<br>Integration |                                                    |                          |                                                                                                                                                                      | WLP; 2.5D/3D;<br>Interconnects; SIP;<br>SCMCI; Test   | WLP; 2.5D/3D;<br>Interconnects; SIP;<br>SCMCI         | WLP; 2.5D/3D;<br>Interconnects; SIP;<br>SCMCI; Security      | Supply<br>Chain TWG | No TWGs<br>yet ??                 |

| SiP<br>Technologies    |                                                    |                          | Analog, rest                                                                                                                                                         | Photonics;<br>MEMS/Sensors; Power;<br>RF/Analog; Test | Photonics;<br>MEMS/Sensors; Power;<br>RF/Analog; Test | Photonics;<br>MEMS/Sensors;<br>Power; RF/Analog;<br>Security |                     |                                   |

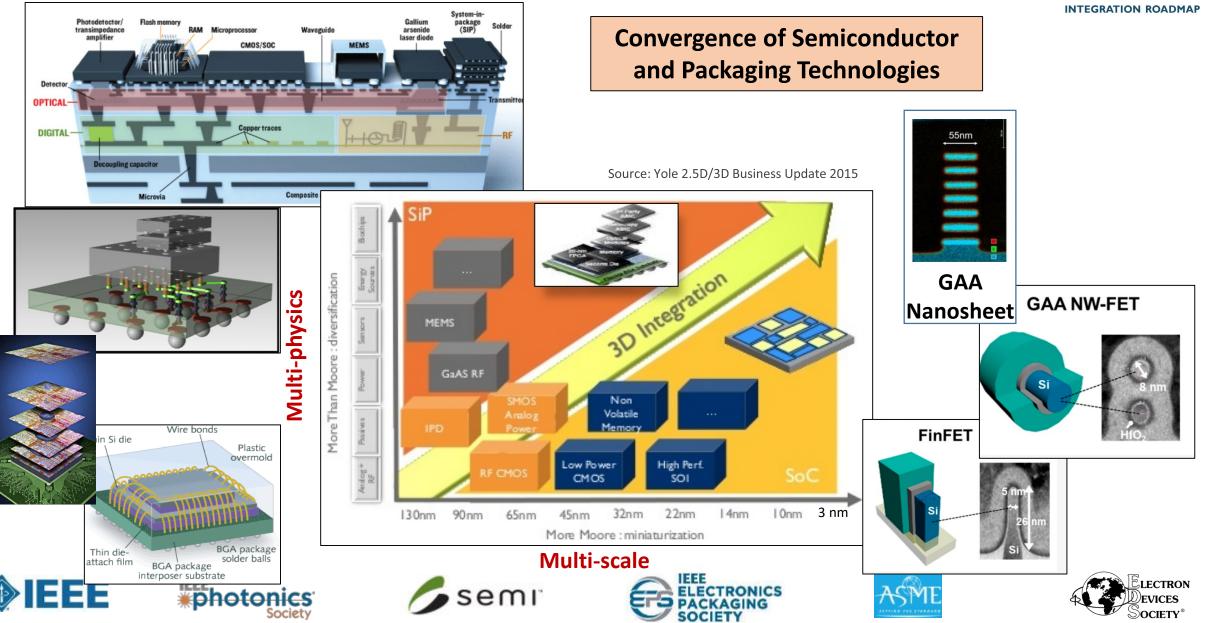

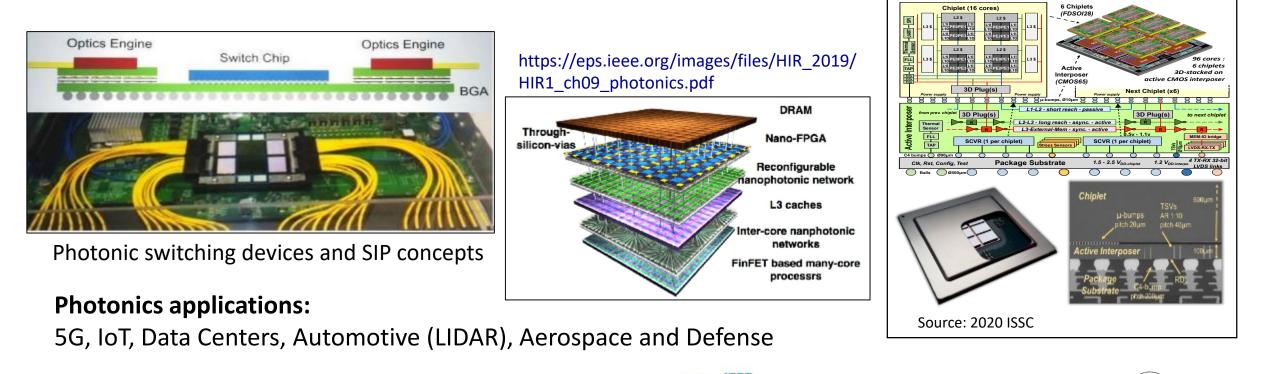

# **Integrated photonics: Challenges & solutions**

https://eps.ieee.org/images/files/HIR\_2019/HIR1\_ch09\_photonics.pdf

#### **Difficult Challenges**

- Physical density of bandwidth

- Thermal management

- Test access for SiP, 3D & Heterogeneous integration

- Photonic Switching to the package

- Cost

#### **Potential Solutions**

- Single-mode WDM fibers

- New materials; multiple temp zones

- BIST, continuous test while running, intelligent redundancy & self-repair

- WDM mux-demux on chip

- High-volume production and a strong and competitive supply chain

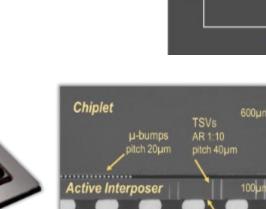

# Upcoming challenges/solutions in integrated photonics

#### https://eps.ieee.org/images/files/HIR\_2019/HIR1\_ch09\_photonics.pdf

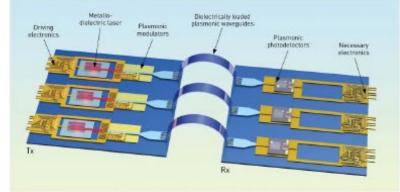

Plasmonic Laser W. Zhu et al. NIST Science Advances (2017)

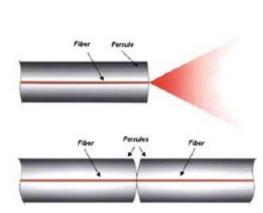

Low-loss Photonic Connectors

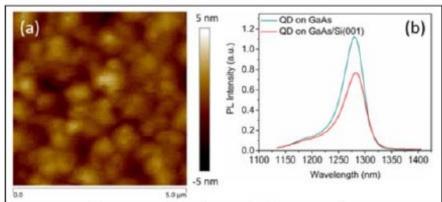

Quantum Dot Laser S. Chen et al. Vol. 25, No. 5 | 6 Mar 2017 | OPTICS EXPRESS 4632

Face-to-face interconnec

by Cu pillars

Solder connection

ASIC

Plasmonic Communication J. Leuthold et al. Optics & Photonics News(2013), pp. 28-35.

Electronic/Photonic Interposer

Courtesy of Xilinx, TSMC, Amkor Cu pillars

Cu pillar

## **HI System Reliability**

# **Reliable HI Systems: Approach**

OCIETY

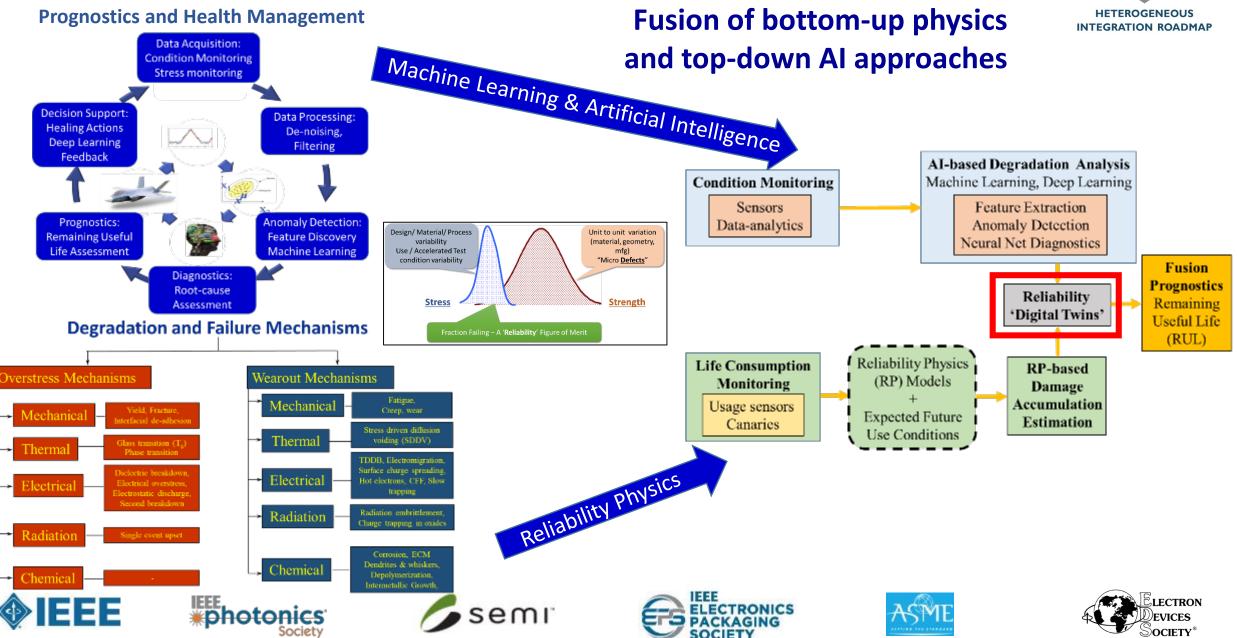

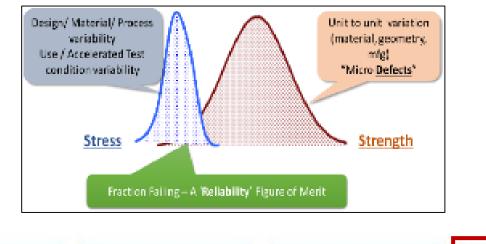

#### **Top down**: **Artificial Intelligence** Multi-physics/multi-scale HI systems and Machine Learning Design/ Material/ Process Unit to unit variation variability (material, geometry, require holistic cradle-to-grave Use / Accelerated Test mfg) condition variability "Micro Defects" methodology Stress Strength Life Cycle Reliability Conditions Targets Fraction Failing – A 'Reliability' Figure of Merit time **Bottom up**: Knowledge **Reliability Physics** Product Health Manufacturing Design for based Testing for Reliability for Reliability Management Failure Distribution Qualification Supply chain Integration time EEE semi TRONICS hotonics

#### **Reliability Assurance Activities**

# **Reliability functions in product lifecycle**

#### **Proof of Concept**

- New Si and Packaging Technology Understanding

- Feature/performance

- Reliability data collection

- Anticipate new failure modes/mechanisms

- Identify Reliability Risks/FMEA

#### Technical Feasibility

- Usage stress conditions

- Reliability targets

- Customer engagement

- Reliability/CPI/BLR Risks

Evaluation

- Test Vehicle Design and Corners

- Eng Verification DOE

- Deliver Reliability Design Rule and aging model

- IP Reliability

- Soft errors

#### Design

- Design Verification

- Implement reliability solutions in the

Development/

- design flow

- Review and assess any violations/trade

- offs

- Product Qual

- Optimize assembly process and materials

- Reliability hardware/dynamic vector/models

- Stress based Qualification

- Knowledge based qualification

**HV Production**

Early failure

rate

Reliability

Solve field

Track field

failure rate

fails

reliability

monitoring

PHM

- Monitor the health of products in field

- Adapt voltage to compensate aging

- Replace failed interconnect

**Design for Reliability**

# **Designing for reliability: Reliability-physics process**

Society

OCIETY®

|                                                                                                                                                         |                                                                                                                                                               |                                                                                     |                                                                                                                                                                                                                       |                                             | HETEROG                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|----|

| INPUTS                                                                                                                                                  |                                                                                                                                                               | ANAL                                                                                | YSIS                                                                                                                                                                                                                  |                                             | OUTPUTS                                                                                                 | DA |

| Hardware<br>configuration<br>materials, geometry,<br>architecture<br>Life Cycle Loading<br>Operational Loads<br>Power dissipation,<br>voltage, current, | Modeling & Sin<br>Multiphysics "S<br>Stresses at f<br>• Electrical<br>• Thermal<br>• Mechanical – Vik<br>• Diffusion<br>• Thermo-hygro-m<br>• Electromagnetic | tress" Analysis<br>failure sites<br>pration & shock                                 | Reliability TWG<br>Reliability Margins<br>Design margins for relevent<br>failure mechanisms dure<br>stresses at each failure<br>• stress margin for overster<br>mechanisms<br>• life margin for wearout<br>mechanisms | ns<br>evant<br>lue to<br>re site:<br>stress | Ranking of<br>potential<br>failure<br>mechanisms<br>and sites<br>Design<br>tradeoffs<br>Risk mitigation |    |

| frequency, duty cycle<br>Environmental<br>Loads<br>Temperature, relative<br>humidity, pressure, shock.                                                  |                                                                                                                                                               | Aggregation to the<br>Reliability block<br>Monte Carlo sin<br>sian updates with fie | k diagrams<br>mulations<br>eld/test data (if any)<br>Analysis<br>urability to changes in:<br>acturing window, life-                                                                                                   |                                             | solutions<br>Accelerated<br>test conditions<br>Reliability                                              |    |

| The life cycle includes<br>transportation,<br>storage, handling and<br>Application environments                                                         |                                                                                                                                                               | · · ·                                                                               |                                                                                                                                                                                                                       |                                             | Assessment<br>Health<br>Prognostics                                                                     |    |

| IEEE #photon                                                                                                                                            | cs 🖉 S                                                                                                                                                        | emi 🍯                                                                               |                                                                                                                                                                                                                       | 45ME                                        |                                                                                                         |    |

SOCIET

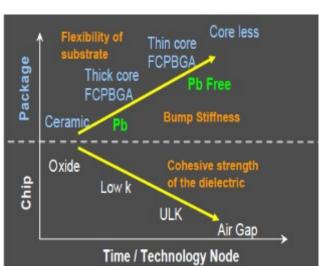

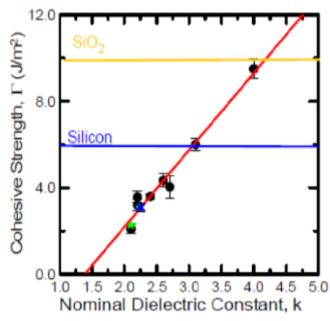

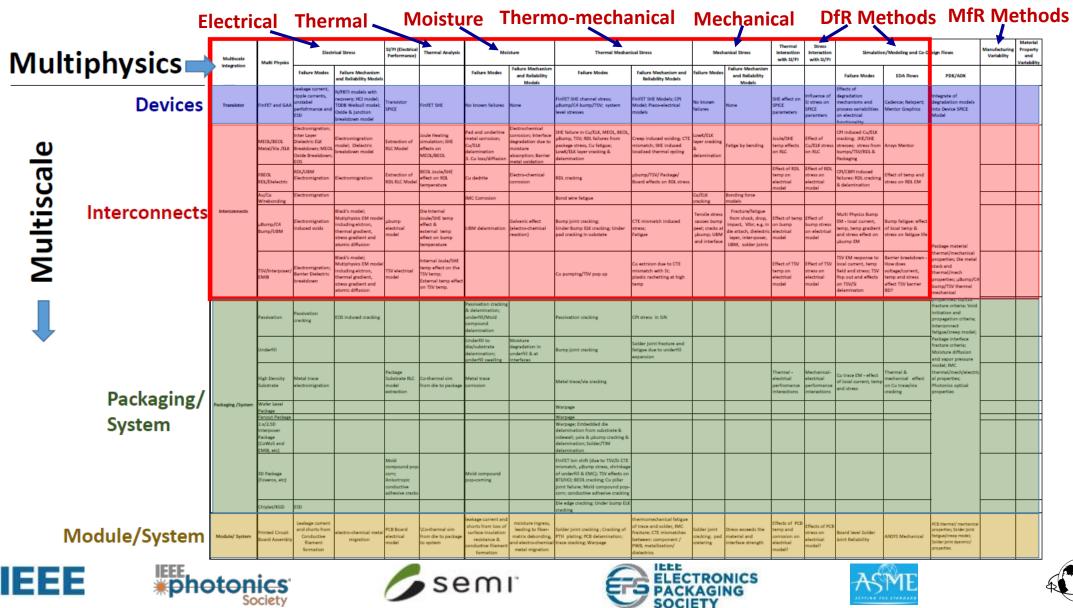

# HI systems: CPI challenges

- CPI issues are increasing with newer Si nodes

- Device and packaging reliability were treated separately in old nodes

- Advanced Si with low k, CPI requires co-development of device and package

- Low k and Ultra low k introduction

- Fragile and poor adhesion

- Build up substrate

- High CTE and warpage

- Pb free or Cu pillar interconnect

- Higher modulus

- Complex die

- Big die size

- Higher power

- Bump on trace

More advanced packaging induced board-chip-package interaction

- UWLP

- **2**.5D/3D

- Big FCBGA

semi

HETEROGENEOUS

**INTEGRATION ROADMAP**

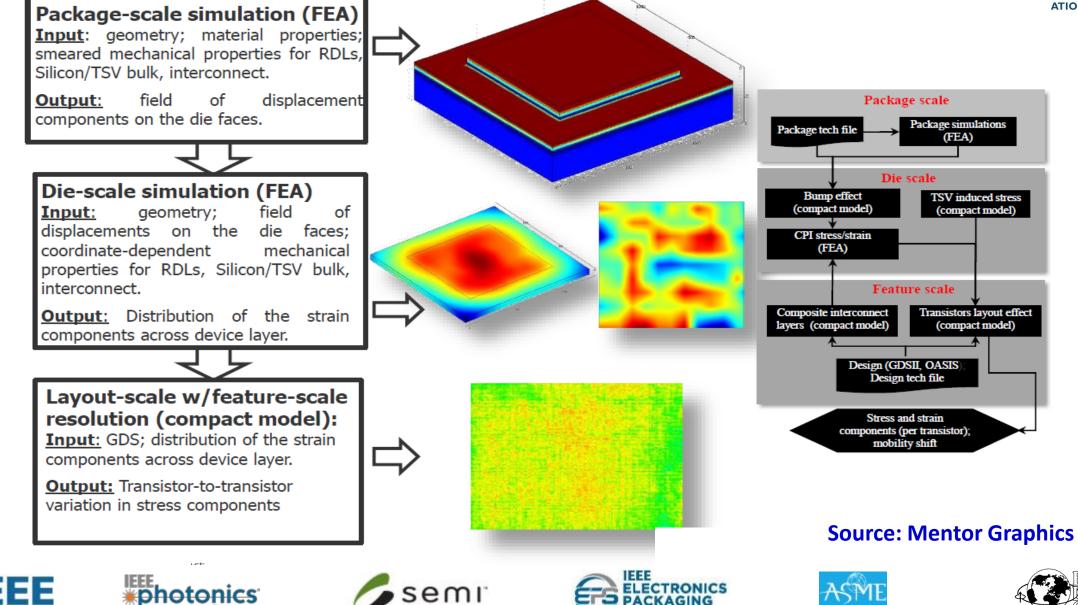

## Multi-scale and multi-physics CPI flow

LECTRON

#### Physics-based modeling simulation and co-design

Source: HIR; Modelling and Simulation TWG

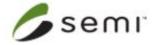

# Modes/Mechanisms/Models for degradation & failure

LECTRON

**EVICES**

OCIETY

## HI Packaging: An overview of 3D IC stresses and reliability

# **CBPI-induced degradation and failure modes**

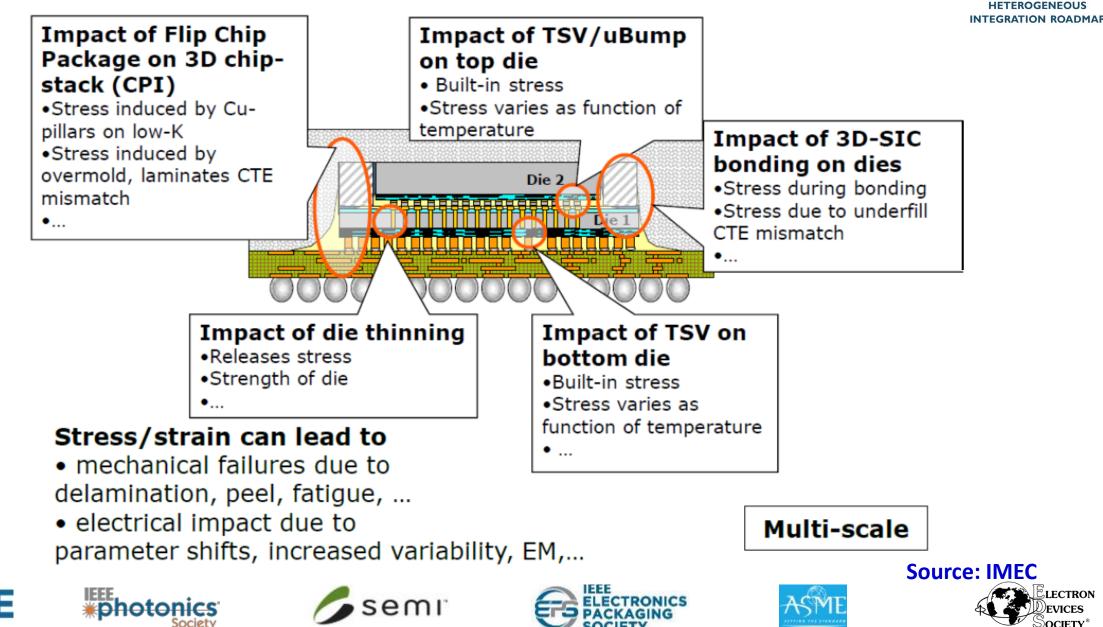

# Influence of manufacturing quality on reliability

# Qualification and testing: Reliability validation/verification

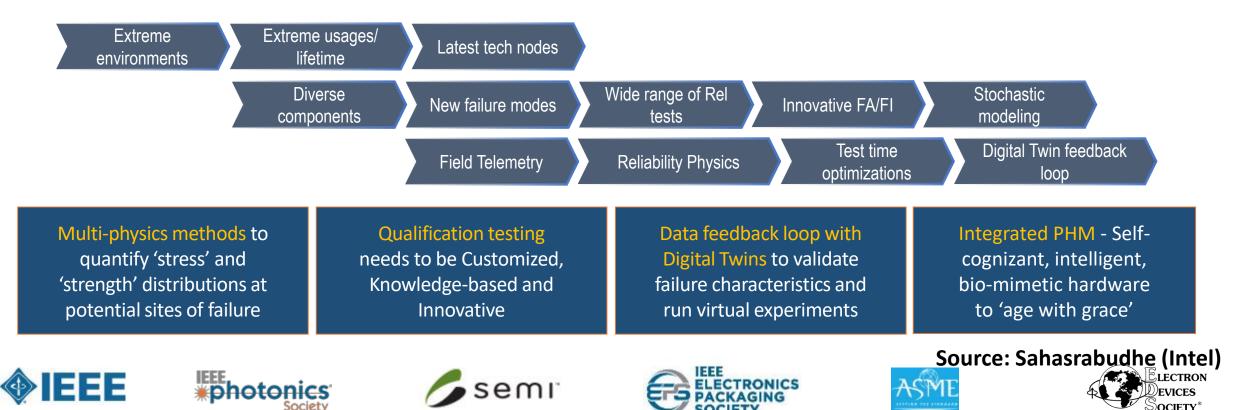

#### The changing and challenging landscape

#### Need for dynamic, flexible models and methods

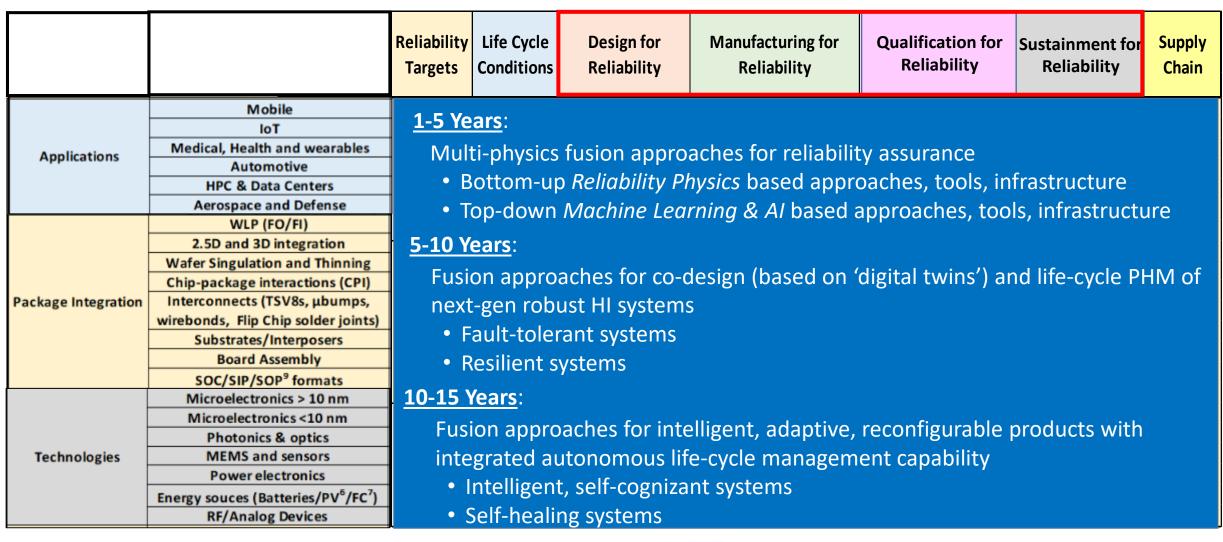

# **Reliability Challenges: Future Outlook**

HETEROGENEOUS INTEGRATION ROADMAP

#### **Reliability assurance activities**

## **Current members of reliability TWG:**

- 1. Abhijit Dasgupta, Univ of Maryland; dasgupta@umd.edu

- 2. Richard Rao, Marvell; richardrao@marvell.com

- 3. Shubhada Sahasrabudhe, Intel; shubhada.h.sahasrabudhe@intel.com

- 4. Willem D. van Driel; Signify; willem.van.driel@signify.com

- 5. Przemyslaw J. Gromala; Bosch; PrzemyslawJakub.Gromala@de.bosch.com

- 6. Hualiang Shi; Lyft; hualiang.shi@gmail.com

- 7. Albert Wang; Univ of California Riverside, aw@ece.ucr.edu

- 8. Pradeep Lall; Auburn University; <a href="mailto:lallpra@auburn.edu">lallpra@auburn.edu</a>

- 9. Bo Ericsson, Ericsson, <u>bo.e.eriksson@ericsson.com</u>

- 10. Siva Shivashankar, Google, <u>rsivasankar@google.com</u>

11. SAAB rep