# Package-Level Heterogeneous Integration – Trends and Challenges

Frank J. C. Lee, Vice President TSMC Technology Inc., North America

TSMC Property

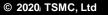

#### **Heterogeneous Integration Is Gaining Momentum**

© 2020, TSMC, Ltd

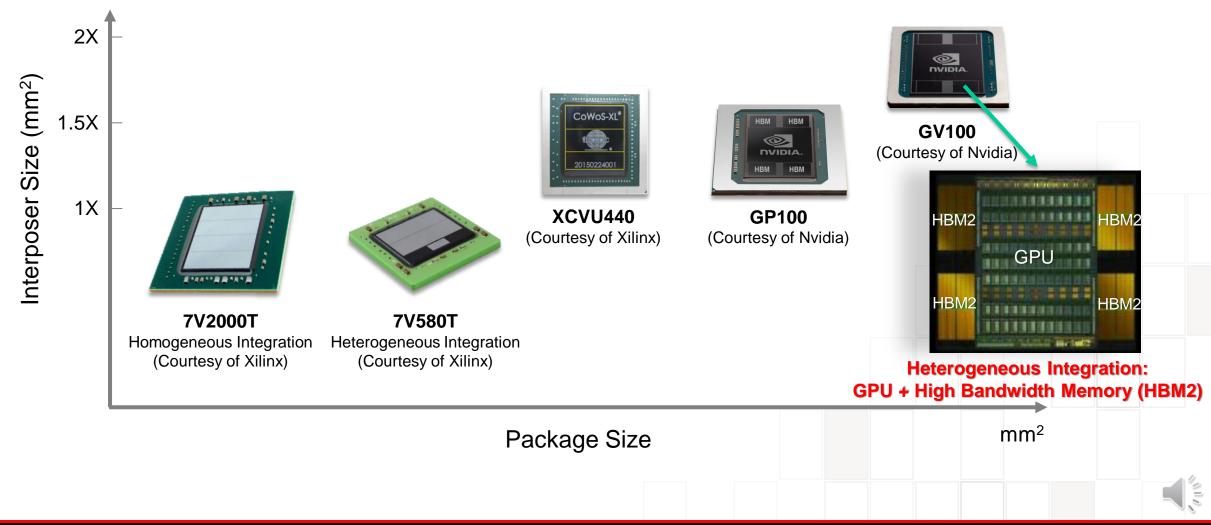

#### Moore's Law Continues with Heterogeneous Integration

#### Outline

- Introduction

- Heterogeneous Integration Technology Trends

- Design Challenges

- System/Technology Co-optimization Needs

- Summary

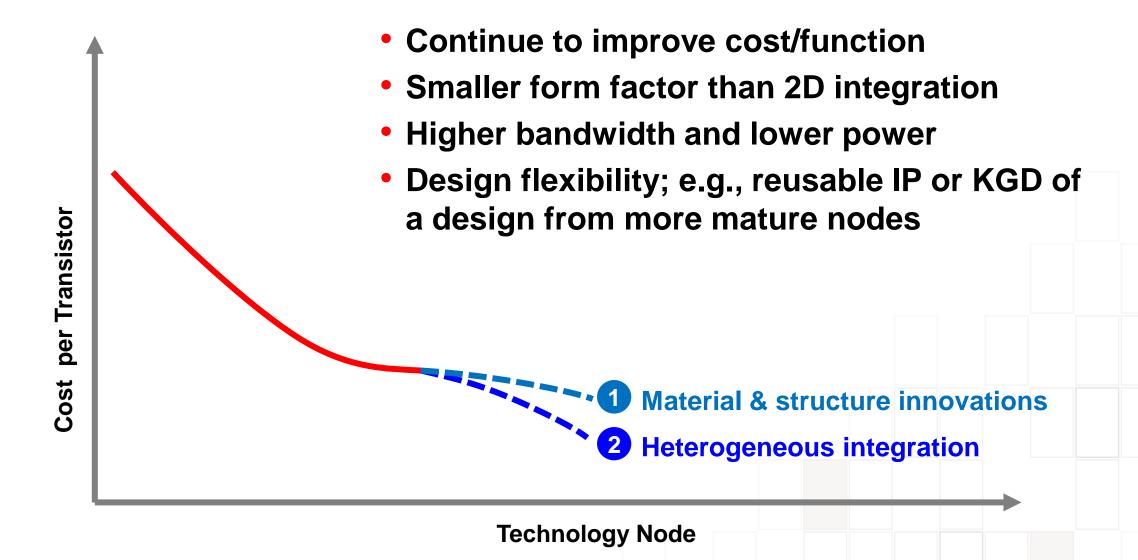

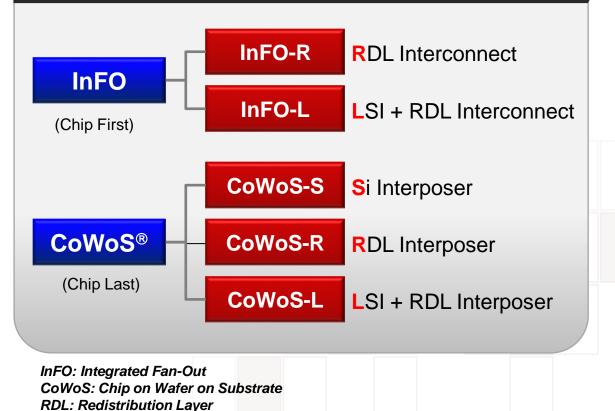

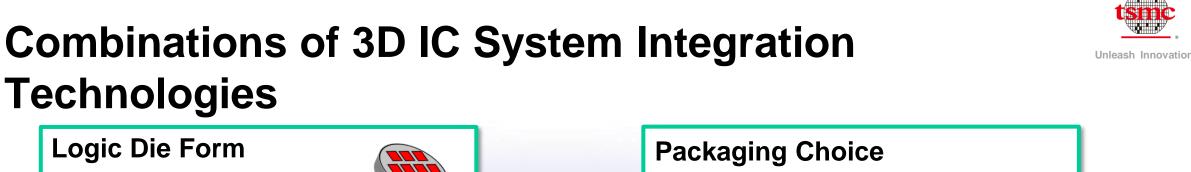

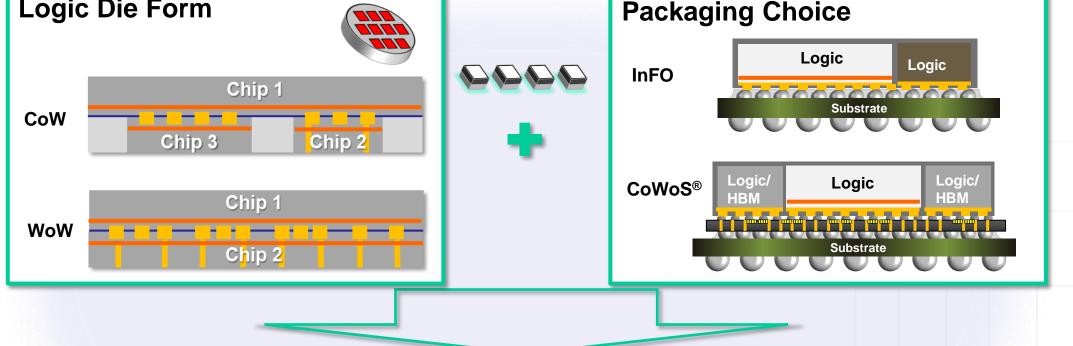

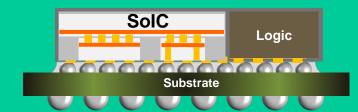

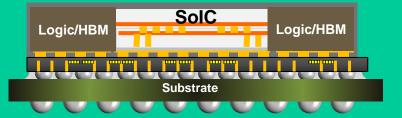

## **TSMC 3DFabric**<sup>™</sup>

SoIC: System on Integrated Chips

LSI: Local Si Interconnect

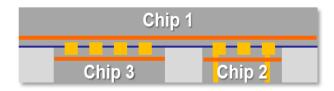

### Wafer-Level Heterogeneous Integration Technologies

5

- Frontend 3D Technologies

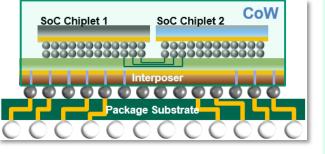

- CoW: Chip-on-Wafer

WoW: Wafer-on-Wafer

- Backend Packaging Technologies

- InFO: Integrated Fan-Out

#### 3D IC Packaging Technology with Silicon Integration Flexibility

#### **TSMC 3DFabric<sup>™</sup> – A Holistic 3D Integration Platform**

TSMC Property

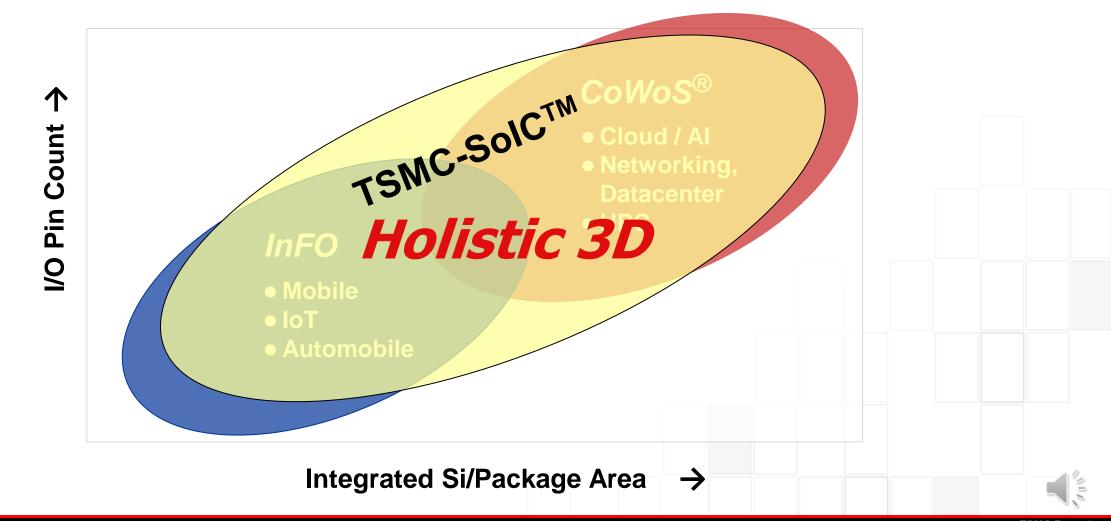

### **Advanced Packaging Technology Trends**

8

#### Outline

- Introduction

- Heterogeneous Integration Technology Trends

- Design Challenges

- System/Technology Co-optimization Needs

- Summary

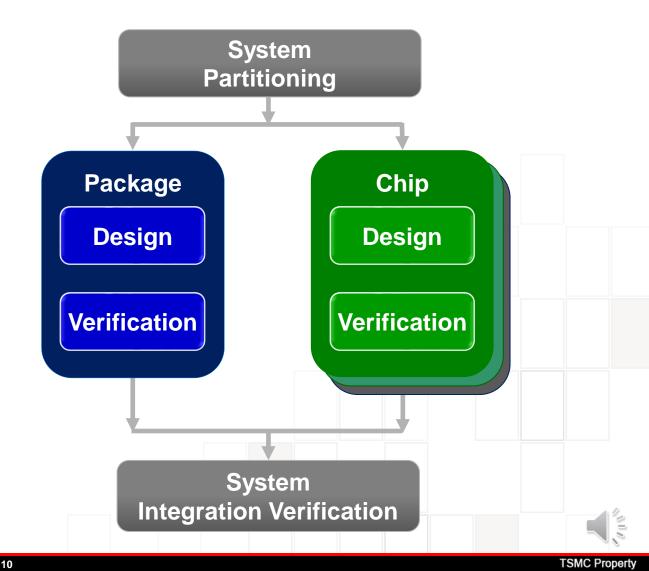

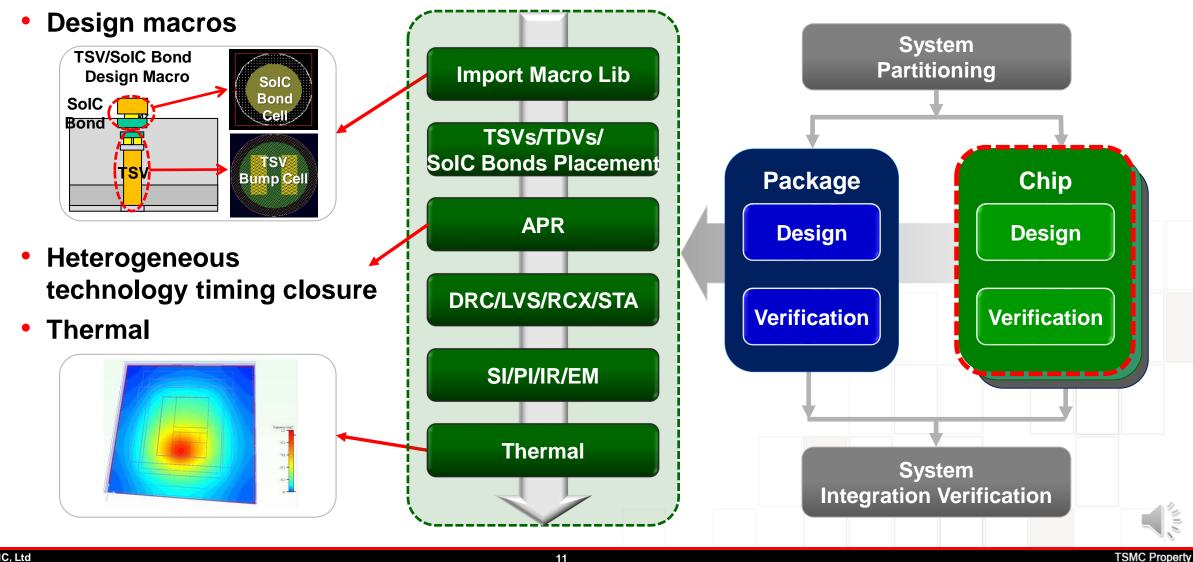

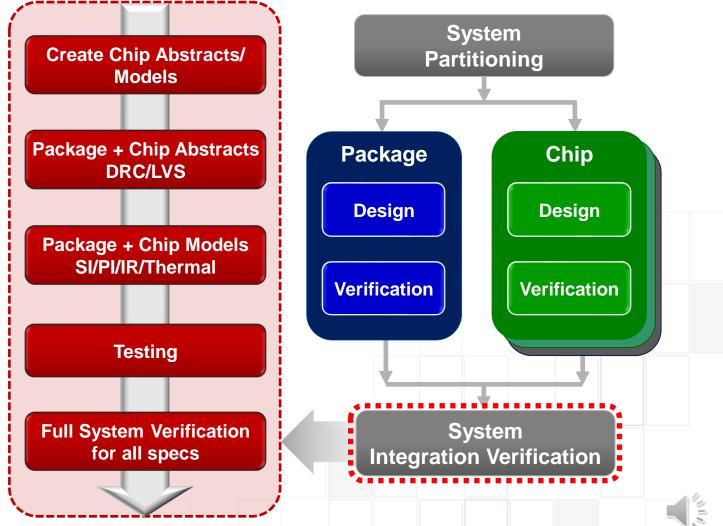

# System Dis-integration and Chiplet Integration Design and Verification

#### A hierarchical approach

- System partitioning

- Functions and timing/power budgets

- Package floorplan

- Chip locations

- Chip implementation

- Pin/bumps locations constraints

- Package-chip interface

- Logical

- Physical

- Electrical

- Test

- Full integration verification

# **TSMC-SolC<sup>™</sup> Design Challenges**

11

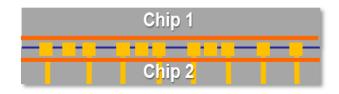

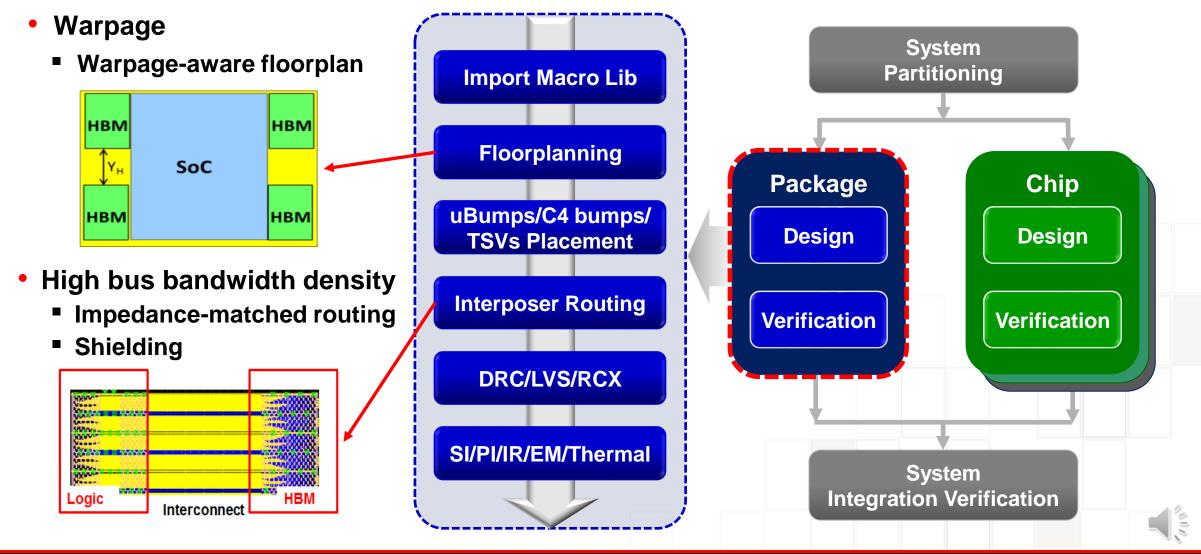

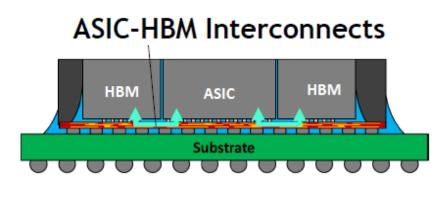

# **CoWoS®** Package Design Challenges

12

TSMC Property

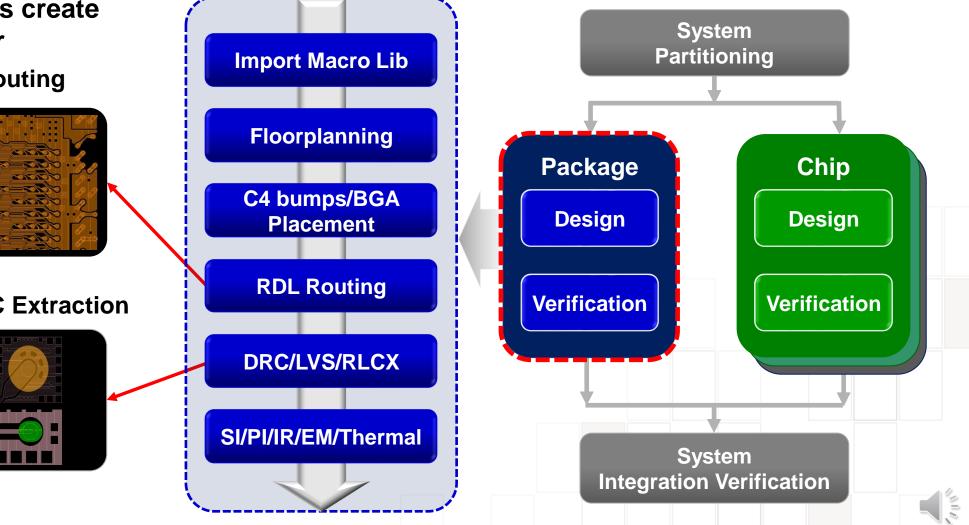

# InFO Package Design Challenges

- Unique shapes create challenges for

- Layout and routing

DRC/LVS/RLC Extraction

# Package-Chip Integration Verification Challenges

- Tools capacity and run time

- Hierarchical flow

- Chip abstracts/models creation

- Interface verification

- Electrical

- Physical

- Logical

- Testing

- 3D Vertical stacking blocks

2D chip probe pads

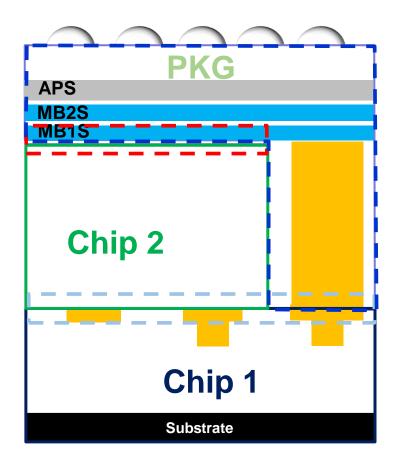

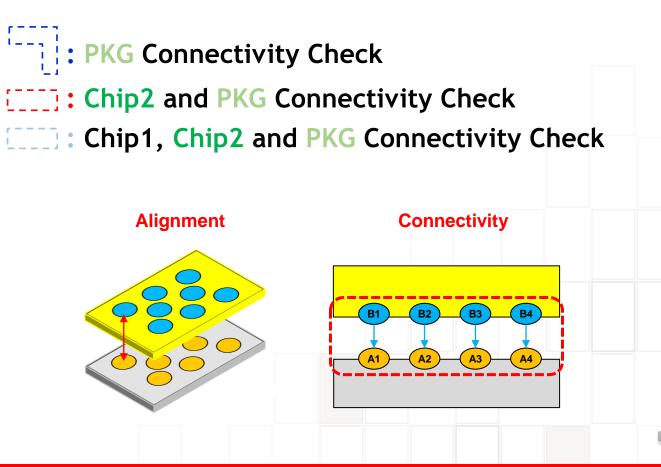

#### **Comprehensive Interface Connectivity Check**

• A SolC example

### **Coping with Hybrid Design Databases**

- Different dies may come from different technologies and are represented in different design databases

- Hybrid design databases need to be merged for DRC/LVS/RC analyses

#### Outline

- Introduction

- Heterogeneous Integration Technology Trends

- Design Challenges

- System/Technology Co-optimization Needs

- Summary

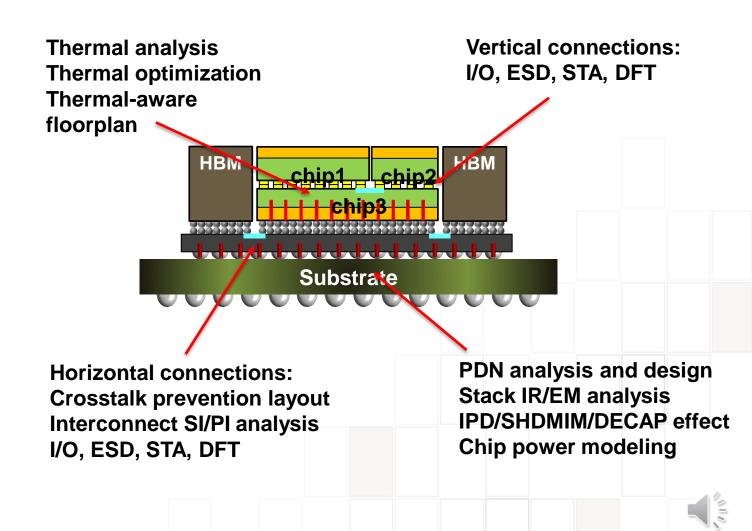

### System/Technology Co-Optimization

- Objectives

- Cost, performance, power, area, yield, form factor

- Co-Optimization examples

- Chip-to-chip link speed

- I/O drivers, ESD, routing patterns

- Power Delivery Network

- Decoupling cap, voltage regulators, power TSVs

#### Package Die-to-Die Interconnect Parameters

- Different package interconnects have different RC loading

- Different dies have different PVT variations

- Need to optimize I/O circuits for power, performance, and area for each packaging technology

|                               | МСМ        | CoWoS®             | InFO      | TSMC-<br>SolC™ |

|-------------------------------|------------|--------------------|-----------|----------------|

| I/O Circuits                  | GPIO       | HBM PHY, LIPINCON™ | LIPINCON™ | Lite I/O       |

| Bump/Bond Pitch               | 130 µm     | 40 µm              | 40 µm     | < 10 µm        |

| Trace Length                  | 10 ~ 20 mm | 0.5 ~ 10 mm        | 1 mm      | 0.01 mm        |

| <b>Channel Insertion Loss</b> | High       | Medium             | Medium    | Low            |

| Power Efficiency              | Low        | Medium             | Medium    | High           |

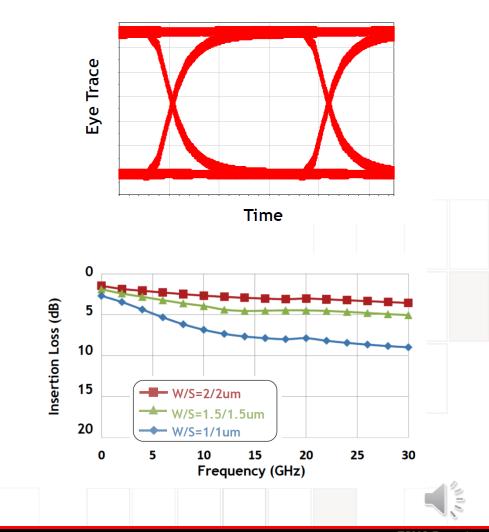

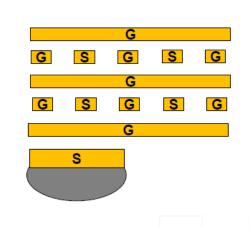

### **Interface Interconnect Design Optimization**

- High data rate bus design requires optimization on

- Shielding pattern

- Routing width/spacing

- Number of routing layers

20

## High Speed Interface I/O Design Optimization

- Design goals

- High speed

- Low energy

- PVT variation tolerant

#### A CoWoS<sup>®</sup> Example

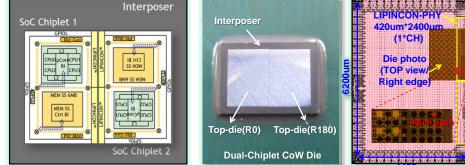

- 7nm 4GHz Arm<sup>®</sup> A72 based CoWoS<sup>®</sup> chiplet design for HPC Application

- LIPINCON<sup>™</sup> for inter-chiplet PHY

- Bandwidth: 320 GB/s

- Data rate: 8 Gbps

- Power efficiency: 0.56pJ/bit

- Bandwidth density: 1.6 Tb/s/mm<sup>2</sup>

- 0.3V low swing I/O

| Comparison                        | IEEE JSSC 4/2020 | ISSCC'18       | ISSCC'17       | Hot Chip'16    |

|-----------------------------------|------------------|----------------|----------------|----------------|

| Company                           | тѕмс             | AMD            | Intel          | тѕмс           |

| Technology                        | 7nm<br>FinFET    | 14nm<br>FinFET | 14nm<br>FinFET | 16nm<br>FinFET |

| Vsw (V)                           | 0.3              | low-swing      | -              | 0.3            |

| Bus Width                         | 320              | 256            | -              | 256            |

| Channel                           | CoWoS<br>500µm   | MCM            | EMIB<br>1mm    | InFO<br>550µm  |

| Die-to-Die<br>Bump Pitch (µm)     | 40               | >100           | 55             | 40             |

| Data Rate<br>(Gbit/s/pin)         | 8                | 5.3            | 2              | 2.8            |

| IO Power Eff.<br>(pJ/bit)         | 0.073            | -              | -              | 0.062          |

| PHY Power Eff.<br>(pJ/bit)        | 0.56             | 2              | 1.2            | 0.42           |

| Bandwidth Density<br>(Tbit/s/mm²) | 1.6              | -              | 1.5            | 0.3            |

Source: M. Lin, et al., p. C28, Symposium on VLSI Circuits, 2019

21

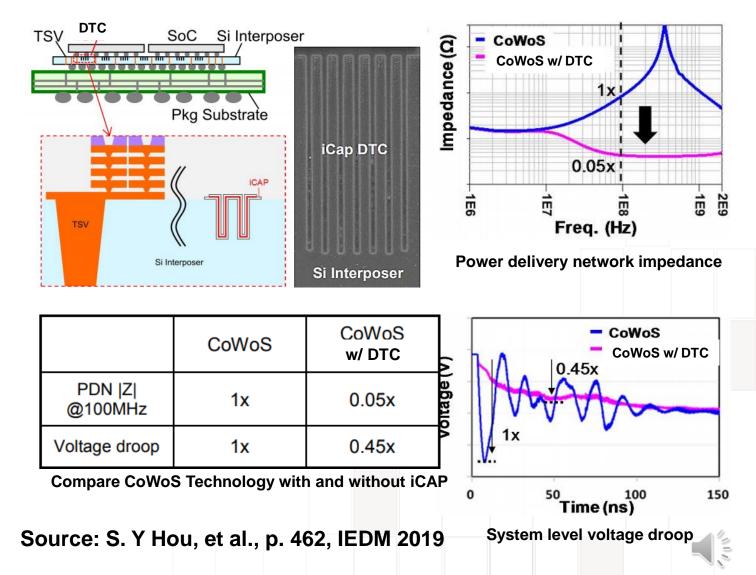

### **Si-Interposer Deep Trench Capacitor (DTC)**

- Key benefits

- Lower PDN impedance

- Reduced voltage droop

- More efficient than MIM cap

- High-K deep trench capacitors

- 340 nF/mm<sup>2</sup>

- Low leakage current

- □ < 1 fA/µm² @ 105C

- Long TDDB lifetime

- <sup>D</sup> 1000 years @ 1.35V

TSMC Property

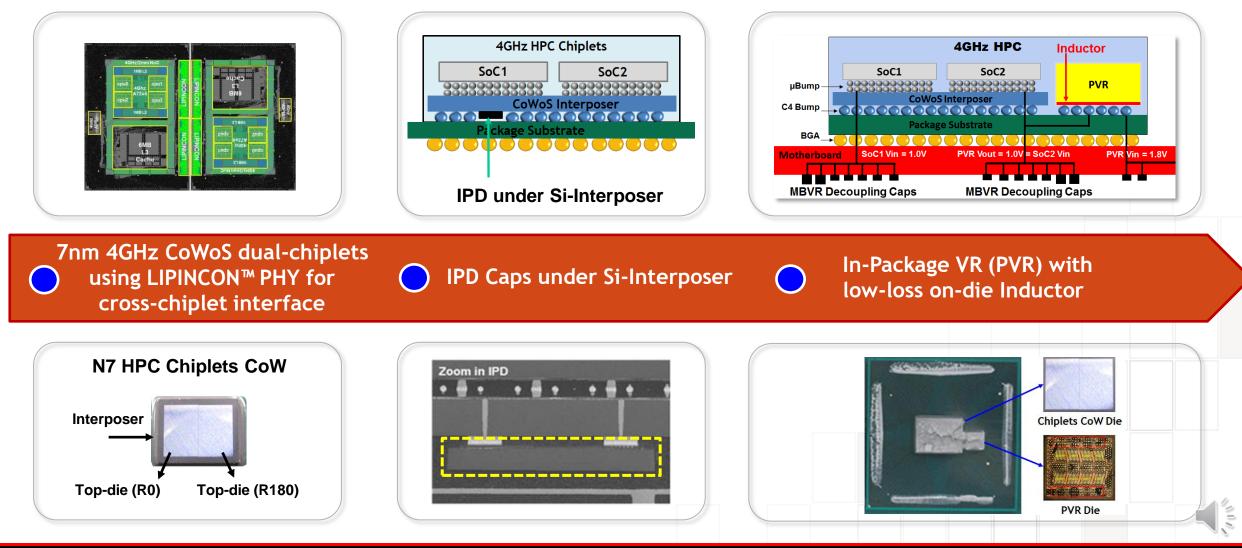

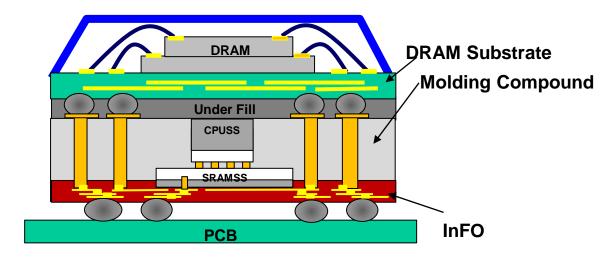

#### System-In-Package Optimization by IPD Capacitors and in-Package Voltage Regulator with On-Die Inductors

23

© 2020, TSMC, Ltd

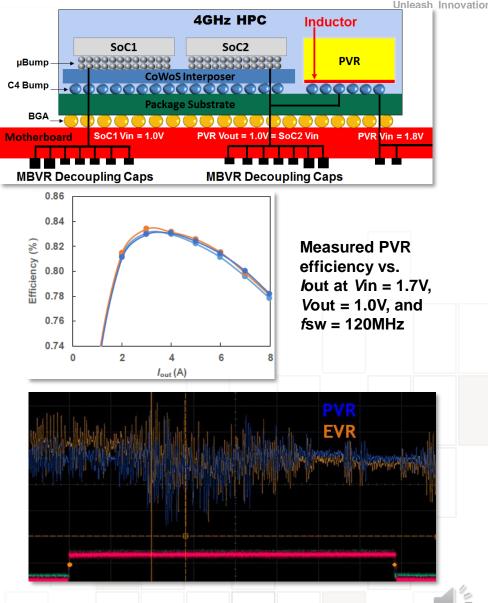

#### **In-Package Voltage Regulators**

- In-Package Voltage Regulators (PVRs)

- Save system board areas

- Reduce system power loss due to PCB traces on the motherboard

- A PVR example

- 4GHz dual HPC chiplets on Si-interposer with both CoW and PVR die on substrate

- PVR regulates SoC2 and external VR (EVR) regulates SoC1

- Both deliver 4GHz performance at 1V and correlate well running Dhrystone at 4GHz

- PVR peak efficiency for target Vout at 1.0V is 83– 84%

Source: A. Roth, et al., JFS5.5, Symposium on VLSI Circuits, 2020

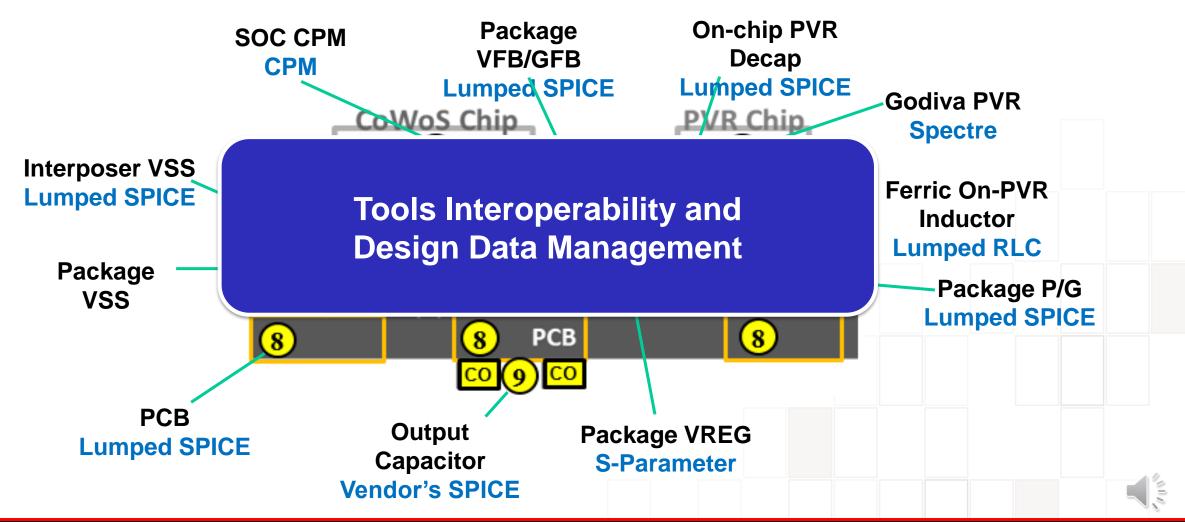

### **System-Level PDN Modeling and Analysis Challenge**

25

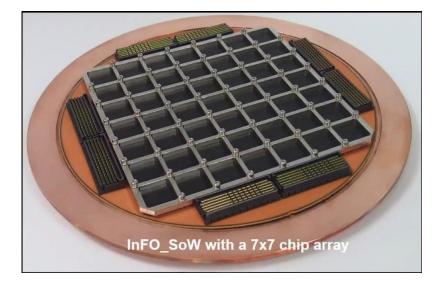

#### **System on Wafer Verification Challenge**

- EDA tools scalability

- Capacity and run time

S. R. Chun, et al., ECTC, 2020.

Cerebras Wafer Scale Engine, S. Lie, Hot Chips, 2020.

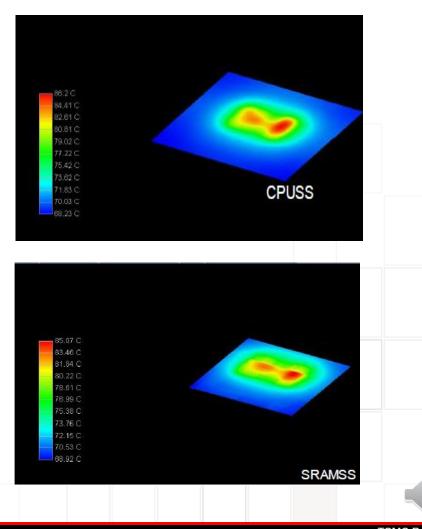

## **Thermal Design Challenge**

- System-Technology co-optimization is needed

- Package: form factors, architectures, materials

- Stacked dies: 3D floorplan, die thickness, DVFS

- Electric-Thermal co-simulation

#### Summary

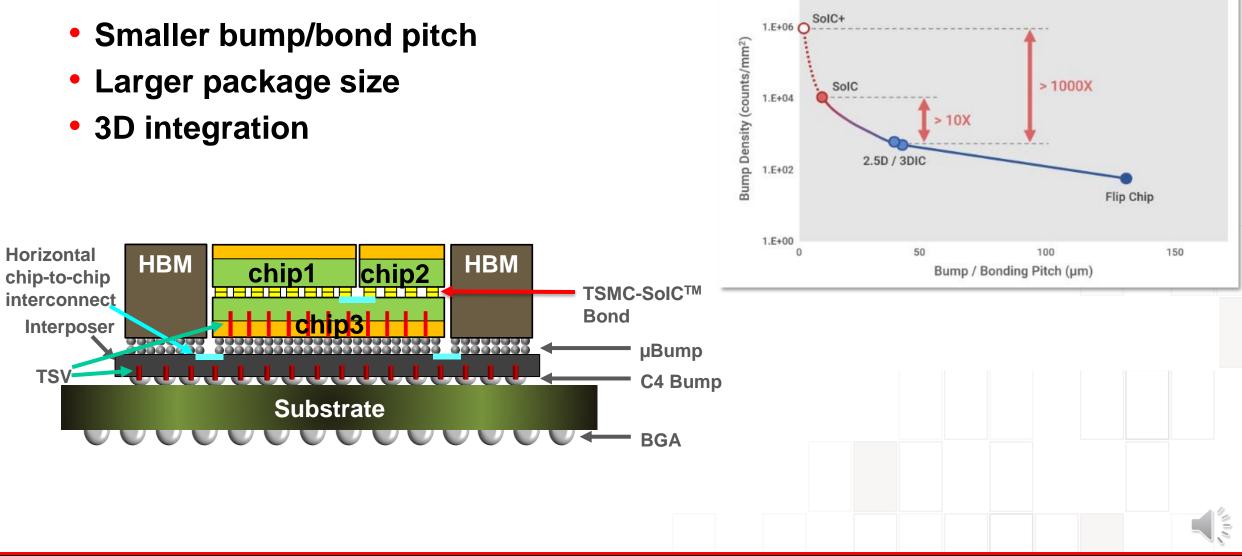

- Moore's law continues with heterogeneous integration technologies

- Technology trends

- Increasing package size

- Decreasing bump/bond pitch

- Many system/technology co-optimization opportunities exist to reduce cost and improve performance, power, area, and yield

- Design technology platforms have been streamlined and are more productive. Still better integration/interoperability between tools is needed.

#### Acknowledgments

- Daniel Chang

- Jonathan Yuan

- Mei Wong

- Stefan Rusu

- Mu-Shan Lin

- Chien-Chun Tsai

- Alvin Loke

- Kenny Cheng-Hsiang Hsieh

- Alan Roth

- Tze-Chiang Huang

- Jerry Tzou

- Shin-Puu Jeng

- Chih-Hang Tung

- Chuei-Tang Wang

- Douglas Yu

- Philip Wong

# **Thank You**