# Connecting Advanced Manufacturing Test To Design, Fab And Final Product Yield For Complex FinFET Defect Challenges

# Matthew Knowles, Ph. D.

Product Marketing Manager

Tessent Silicon Learning

Mentor, A Siemens Business

September 2018

# Outline

- Yield Challenges

- Scan Diagnosis Basics

- Data Sharing Fabless / Foundry

- Conclusions

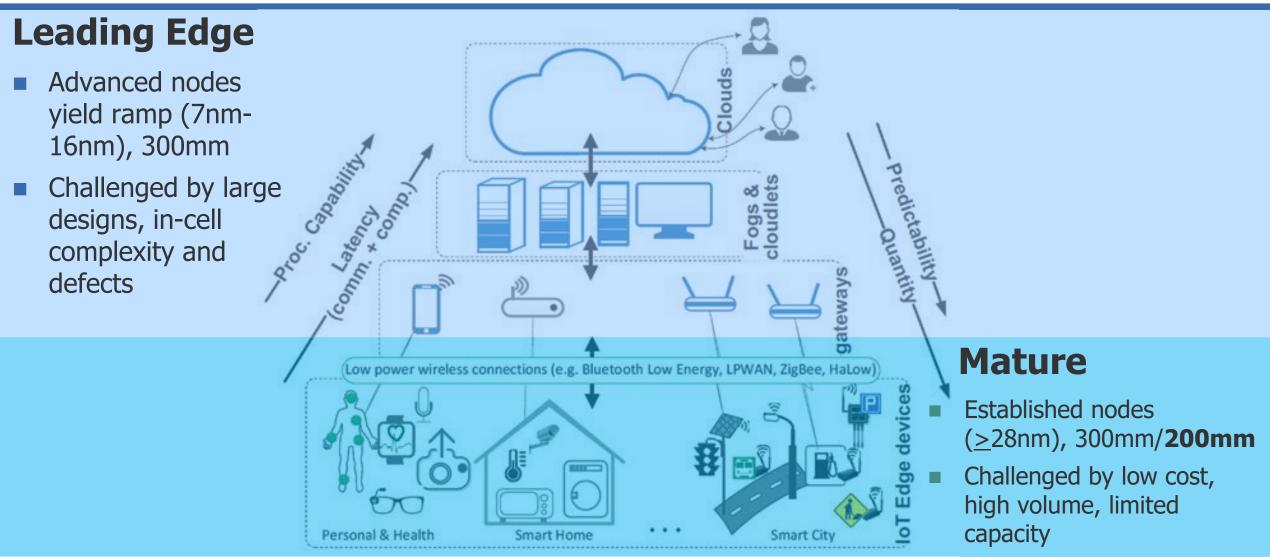

# **Market Landscape and Challenges**

Figure 1: The layers of IoT computing and the communication between them. (Image: F. Samie, L. Bauer, and Khenkes, Imerachinglogies for Finded and the communication between them. (Image: F. Samie, L. Bauer,

3

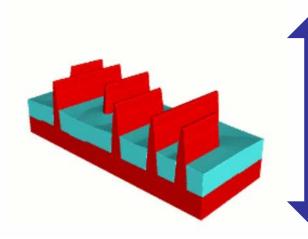

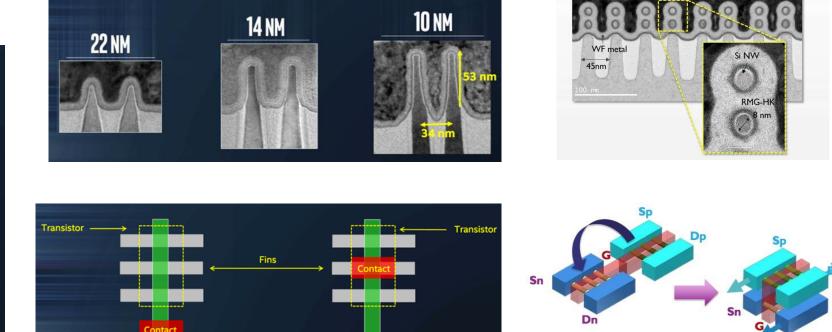

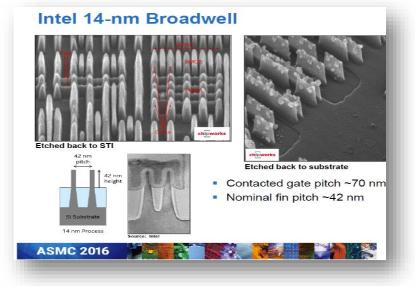

# Leading Edge Challenges: Complexity

- Big increase in transistor processing complexity 7/10/14nm nodes

- "Myriads of systematic defects" for 10nm

- "With 10nm the number of multi-patterning steps makes things much more complex"

- "7nm is a disaster (because of the number of steps)"

- "With 7nm it takes 21 days to go from M0 to M1, compared to 3-4 days in 14nm"

- "90% of defects are inside cells"

Advanced cells now have multiple layers included

Old cell was only very first layers of the transistor

4 from Coventor Semulator3D 4 M.Knowles, Mentor A Siemens Business, EDPS 2018

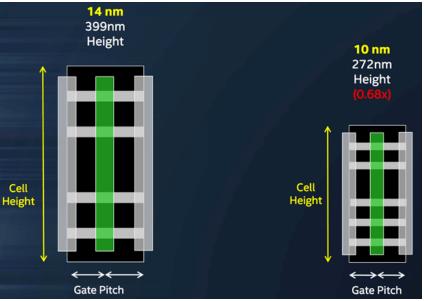

# Leading Edge Challenges: Complexity

- Trend continues with future 5nm/3nm nodes

- Further scaling requires density increase in addition to pitch scaling

https://techreport.com/review/31660/intel-defends-its-process-technology-leadership-at-14nm-and-10nm/2

# **How to Solve Systematic Yield Issues?**

M.Knowles, Mentor A Siemens Business, EDPS 2018

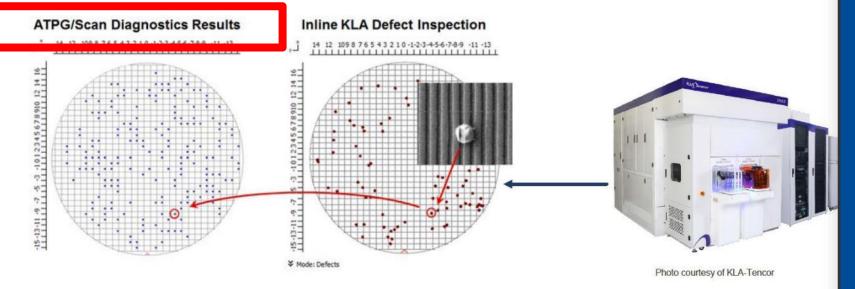

# **Data Sharing**

#### **Fabless-Foundry Information Exchange**

Beyond WAT data → Open sharing of more IN LINE data including KLARF

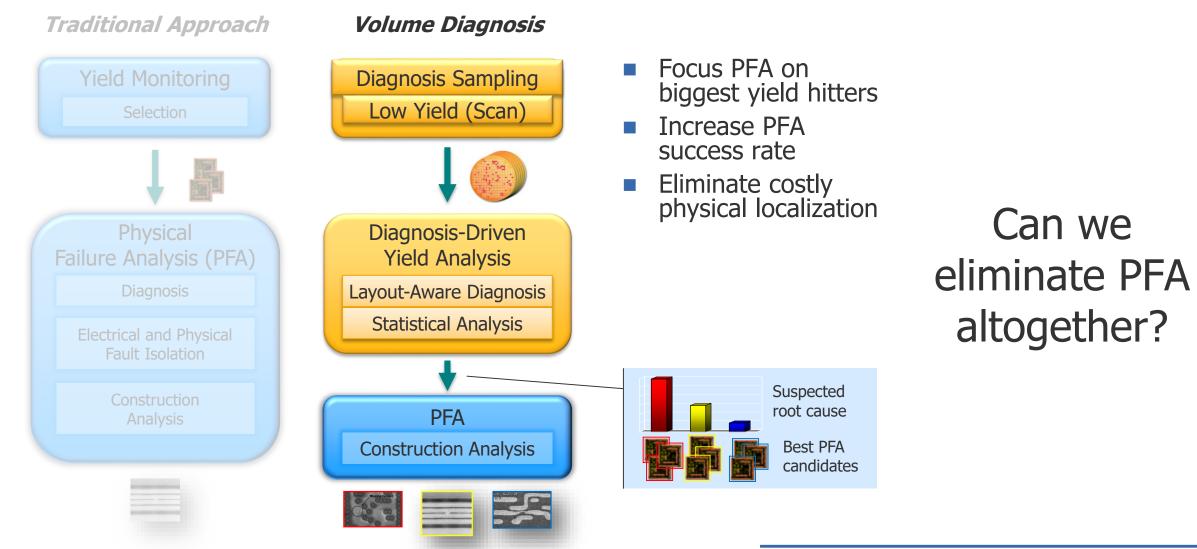

# Q: Why Volume Diagnosis?

# A: Eliminate PFA altogether!

Overlay of fab defect data to identify origin of mapped failing nets/cells.

Eliminate need to PFA defects with a known source in fab

Improves signal-to-noise ratio to identify outlier systematic defects thru PWQ's

W.J.Miller - ASMC 2017

William Miller, VP Engineering, Qualcomm ASMC 2017

7 M.Knowles, Mentor A Siemens Business, EDPS 2018

# A: Reduce costs.

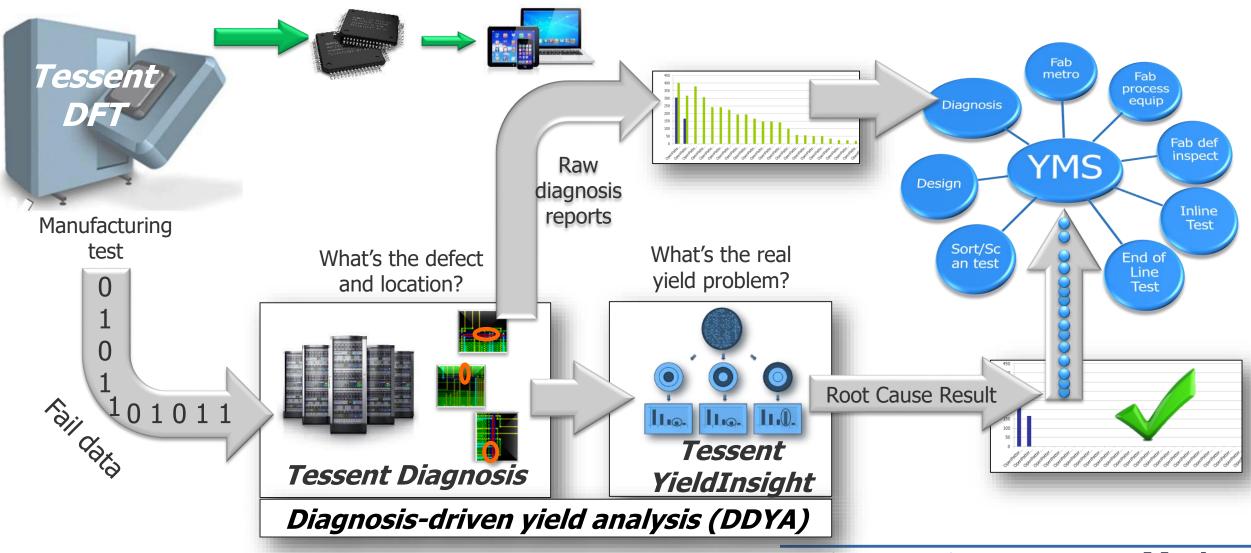

# **Leveraging Scan Test for Yield Learning**

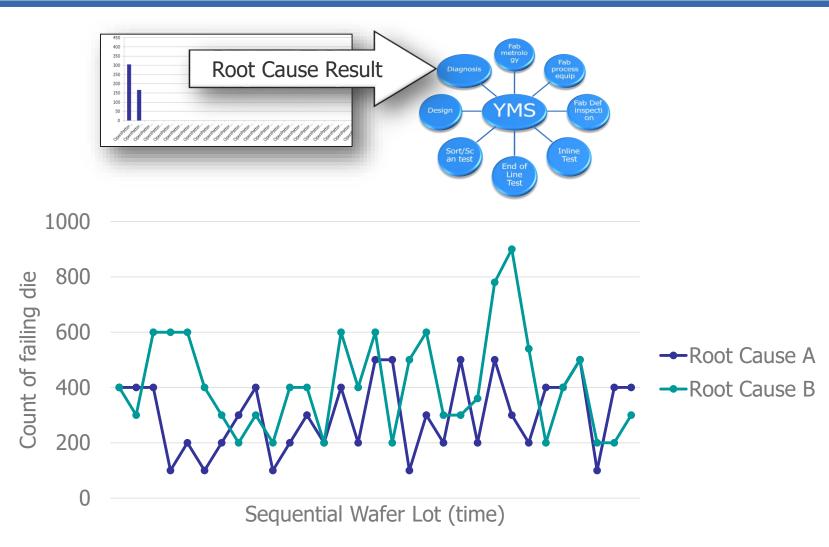

# Why Diagnose All Fails?

- Monitor specific root causes over time to understand variability

- Accelerated excursion response

- Trigger outliers will drive response

- Root Cause  $A \rightarrow$  etch equipment issue

- Root Cause B→ pattern design marginality

- …Prevent excursions

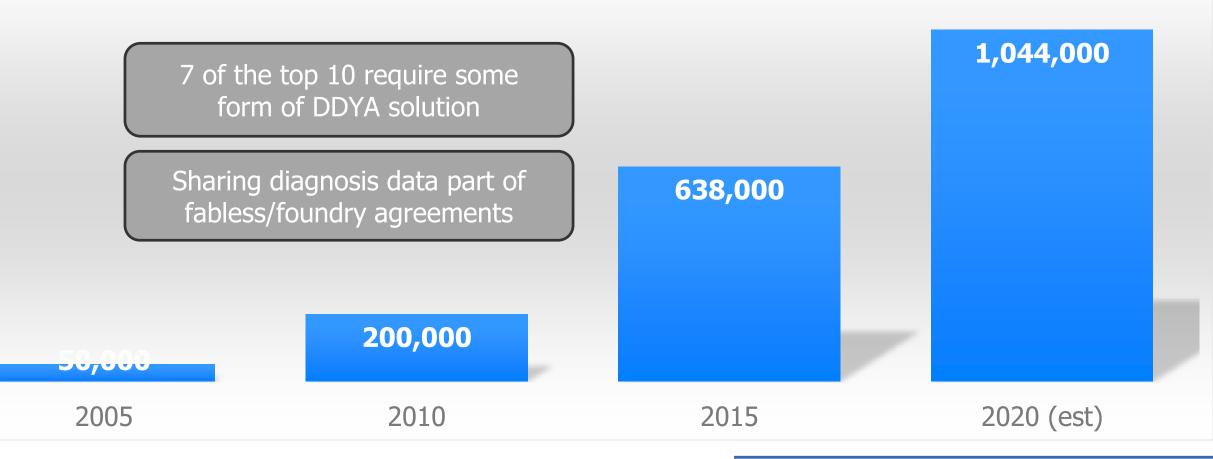

# Industry Moving→100% Analysis of All Failed Die

Die Diagnosed per Day

Source: ITC 2016 plenary keynote: Dr. Wally Rhines https://youtu.be/A0K3rkWiXJo

10 M.Knowles, Mentor A Siemens Business, EDPS 2018

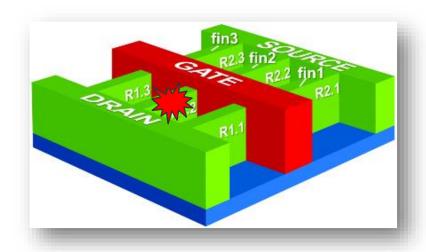

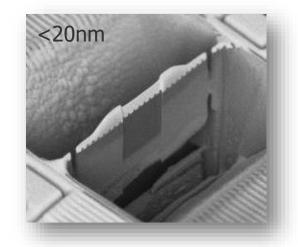

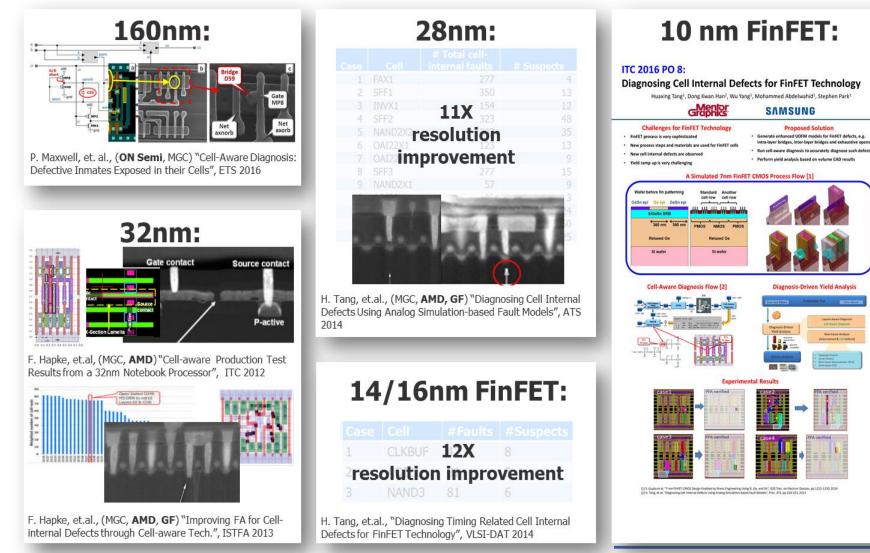

# **FinFET Requires More from Diagnosis than Planar**

Accelerated critical dimensions

Defects cause timing failures

TEM 1-shot PFA

Increased number of cell related failures

Diagnosis must consider intra-cell transition faults Requires diagnosis resolution of one transistor

#### **Tessent Cell-Aware Diagnosis** transistor level accuracy and resolution

12 M.Knowles, Mentor A Siemens Business, EDPS 2018

# **SCAN DIAGNOSIS BASICS**

M18 nowles, Mentor A Siemens Business, EDPS 2018

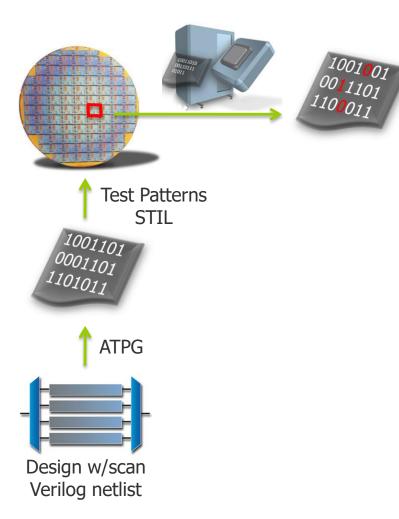

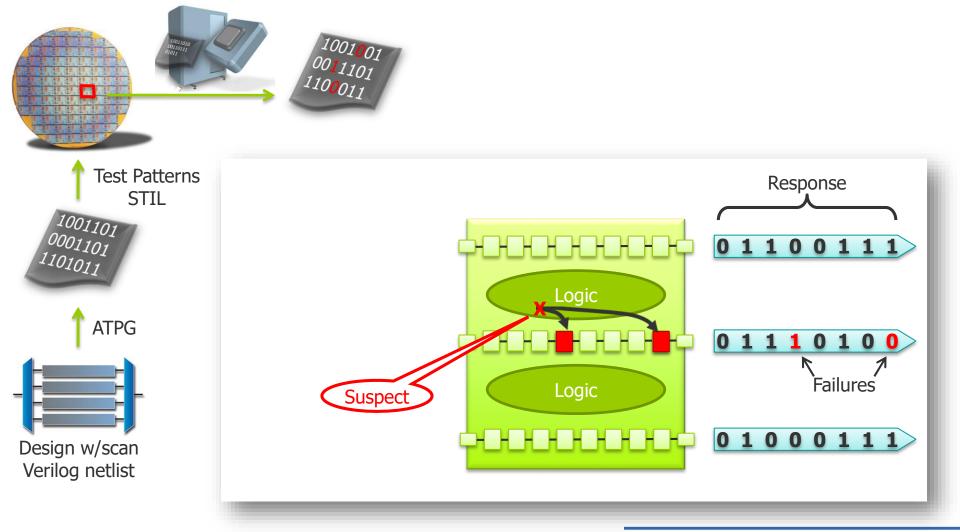

#### **Scan Test**

## Scan test: How most digital ICs are tested

15 M.Knowles, Mentor A Siemens Business, EDPS 2018

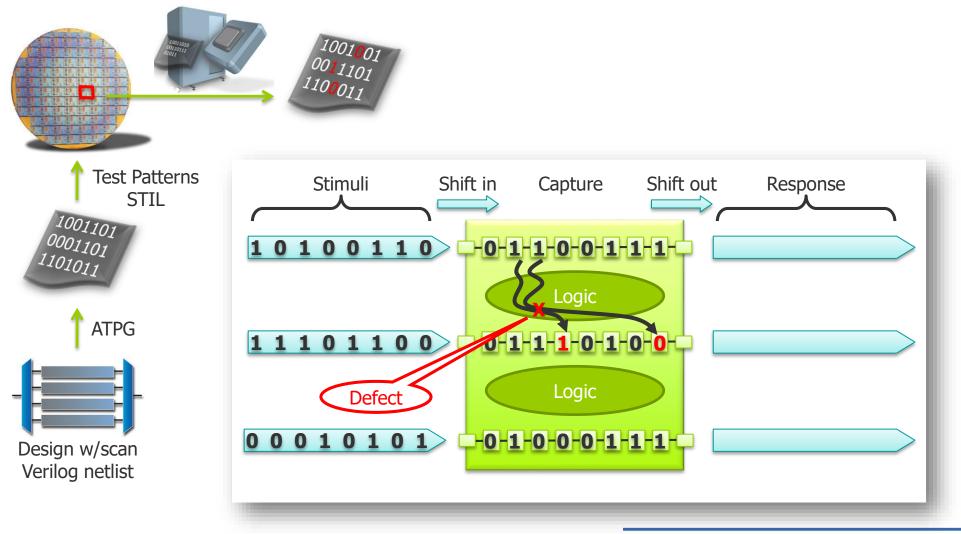

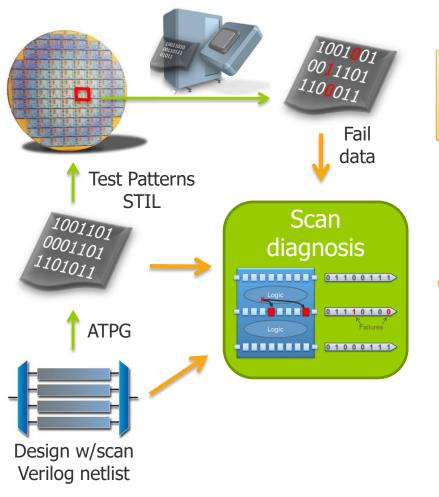

# Scan test diagnosis: Software-based defect localization

# Scan test diagnosis: Software-based defect localization

17 M.Knowles, Mentor A Siemens Business, EDPS 2018

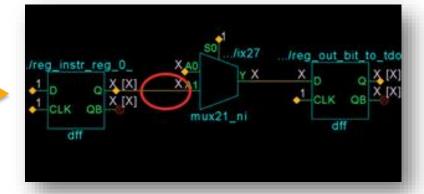

# **Traditional Scan Diagnosis**

| suspect score fail_match pass_mismatch type value pin_pathname cell_name<br>1 100 164 0 OPEN/DOM both /a0/m 1/m 55/B NR2M2D | <pre>#symptoms=1 #suspects=4 CPU_time=21.39sec fail_log=fail1 #failing_patterns=164, #passing_patterns=99 symptom=1 #suspects=1 #explained_patterns=164</pre> |                   |                 |                    |      |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------------------|------|--|

| 1 100 164 0 OPEN/DOM both /a0/m 1/m 55/B NR2M2D                                                                             | suspect score fail                                                                                                                                            | _match pass_misma | atch type value | pin_pathname cell_ | name |  |

|                                                                                                                             | 1 100 164                                                                                                                                                     | 0                 | OPEN/DOM both   | /a0/m_1/m_55/B NR  | 2M2D |  |

#### Logic location (net and cell name)

- Identifies logical failure and type Nets can be long Bridges might be unlikely due to physical proximity

- Poor classifications for yield analysis

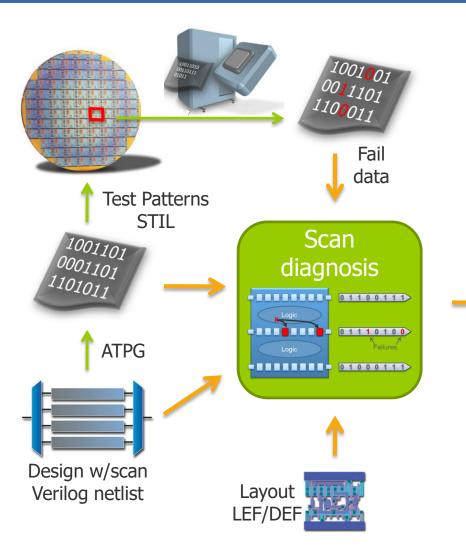

# Layout-Aware Scan Diagnosis

- Improves resolution

- Physical call-outs provide valuable classifications for yield analysis

- Reduced suspect area accelerates failure analysis (FA)

Diagnosis-Driven Yield Analysis

# WHAT IS NEEDED?

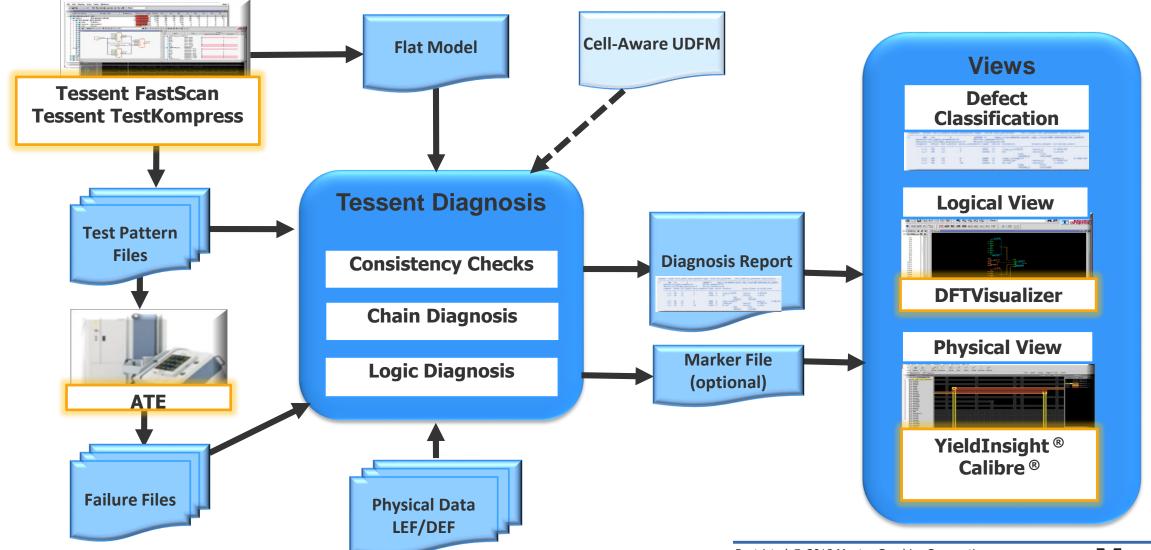

# **Tessent Diagnosis Collateral**

# Scan Diagnosis Input Requirements

- Logical design data

- Design netlist/data

- ATPG settings and constraints used to generate the test patterns

- Scan Patterns

- Cycle-based scan pattern formats WGL or STIL

- Pattern-based scan format ASCII

### Failure file (log) formats

- Cycle based failure log for cycle-based patterns

- Pattern based failure log for pattern-based format

- STDF (v4-2007) supported via DlogUtil converter tool

- Physical design netlist

- LEF and DEF for design

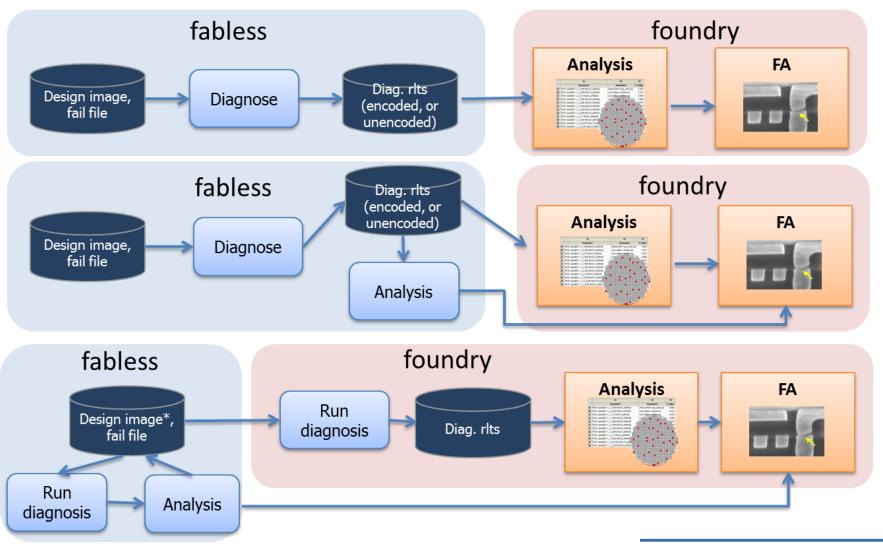

# Proven Data Flows...one size does NOT fit all

# **Foundry Successes**

"Diagnosis-driven yield analysis is an **established yield-learning methodology** at GLOBALFOUNDRIES for **test chips** as well as for yield ramp of **customer products**" TDF 2011

"The diagnosis resolution for cell internal defects is improved by **11.3X** on average" ATS 2014 "RCD determine **the underlying root causes** represented in a population of failing devices from **test data alone**" IEEE D&ToC, 01/12

"Mentor and Samsung are also leveraging production test diagnosis by exchanging information between the Tessent tools and the Calibre Pattern Matching facility to **quickly identify and eliminate design-specific yield limiting features** during design ramp up." Press release 2012

"The use of design layout information during diagnosis ... directly results in more die becoming suitable for PFA" ISTFA 2011

"Our experience shows that using scan **chain diagnosis** ... PFA hit rate is over **80%**." ATS 200

SAMSUNG

"Fixing this problem **improved baseline yield about 8%**. It is impossible ... with the traditional method." ElectroIQ, Nov 2011

"Layout-aware diagnosis ... directly translates into **improved FA success rates** and turnaround time." EDFA, 5/2010

Restricted © 2018 Mentor Graphics Corporation

#### Recognition

"The addition of DFM-aware yield analysis helps us and our customers to separate design-and process-related yield limiters, and reduces the time to find the root causes of yield loss. We can also use the technology to optimize DFM rules to address specific customer needs."

- Thomas Herrmann, MTS product engineer, **GLOBALFOUNDRIES**

"Using the statistical analysis features of Tessent YieldInsight we are able to identify yield issues in days as well as determining the impact of process modifications."

- Davide Appello, Design-to-Test Engr. Manager, **STMicroelectronics**

"We have found that Mentor's unique chain and at-speed diagnosis capabilities accurately diagnose failing die and can effectively pin-point problem areas within the die, even when the problem is internal to a cell, which is very important for physical failure analysis."

- Shauh-Teh Juang, Sr. Director of Design Infrastructure Marketing, TSMC

"By incorporating critical area analysis (CAA) and volume scan test diagnosis in our yield analysis process, the physical failure analysis cycle time is significantly reduced and the impact of each PFA is significantly higher, allowing us to take faster corrective action."

- Kyu-Myung Choi, VP Infrastr. Design Center, System LSI Division, Samsung Electronics

# Conclusions

- Leading edge process nodes challenged by new levels of in-cell complexity.

- Scan diagnosis provides unique, actionable information on systematic yield limiters, reducing PFA cycle time.

- Volume diagnosis can help avoid PFA and reduce costs.

- Where there's a will (value) there's a way.

Data sharing among fabless/foundry/tester is always a challenge and worth it to both fabless and foundry.

# **THANK YOU!**

M2Rnowles, Mentor A Siemens Business, EDPS 2018