## "Bala" Rajendran - CTO, EDA

- Part of global CTO office, focused on UDS product line for EDA vertical

- Joined Dell EMC from the customer side with 20+ years of experience in the EDA

- Before Dell EMC CAD Tools / Flows / Methodology / IP Management / M&A / Infrastructure / IT

- Post graduate degree in Material Science from India Institute of Science, Bangalore, India.

- Recent Conference Presentations

- 99.6% utilization on Cadence Palladiums CDN Live April 2018

- Peeling the onion on storage DAC June 2018

- Machine Learning in System Design and EDA IEEE Symposium Sept 2018

- Storage Aware Grid SC Nov 2018\*

- Annoyingly persistent!

2 of Y

# Agenda

| _       |     |   |

|---------|-----|---|

| <br>Pre | mis | e |

- Basics

- What do we know

- ☐ Identify problems to solve #1 and #2

- Where do we start #1 and #2

- ☐ Discussion on problems to solve

- ☐ Recommended reading / courses and playgrounds

- □ Q&A

3 of Y

**D&LL**EMC

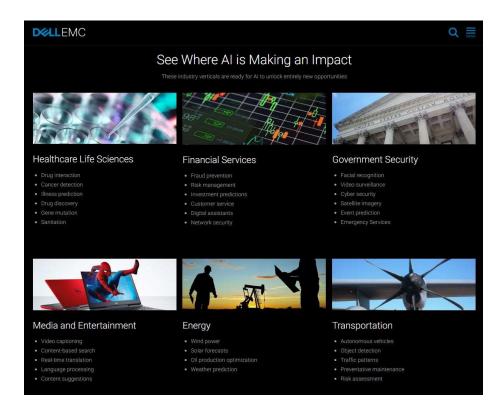

### **Premise**

- Almost every industry out there is using AI.

- It is being used in improving yield in agriculture and farming

- Even being used to cure cancer and yet ...

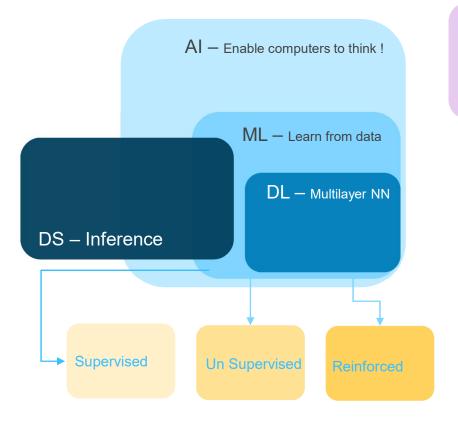

#### **Basics**

- Create a system that answers a question

- Question answering system is called a model

- The model is created via process called training

#### 7 steps of Machine Learning

- Gathering Data

- Preparing that Data

- Choosing a Model

- Training the Model

- Evaluation

- Parameter Turning

- Prediction

5 of Y

## What do we know

| Known Limitations |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | ML results are non-deterministic and EDA workflows needs consistent results not 99% accurate results Training data is the most important aspect of machine learning and there is a huge deficiency EDA tool vendors don't have enough data for to solve problems using machine learning algorithms With change in node and design requirements, the variables change thus making previous model unreliable |  |

| But               | that didn't stop ML techniques are being used                                                                                                                                                                                                                                                                                                                                                              |  |

|                   | Improve yield through wafer map failure diagnosis                                                                                                                                                                                                                                                                                                                                                          |  |

|                   | For equipment monitoring, tracking and process optimization                                                                                                                                                                                                                                                                                                                                                |  |

|                   | Generate interconnects for new SoC                                                                                                                                                                                                                                                                                                                                                                         |  |

|                   | P&R                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                   | Being investigated on system design, verification and project management                                                                                                                                                                                                                                                                                                                                   |  |

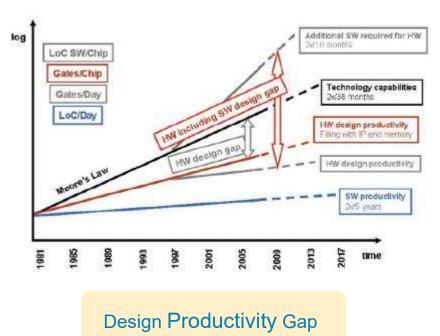

## Identify problems to solve #1

- Published in 2009 by ITRS (International Technology Roadmap for Semiconductors)

- Several EDA tool areas have made significant improvements in designer productivity and support larger dataset sizes - e.g., analysis-driven optimization algorithms, multi-threaded and distributed algorithms.

- Alas, the EDA productivity gap is still present a factor of 10X improvement in throughput is needed.

The circuit capacity afforded by the Moore's Law pace of technology advancement was growing faster than the capabilities of EDA tools and flows to support the associated design complexity.

7 of Y D≎LLEMC

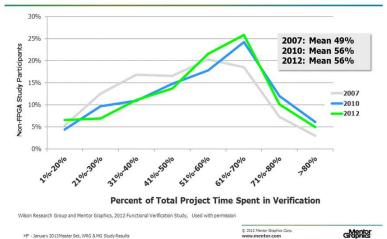

## Identify problems to solve #2

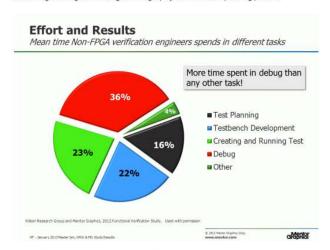

#### **Effort and Results**

Percentage of Non-FPGA total project time spent in verification

Verification

#### Percentage of time verification engineers spends in various task

Next, let's look at the mean time verification engineers spend in performing various tasks related to their specific project. You might note that verification engineers spend most of their time in debugging. Ideally, if all the tasks were optimized, then you would expect this. Yet, unfortunately, the time spent in debugging can vary significantly from project-to-project, which presents scheduling challenges for managers during a project's verification planning process.

Figure 2. Average (mean) time verification engineers spend in various task

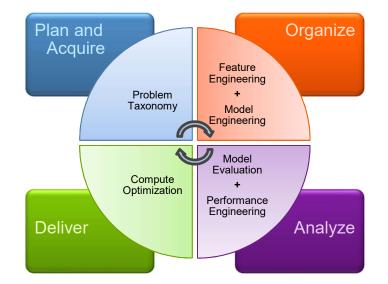

#### Where do we start #1

- Setup a team

- Ideally within CAD + Methodology + Infra team

- Continuous ML Model and Control Framework

- Start saving data

- Logs regression logs, simulation logs, system logs etc.

- System data resources, cores, licenses, storage etc

- Project data check ins, bugs, features, schedule slips etc

- Any other data that you believe needed to solve a problem

- Start small

- Define success and failure metrics

- Model gets better with time

- Iterate through different models / fine tune parameters

- Be aware of what ML cannot solve

- You cannot simply pour raw data into a general ML and expect something meaningful

- It is not magic ©

### Where do we start #2

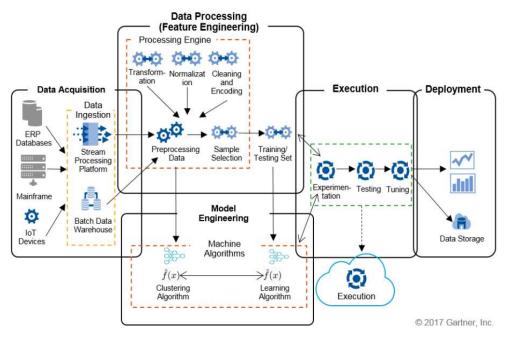

Architecture

- Infrastructure

- GPU based servers

- Dell EMC Al Ready Bundle : <a href="https://www.dellemc.com/ready4a">https://www.dellemc.com/ready4a</a>

**D**ELLEMC

#### Discussion on Problems to solve

Design Productivity Gap

Verification

- Grid Compute Infrastructure / Verification Engine / Test-bench Management System

- Resource Management -> Dynamically Alter Behavior

- Predictable Run times -> Predictable Design Times -> Predictable Deliverables

- Adaptive Build user smoke , PSCI and nightly regression

- Model to efficiently balance and saturate cores/licenses/storage/memory

- Pass rates -> Project Management -> Bug Tracking -> Schedule Confidence

# Recommended Reading / Courses / Playgrounds

| Cou   | ourses                                                                                    |  |  |

|-------|-------------------------------------------------------------------------------------------|--|--|

|       | http://www.andrewng.org/courses/ Andrew Ng                                                |  |  |

|       | Online courses @ Coursera, EDX and MIT                                                    |  |  |

| Books |                                                                                           |  |  |

|       | http://alex.smola.org/drafts/thebook.pdf Alex Smola : An Introduction to Machine Learning |  |  |

|       | http://neuralnetworksanddeeplearning.com/index.html Michael Nielsen Dec 2017              |  |  |

|       | https://cs.nyu.edu/~mohri/mlbook/ : Foundations of Machine learning, MIT Press            |  |  |

| Pla   | ygrounds                                                                                  |  |  |

|       | http://playground.tensorflow.org                                                          |  |  |

|       | https://ml5js.org/                                                                        |  |  |

|       | https://prodi.gy/                                                                         |  |  |

| Che   | eat Sheets                                                                                |  |  |

|       | https://github.com/kailashahirwar/cheatsheets-ai                                          |  |  |

12 of Y