#### VALIDATION, TESTING AND TUNING OF MIXED-SIGNAL/RF CIRCUITS AND SYSTEMS: A MACHINE LEARNING ASSISTED APPROACH

A. Chatterjee,

Georgia Tech

GRAs: S. Deyati, B. Muldrey, S.Akbay, V. Natarajan, R. Senguttuvan, S. Sen, R. Voorakaranam, S. Cherubal, P. Variyam, S. Chakrabarti, D. Han and X. Wang

Ack: SRC, Intel Corp, NSF and MARCO-DARPA

#### **Background: Mixed-Signal/RF Systems**

# Post-manufacture testing and tuning

#### **Machine learning**

Post-silicon validation

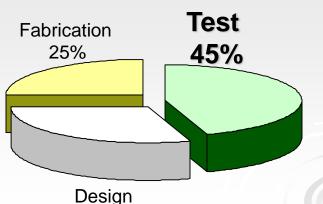

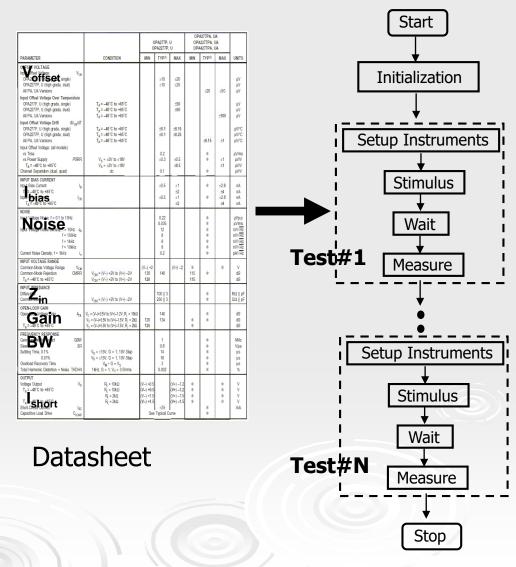

### State of the Art in Test: Mixed-Signal SoCs

- Specification Tests

- Each test requires a different setup

- Total testing time

- ATE complexity

- Load board complexity

- Test cost up 30%- 45%\*

30%

\*R. Tummala, Fundamentals of Microsystems Packaging, 2001.

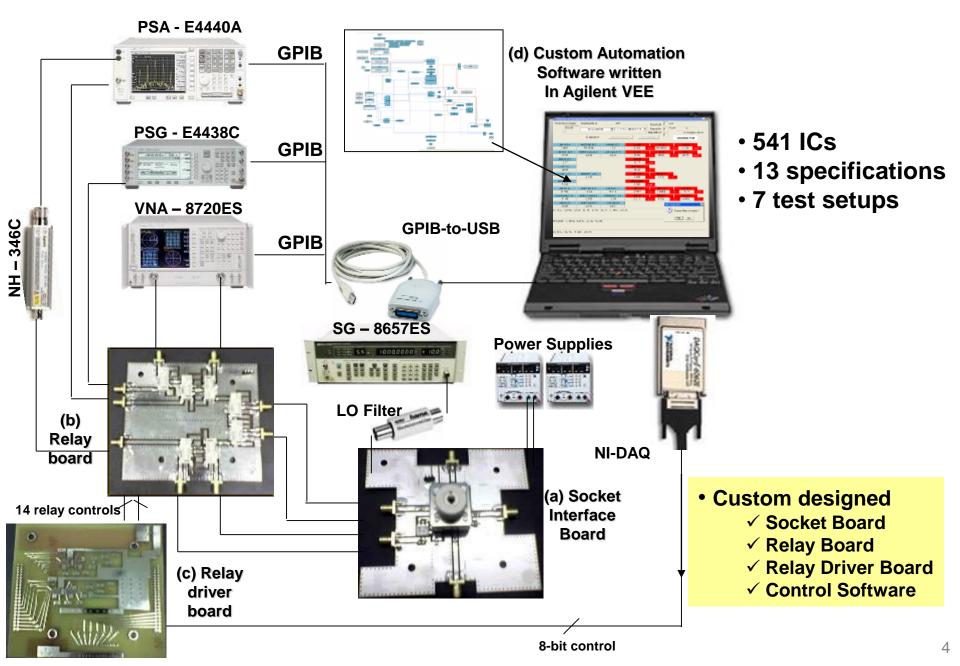

#### **Standard Specification Tests**

## Key Issues:

Manufacturing test time: Relay settling time (ms) >> actual test time (usec) ! Test multiple specs.

Built-in test of complex specifications: Difficult to place test instruments and circuitry onchip for multiple specifications !

Post-manufacture and field performance tuning: Tune *multiple* specs while minimizing power ? Need to tune devices *without extended test costs*.

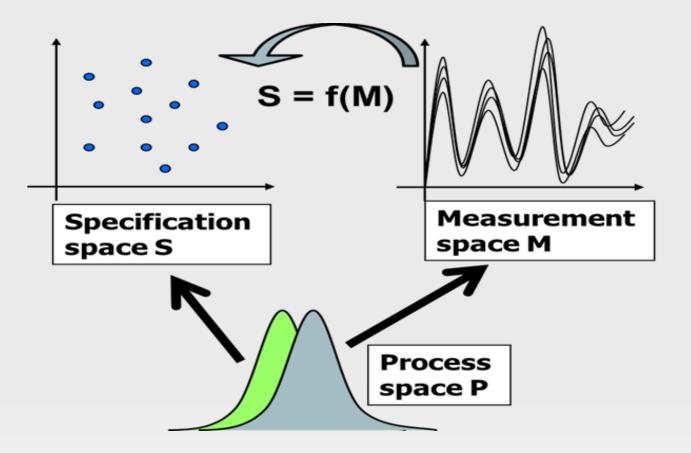

### Alternate Tests: Key Principles

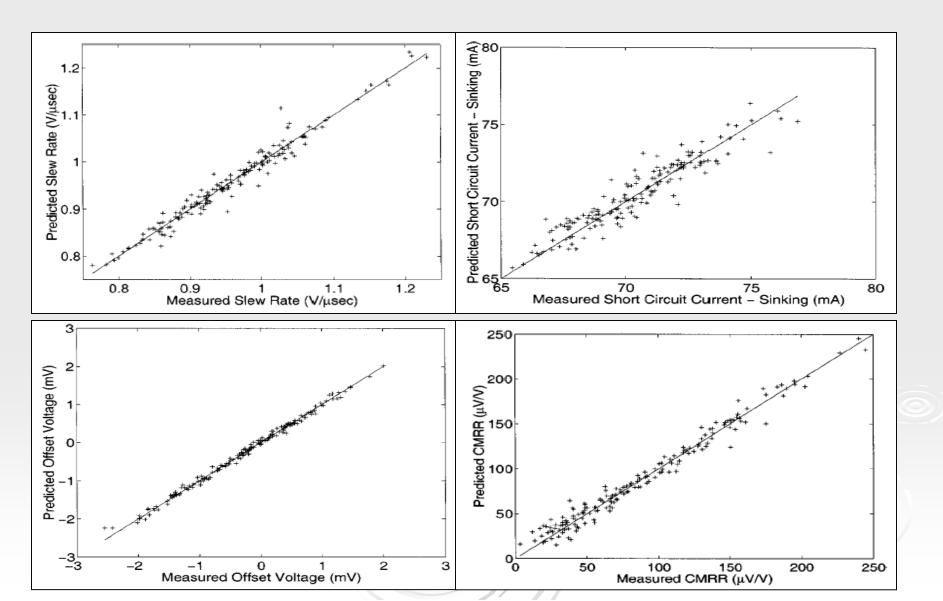

The mapping S=f(M) is derived using nonlinear regression (multiple adaptive regression splines: MARS)

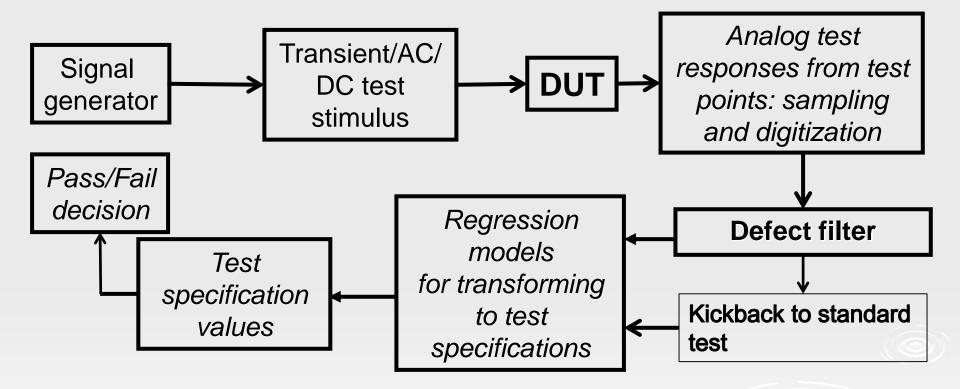

## Signature Test Methodology

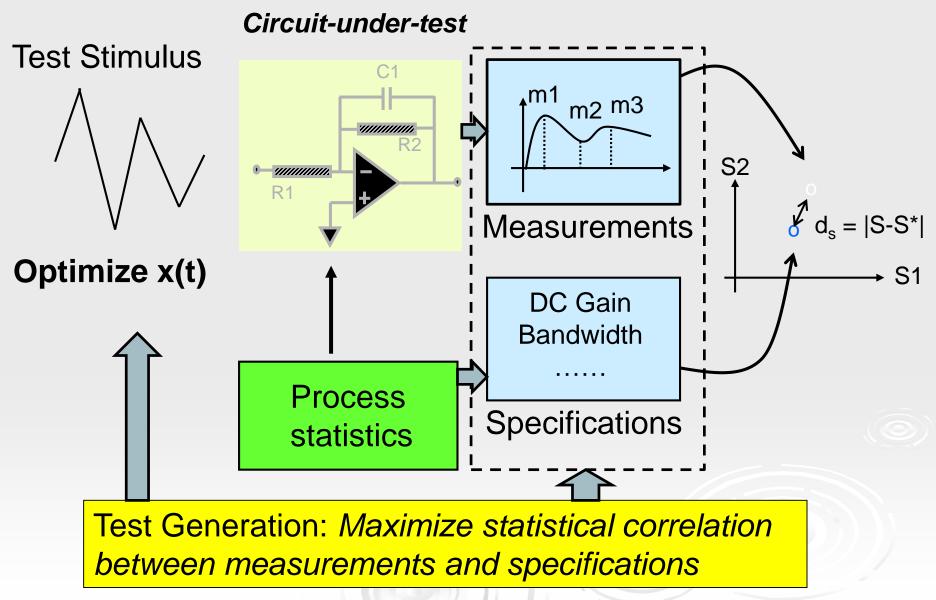

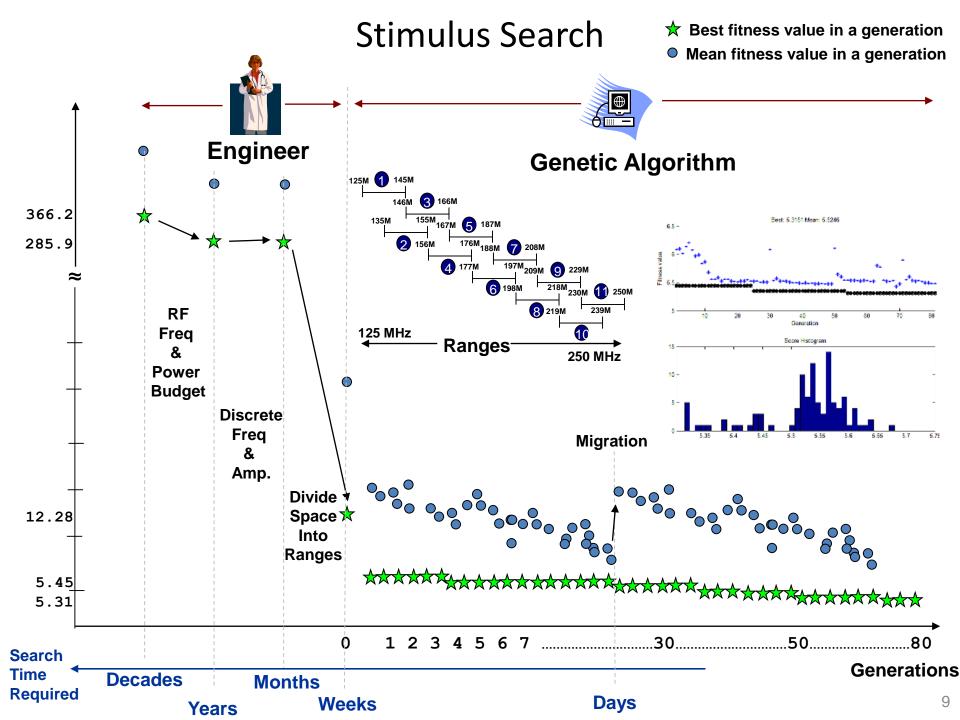

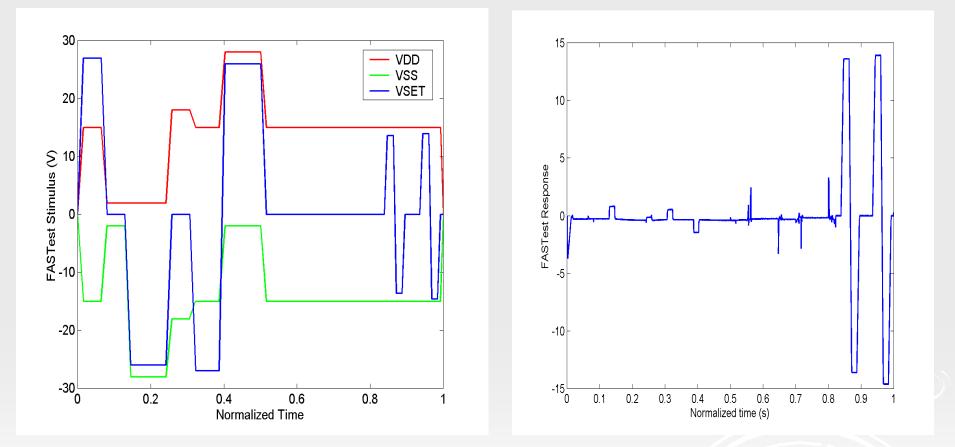

## **Test Stimulus Generation**

## **TI Precision Opamp**

#### >3X test time reduction

## **Alternate Test: Performance**

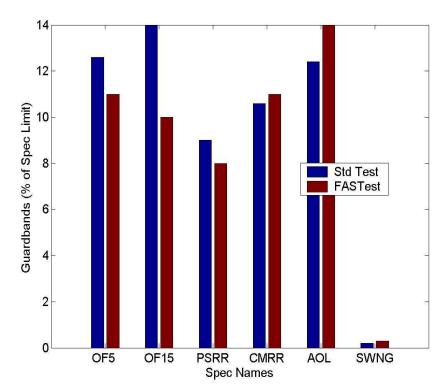

## Capability Study (Guardbands)

• For most specs, identical or better guardbands resulted

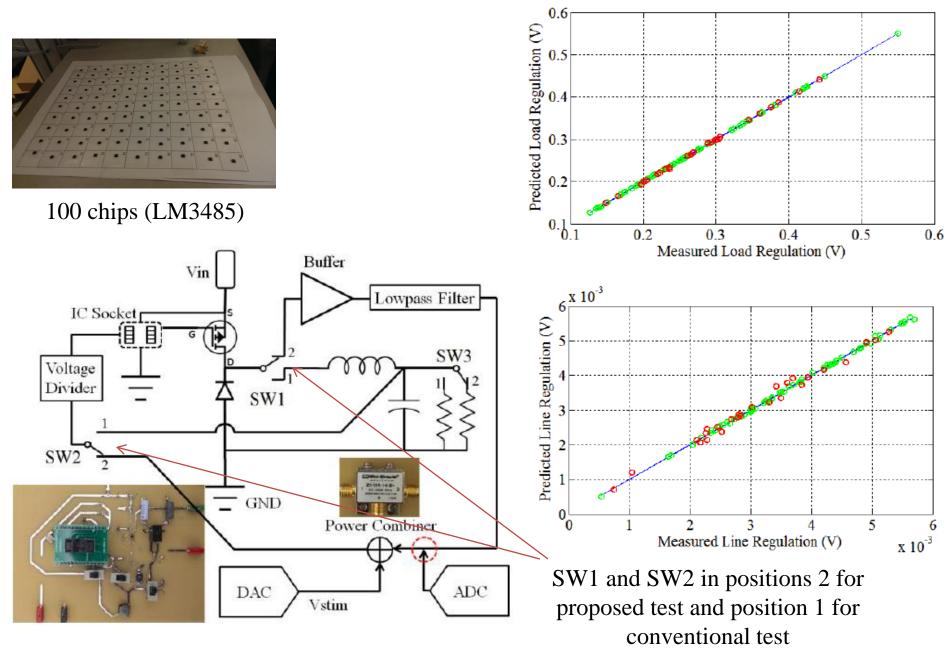

#### Hysteretic Buck Converter

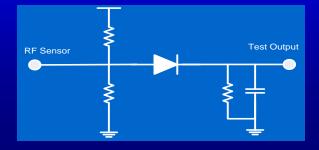

#### **Signature-BIST: Overview**

Ref: Variyam, Chatterjee, TCAD 2000

#### **Optimized Diagnostic Tests**

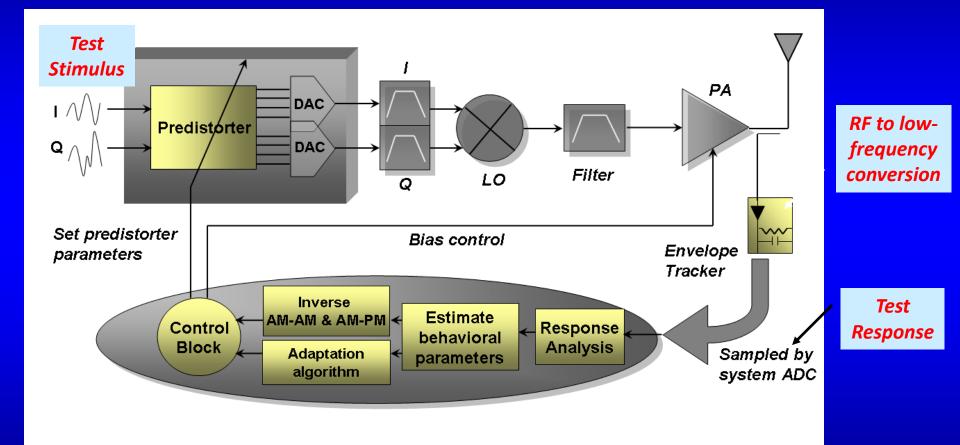

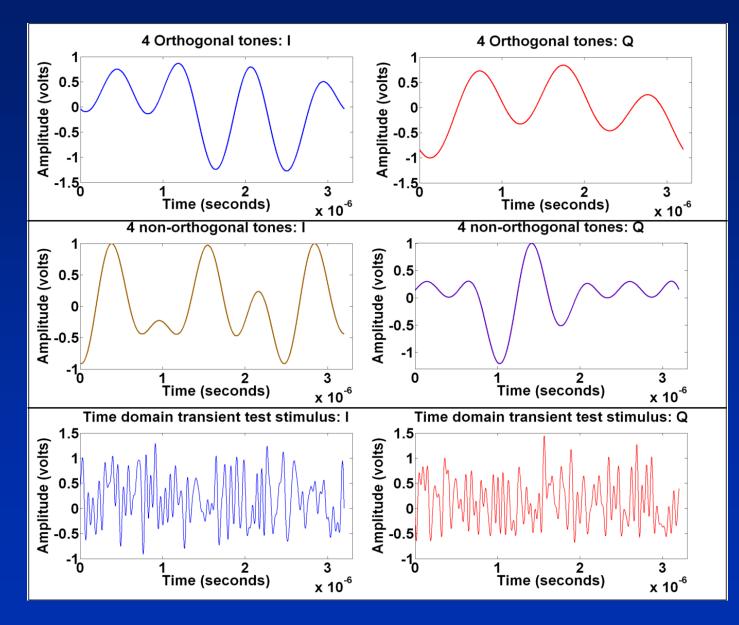

## Orthogonal tones

## Non-orthogonal tones

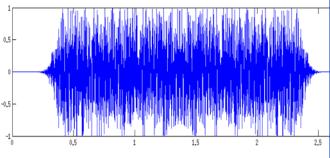

## Time domain test stimulus

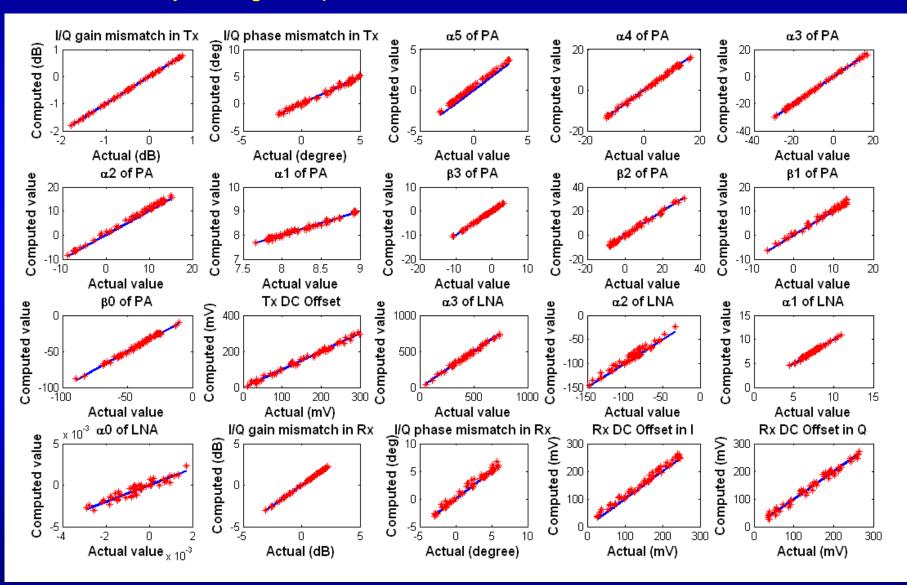

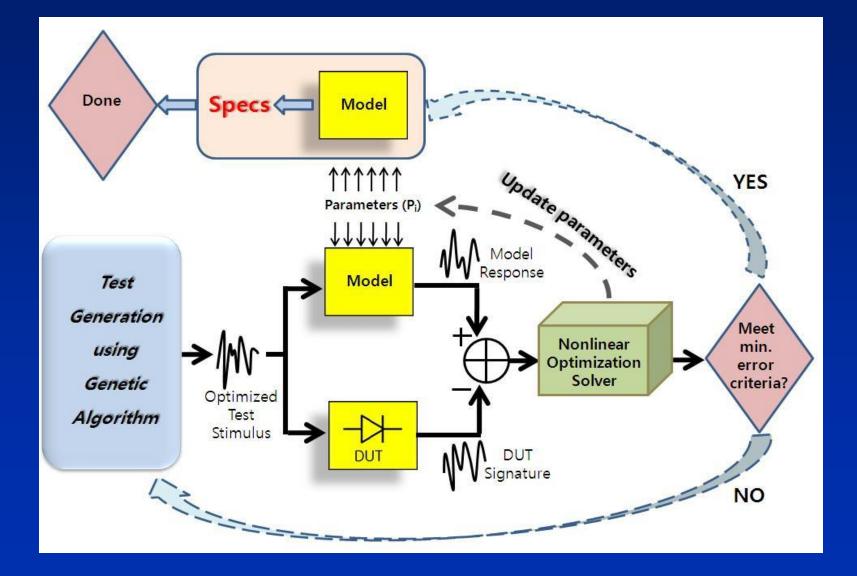

#### Signature Based Model Parameter Estimation

Ability to diagnose parameters of embedded modules !

## **Tuning: Learning Driven**

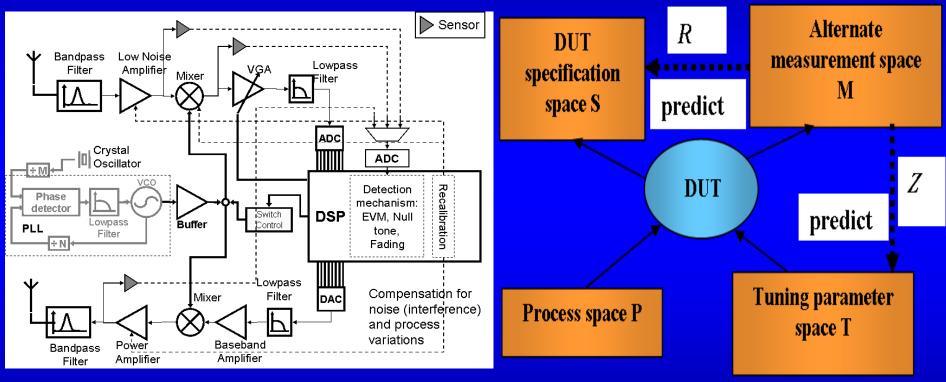

#### **Tuning Architecture**

#### **Supervised Learning**

- Ability to tune for multiple specs using *single data acquisition*

- Ability to perform *<u>near optimal tuning</u>*

- Minimal on-chip hardware overhead

## Learning driven tuning algorithms

Need accurate learning algorithms!

## Learning driven tuning algorithms

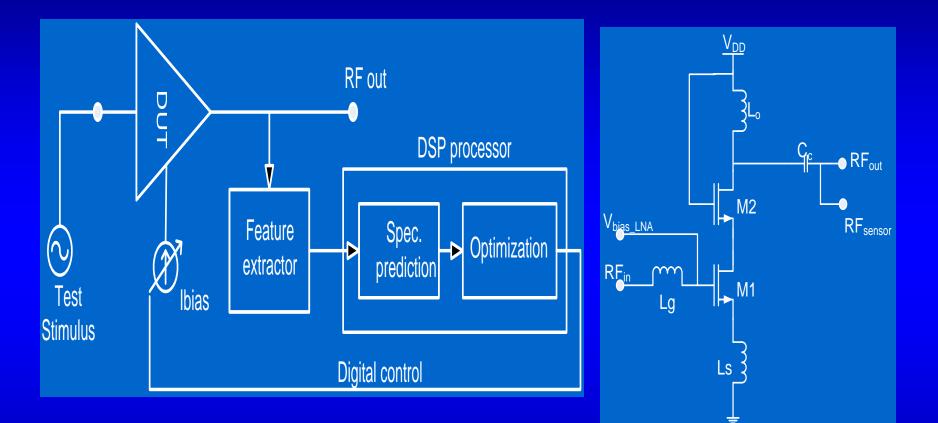

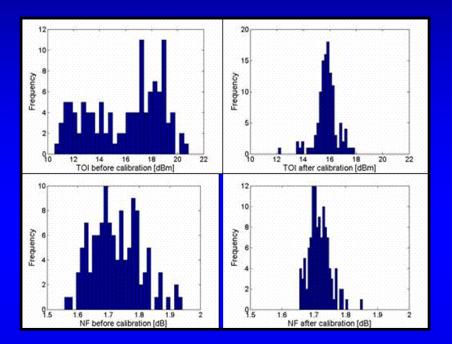

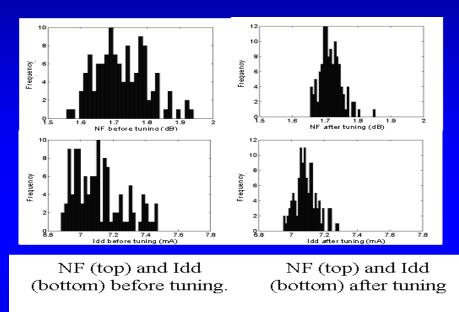

Self-healing LNA ! 70% to 99% yield

improvement

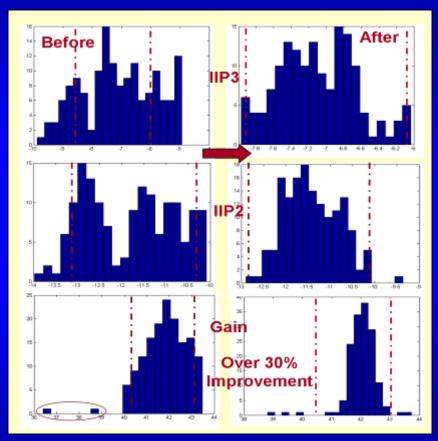

## Experimental Results: Full Receiver

**Nominal Specs**

| i tommu o beed    |           |       |         |  |

|-------------------|-----------|-------|---------|--|

|                   | Gain      | IIP2  | IIP3    |  |

| Nominal           | 42.5 dB   | -11.5 | -       |  |

|                   |           | dBm   | 7dBm    |  |

| Lower bound       | d 41.5 dB | -12.5 | -       |  |

|                   |           | dBm   | 8dBm    |  |

| Upper bound       | d 43.5 dB | -10.5 | -6      |  |

|                   |           | dBm   | dBm     |  |

| One-Instance (P1) |           |       |         |  |

|                   | Gain      | IIP2  | IIP3    |  |

| Before            | 40.1      | -10   | -5.3    |  |

| After             | 41.5726   | -11   | -7.2569 |  |

• 207 possible knob combinations (P1) for yield recovery

• Power conscious knob combination (P1) : 0.5724W

• Converged Knob combination (P1) : 0.5724W

## **Post-Silicon Challenges**

- Models for design bugs are not known a-priori and must be detected, learned and diagnosis

- Need to automate generation of bug models using learning algorithms

- Diagnosed bugs must eventually be mapped to physical design parameters

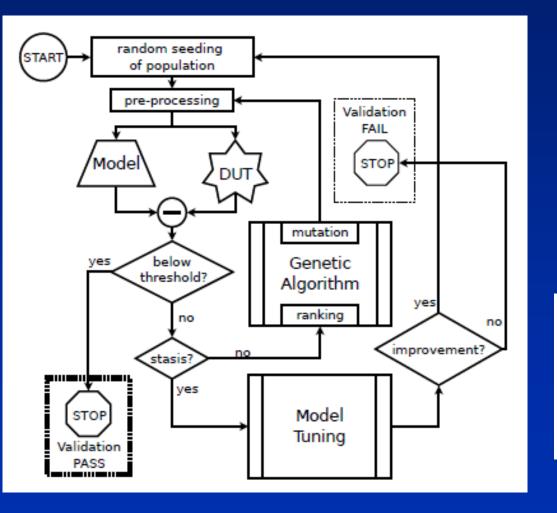

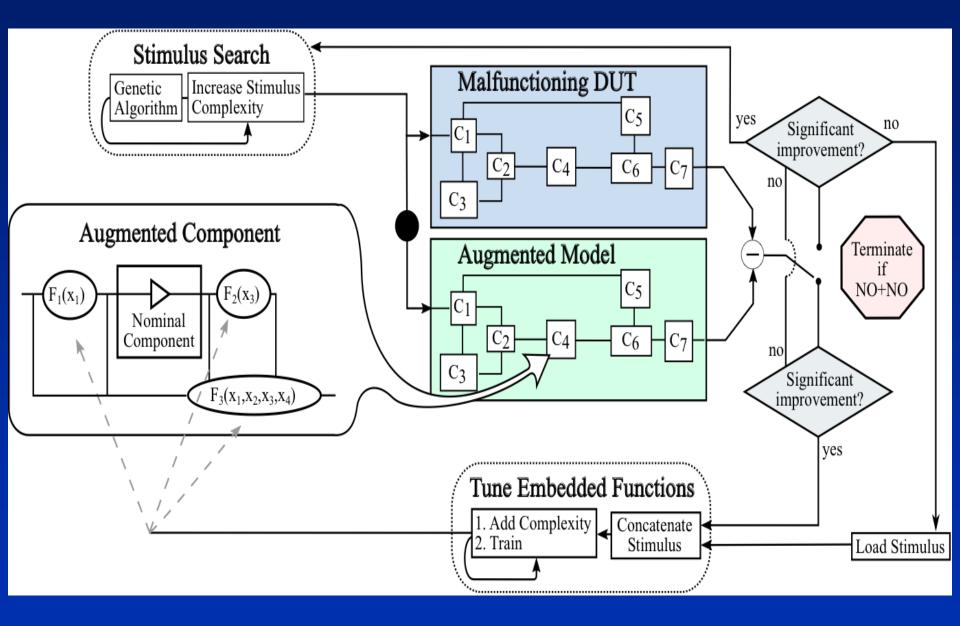

## **Model Tuning**

#### Test Stimulus Generation for Exposing Design Bugs

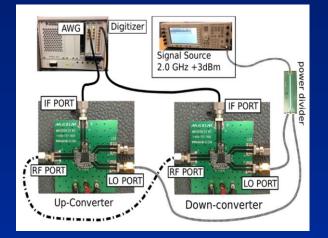

#### **Test setup**

**Best stimulus**

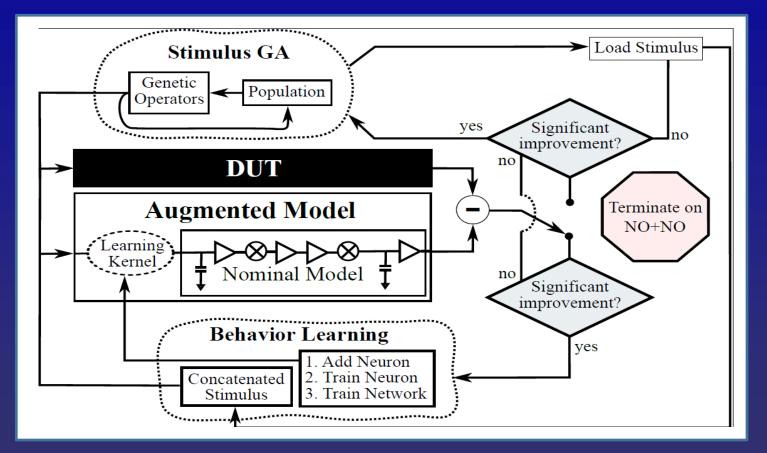

## **System Level Bug Learning**

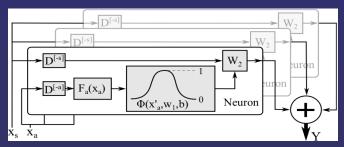

Sparse Weiner learning kernel

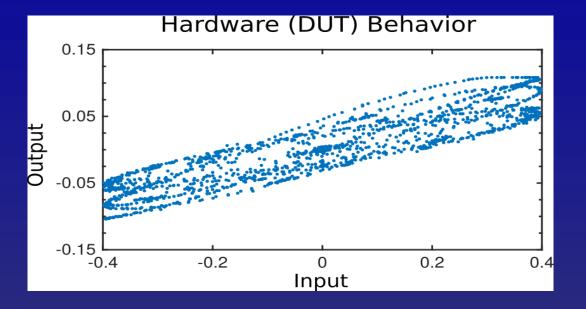

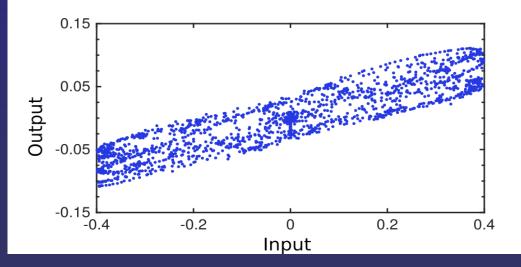

#### **Experimental Results: Maxim MAX2242 RF PA**

Model Behavior After Augmentation and Training

Captures hysteresis and memory effects automatically

#### **Diagnosis of Static Design Bugs**

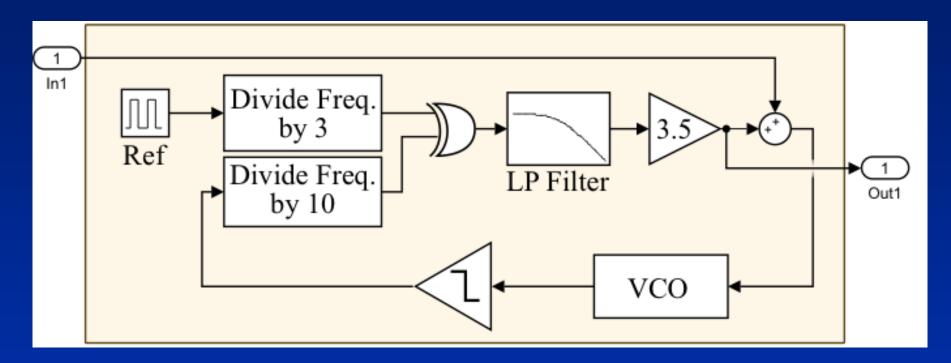

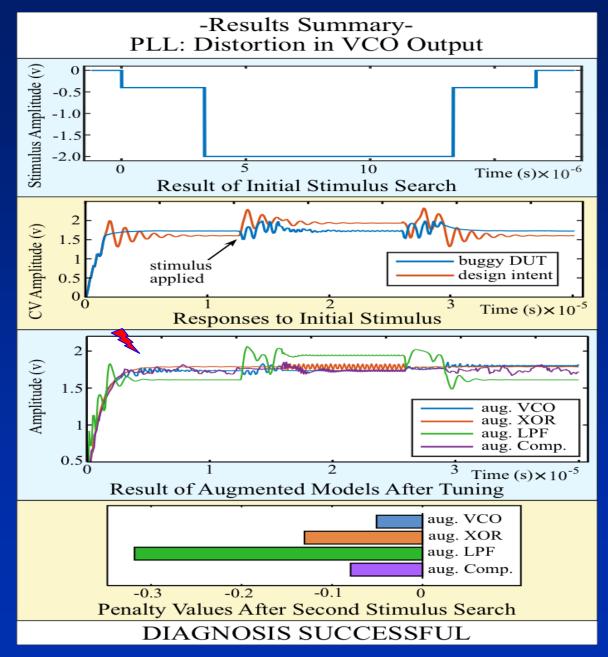

### **PLL Experiments**

- System stimulated by summing LP signal at VCO input

- System observed immediately prior to summing

### **PLL Experiment: Buggy VCO Output**

#### **Questions ?**