# Some Implications Brought In By The Coming Semiconductor Technologies

Dr. Antun Domic, CTO Synopsys, Inc.

#### Where Do We Stand & What Lies Ahead Lithography & Devices

#### Where Do We Stand ? What Lies Ahead ? Lithography & Devices

| ArF Immersion             |                                                                             |                                                                     |  |  |

|---------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| Mainstream at 7nm<br>SAQP | FinFET<br>Will stay until 3nm                                               | EUV                                                                 |  |  |

| 1D rules                  | No clear "heir" yet<br>Silicon nano-sheets and<br>nano-wires top contenders | Mainstream at 5nm<br>LE/LELE for M0/M1<br>2D rules temporarily back |  |  |

| GPU, CPU, NPU, TPU,       |                                                                             | APU, A&M/S<br>3D-IC (Active SI)                                     |  |  |

| 5.5D-IC (Passive          | SI/Substrate)                                                               |                                                                     |  |  |

#### Lithography Implications – ArFi, EUV, Applications Different Objectives Lead to Very Different Outcomes !

|          | Minimum<br>Metal<br>Pitch | Minimum<br>Contacted<br>Pitch | MMP × MCP            | MCP / MMP | Most<br>Advanced<br>Lithography |

|----------|---------------------------|-------------------------------|----------------------|-----------|---------------------------------|

| N10 (HP) | 36nm                      | 54nm                          | 1,944nm <sup>2</sup> | 1.5X      | SAQP                            |

| N7       | 40nm                      | 57nm                          | 2,280nm <sup>2</sup> | 1.425X    | LELELE                          |

| N10 LPE  | 48nm                      | 64nm                          | 3,072nm <sup>2</sup> | 1.333X    | LELELE                          |

| N7 LP    | 40nm                      | 56nm                          | 2,240nm <sup>2</sup> | 1.4X      | LELELE                          |

| N7 LPE   | 36nm                      | 54nm                          | 1,944nm <sup>2</sup> | 1.5X      | EUV                             |

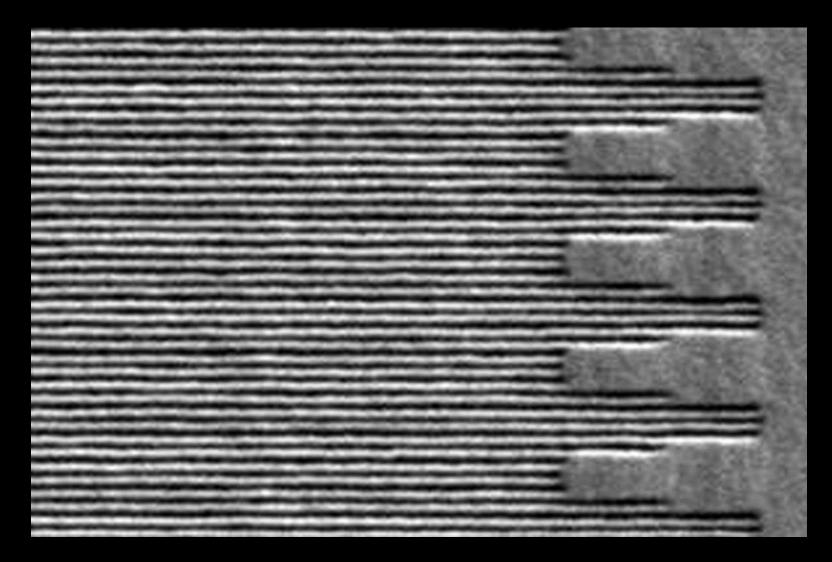

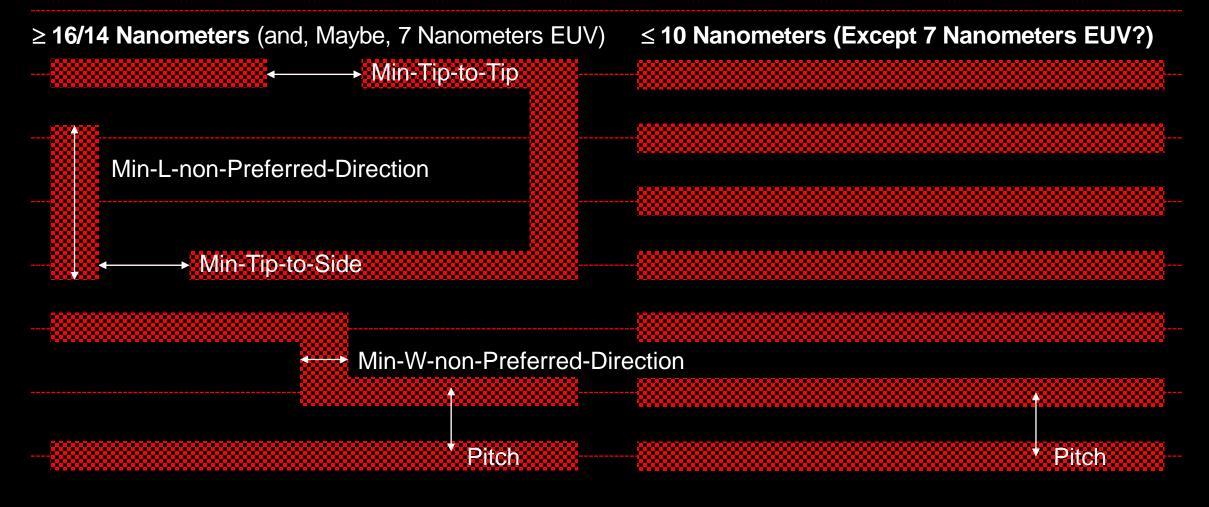

#### Lithography Implications – ArF Immersion, SAQP From 2D To 1D Rules, No Jogs, Only One Pitch/Width

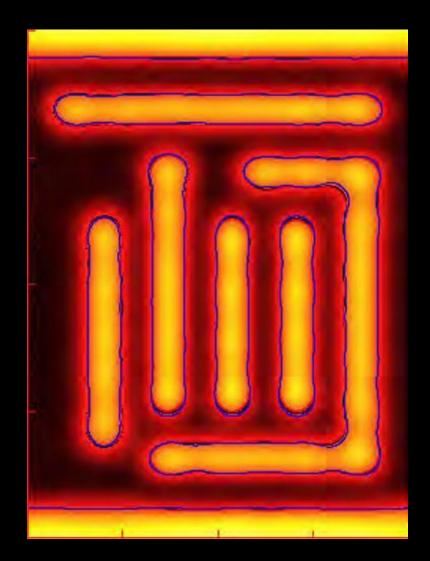

24 Nanometer Pitch, ArF Immersion, SAQP; Source: R. Brain et al., Intel, IEDM 2016

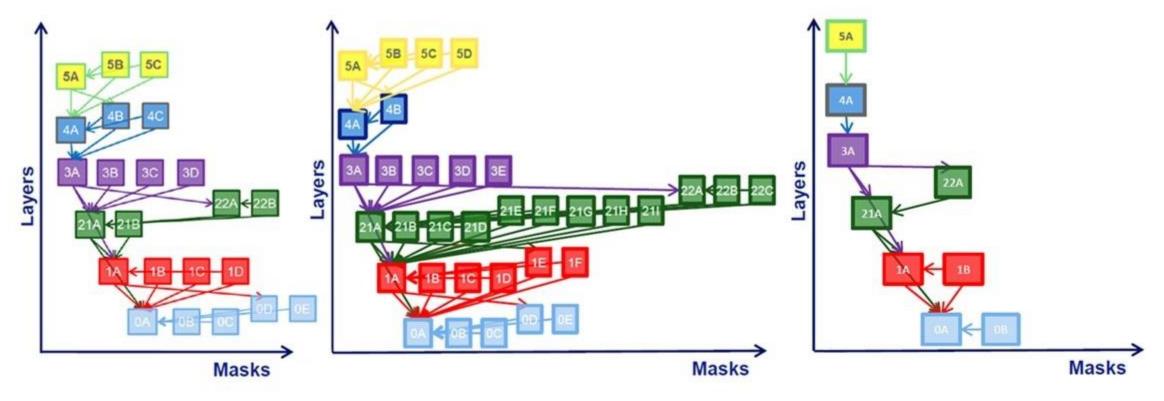

#### Lithography Implications – ArFi Vs. EUV # of Critical Lithography & Alignment Overlay Steps

| N10   | N7 ArFi | N7 EUV |

|-------|---------|--------|

| 23    | 34      | 9      |

| 36-40 | 59-65   | 12     |

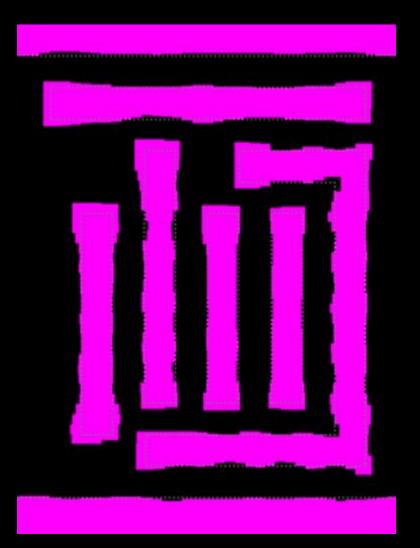

#### Lithography Implications – EUV Temporarily Back To 2D Rules At 7 Nanometers ?

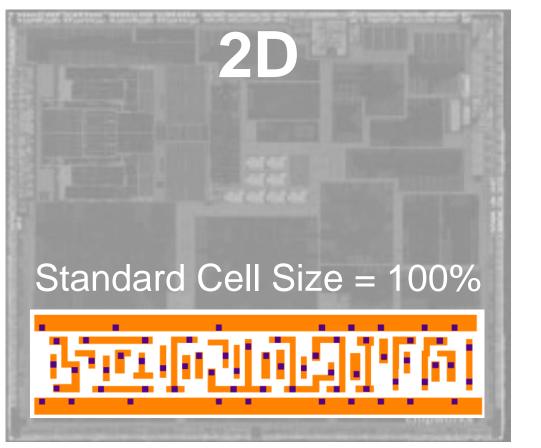

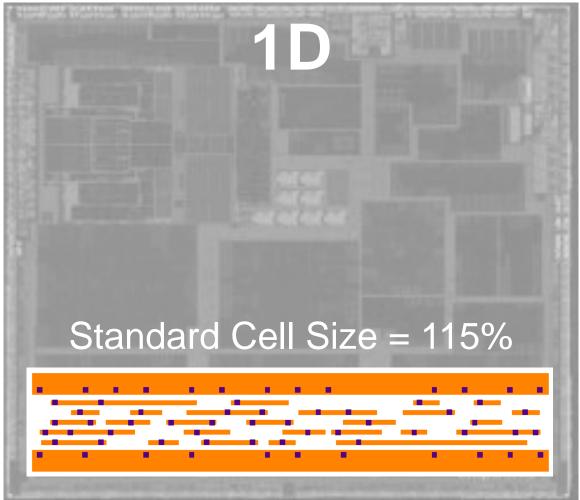

From 2D to 1D Routing AND Standard Cells No More Jogs, Tip-to-Tip, and Tip-to-Side Rules, Only One Pitch/Width

#### **Design Implementation At** ≤ **10 Nanometers** *From 2D To 1D Routing AND Standard Cells*

### Design Implementation At 7 Nanometers (70 Ångstroms)

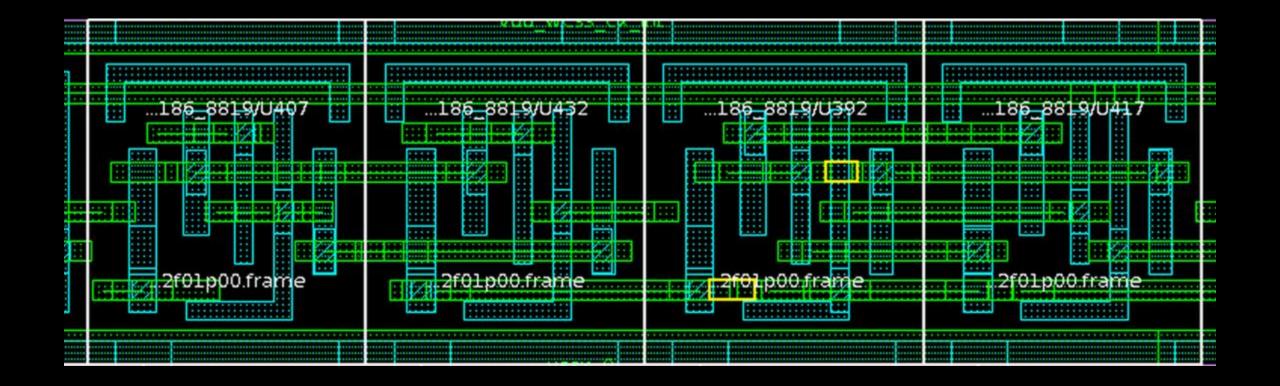

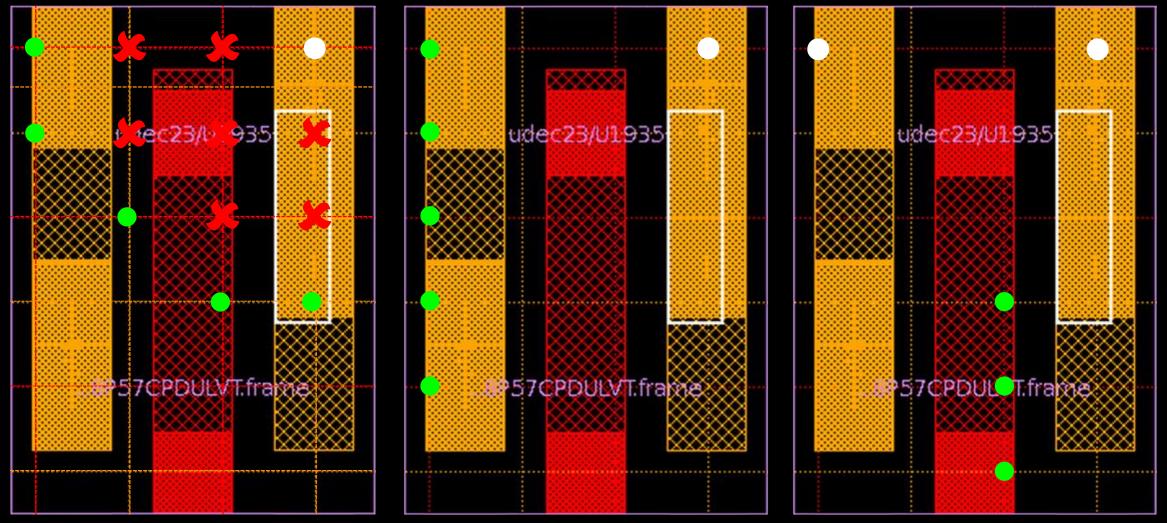

End-of-Line Rules Violations at High Pin Count Cell Consecutive Placement Areas When Pins Are Near Cell Boundary, Wire End Extend Beyond Boundary

Placement Must Align Near-by Connected Pins Vertically to Allow Direct Connection on M1, and Avoid Connected Pins in Neighboring Rows Being One Track Off

Vertical Pin Alignment-Aware Placement Reduces Routing Congestion

Placement Becomes Increasingly Restricted More and More White Space Is Required to Achieve Legality

|     |        | .pj/U1426 |      |     |      | 613 |       | 1    | 03   |      | 3       | 64   |        |    |

|-----|--------|-----------|------|-----|------|-----|-------|------|------|------|---------|------|--------|----|

| VOI | A      | AOI211D2  |      | OAI |      | OAI |       | ND   | 2    |      | AO      | I    |        |    |

| 01  |        | 87        | 11   | UAI |      | 290 |       | 287  |      |      | dpj/U14 |      |        |    |

| 878 |        | ND2       | 1    |     |      | OAI | N     | D2   |      |      | OAIZ    | 11D  |        |    |

|     | 976    | 561       |      |     |      | 611 |       | 572  |      | 56   | 580     |      | 58     |    |

|     |        | OAI       |      |     | NC   | )2  | OA    | 1    | OA   | line | ND2.    |      | ND     | 2  |

| AC  | DI     |           |      | 6   | 41   | 63  | 9     | 4    | 09   |      | .570    |      | dpj/U8 | 82 |

|     |        | (10       |      | OA  | I    | ND2 |       | ND   | 2,   | N    | D2      | 0/   | 12110  | 22 |

|     | 632    | 618       |      | 411 |      |     | 1     | 19   |      |      |         |      |        |    |

|     | OAI    | 1.01      |      | OAI |      |     | OA    | I    |      | 0    | AI211D. |      |        |    |

| 6   | 630    | AO1       | 62   | 3   | U1   | 5   | 916   |      | 315  |      |         |      |        |    |

| ND  | 2      |           | OAI  |     | OAI. |     | ND2   |      | ND2  |      |         |      |        |    |

| 3   | 354    | 308       | 70   | 7   | 56   | 9   |       | .567 | 8    | 12   | 810     | )    |        |    |

| ND  | 2      | OAI       | OAL  |     | OAI. |     | N     | ID2  | OA   | la.  | ND2.    |      |        |    |

|     | 740    | 306       | 15   | 1   | 29   | 9   |       |      | .729 |      | j/U     | 1026 |        |    |

|     | OAL. N |           | OAI. |     | OAI. |     |       | c    | )AI  |      | OAI2    | 11D  |        |    |

|     | 8      | 8870      | 5    | 297 |      | pj/ | J1017 | 2    | 093  |      |         |      | .250   |    |

####

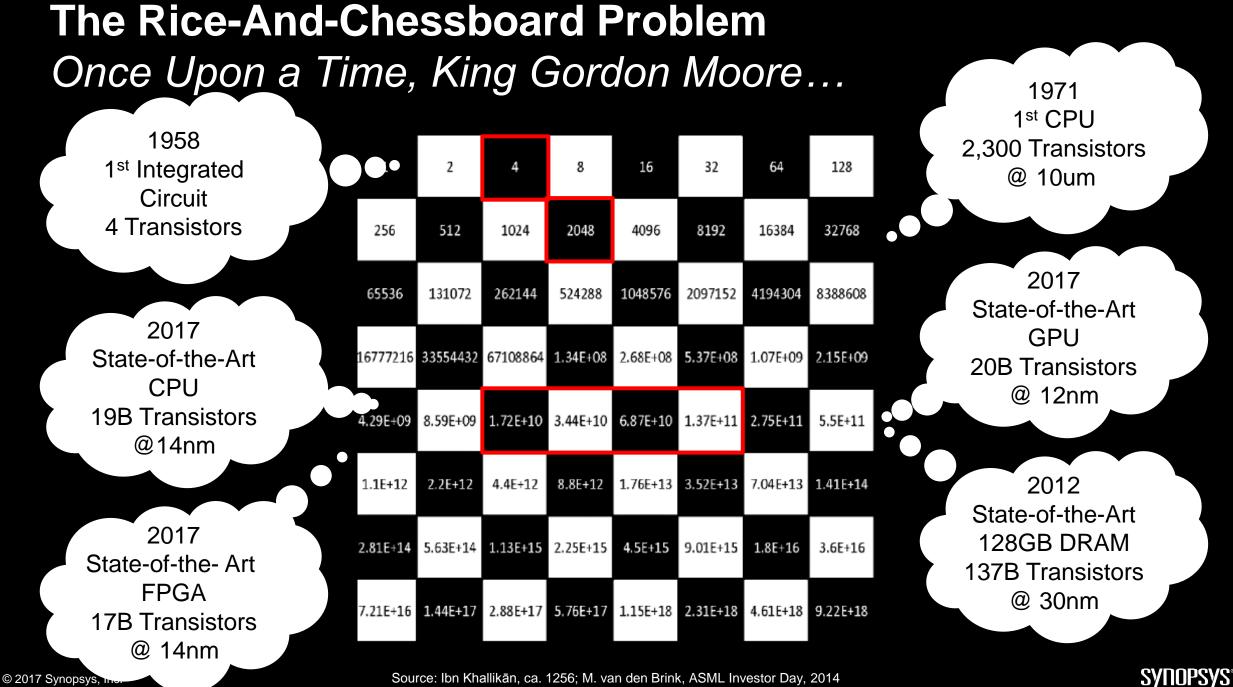

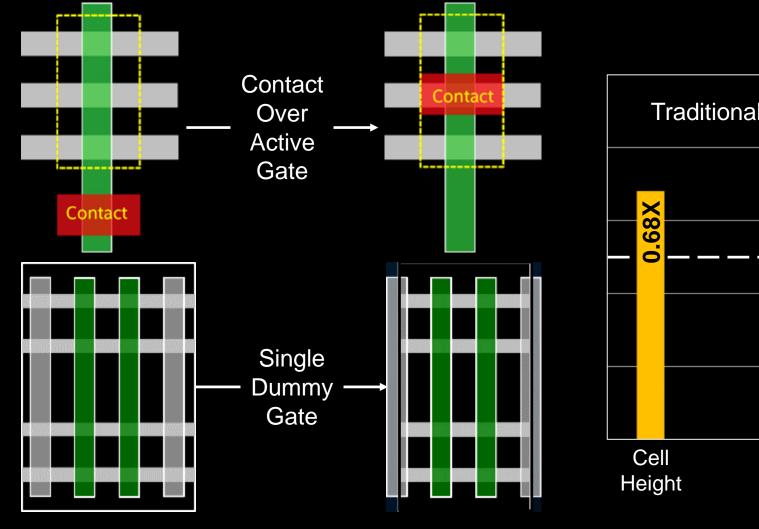

#### **Design Implementation At** ≤ **10 Nanometers** *Moore's Law Is Fueled by Single Bullet Weapons*

SYNOPSYS®

© 2017 Synopsys, Inc. 16 Source: M. Bohr, Intel Technology & Manufacturing Day, 2017

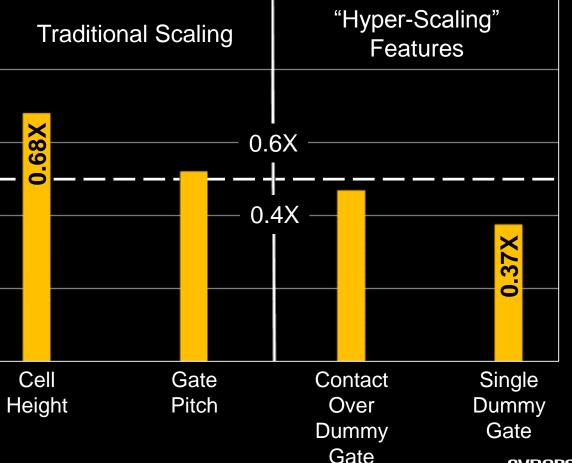

#### **Design Implementation At ≤ 10 Nanometers** *Caveat: Standard Cells Shrink, # of Pins Remain the Same*

5nm (5T)

(0.55x)

MP = 28nm GP = 48nm

A Nanometer... Tic-Tac-Toe: a 4x6 Grid, P&R Must Route 3 Pins, But... There Are Only 4 Simultaneous Legal Access Points (Via Spacing Rule  $\geq 2\sqrt{2}$  Grids)

Pins Density & Accessibility-Aware Placement Addresses/Mitigates Pins Density/Accessibility, and Routing Congestion Issues

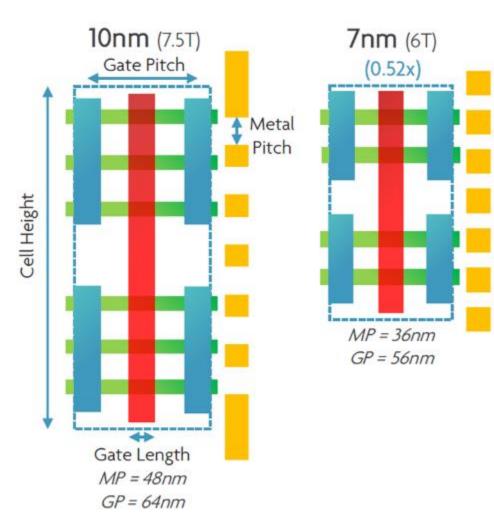

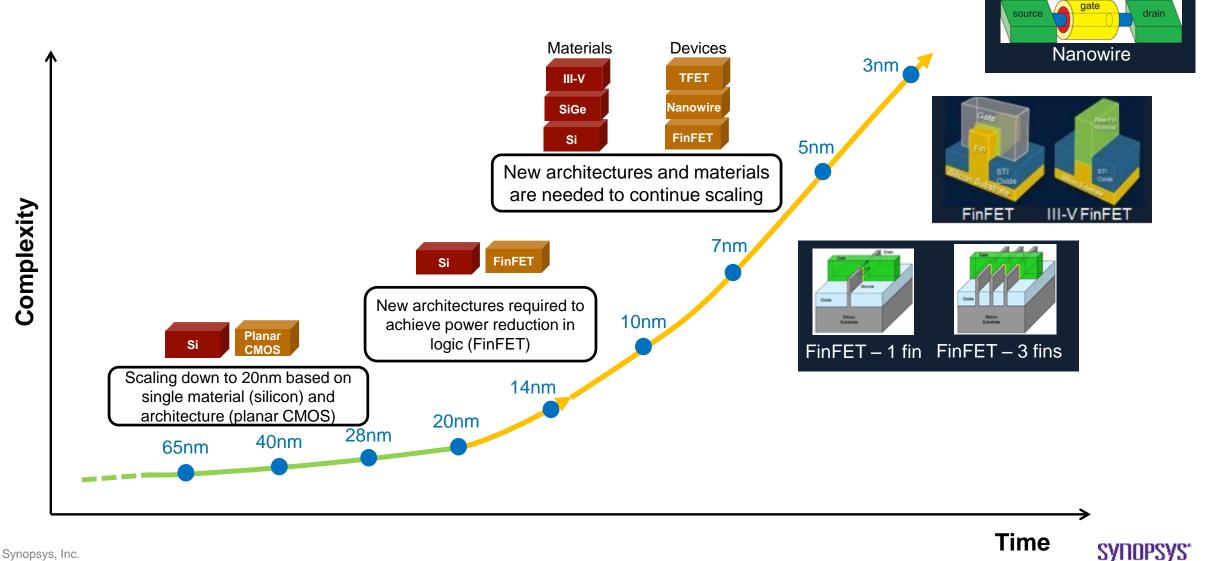

#### **Shrink Scenarios For Logic Devices** *No End in Sight*

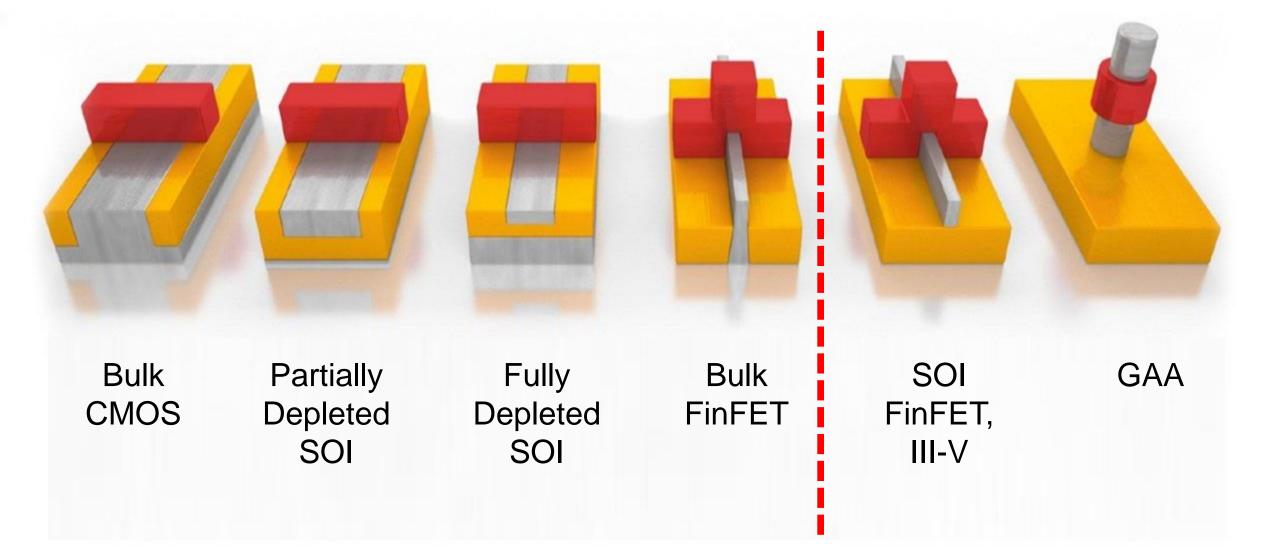

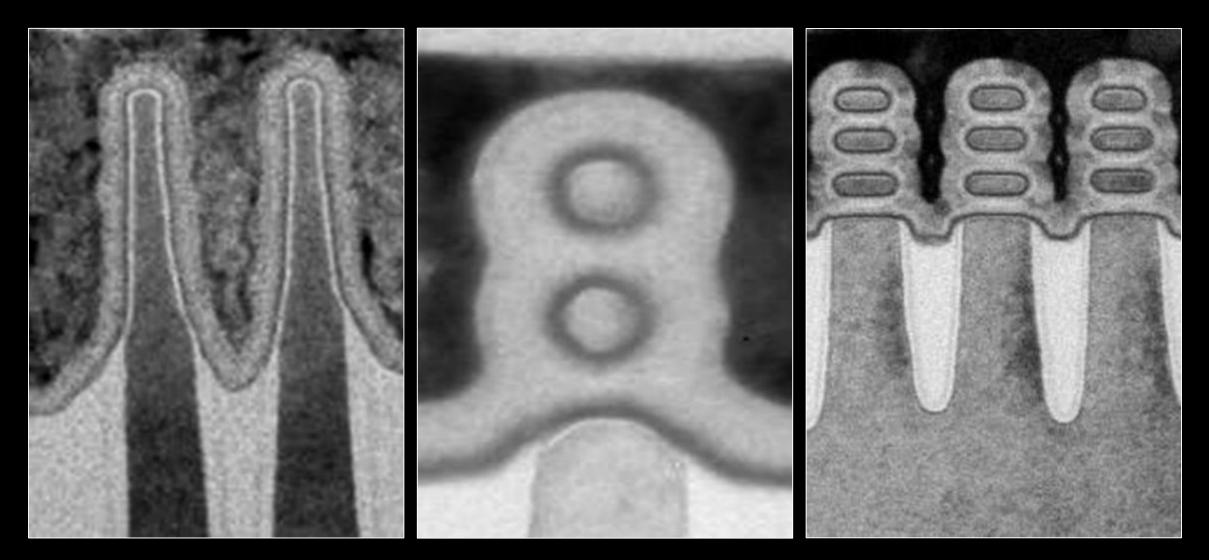

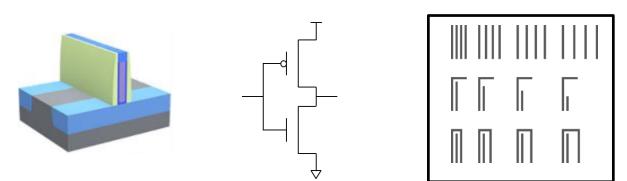

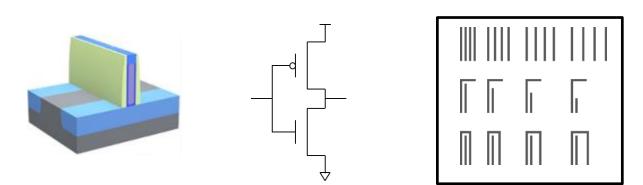

#### **Device Implications – Beyond FinFET (At 3 Nanometers)** [Stacked] Nano-Wires, and Nano-Sheets

Source: K. Mistry, Intel Technology & Manufacturing Day, 2017; IMEC Technology Forum, 2017; IBM, 2017

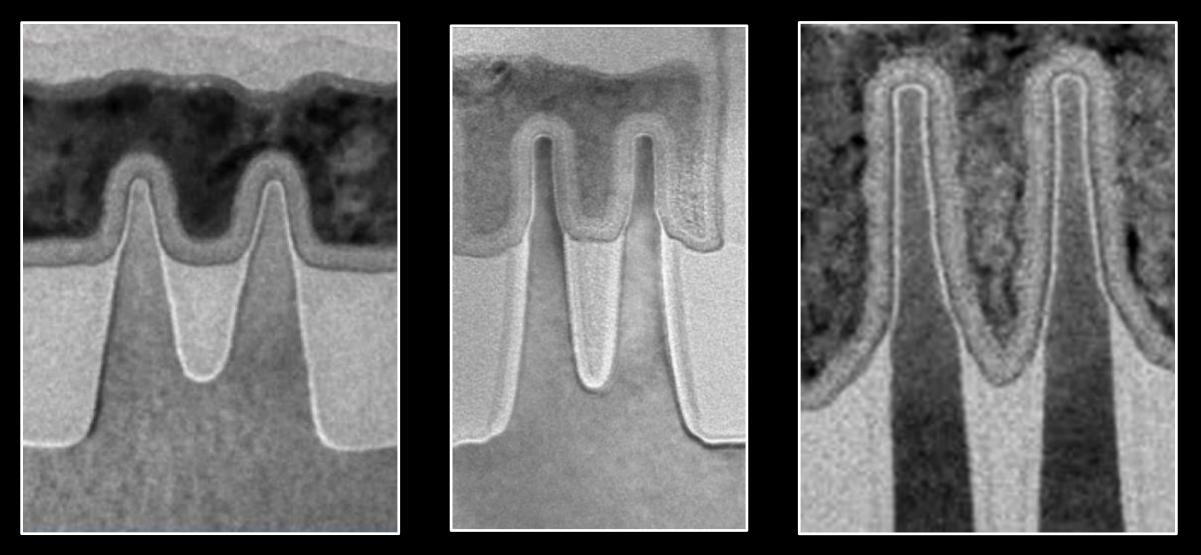

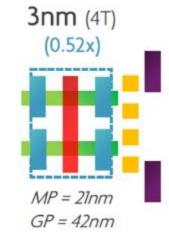

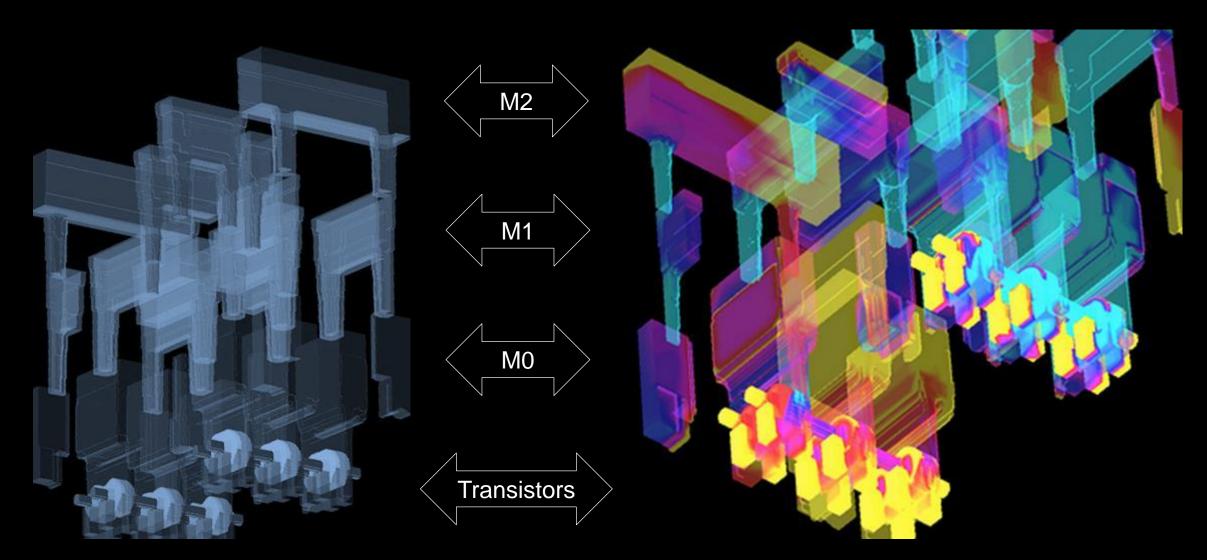

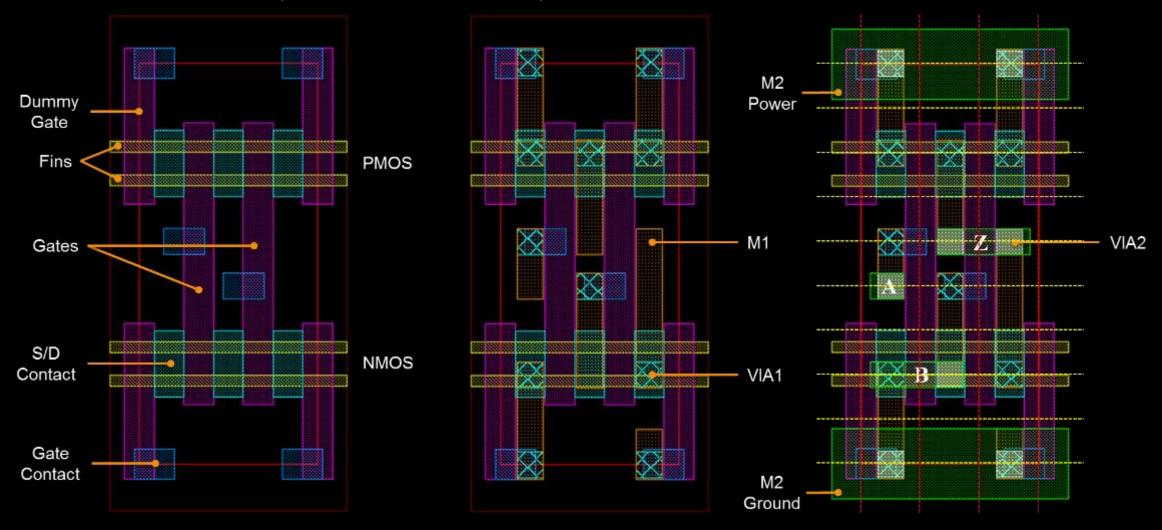

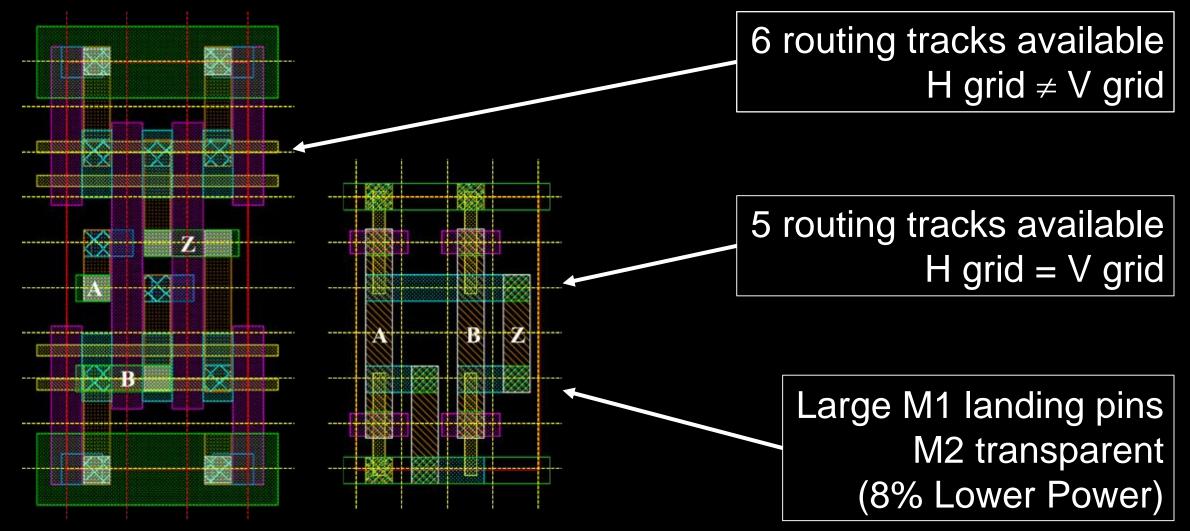

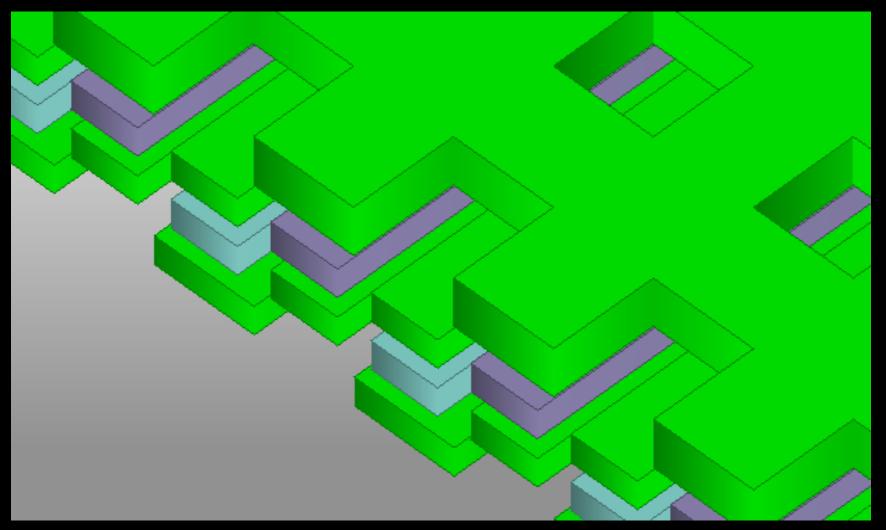

# Process Exploration At 5 Nanometers (50 Ångstroms)

2-Input NAND 3D Structure, and Current Flows

### **IP Exploration At 5 Nanometers**

#### 9-Track 2-Input NAND Layout Gate Pitch = 32nm, M1 Pitch = 24nm, Fins <u>Pitch = 18nm</u>

Source: V. Moroz, Synopsys, ISPD 2016

#### **IP Exploration At 5 Nanometers**

What If We Rotate The Fins ? 9-Track vs. 6-Track 2-Input NAND Layout Gate Pitch = 48nm, M1 Pitch = 24nm, Fins Pitch = 48nm

#### **The Number Of Material And Device Options Increases** Selection Of Optimal Solution Threatens Schedule

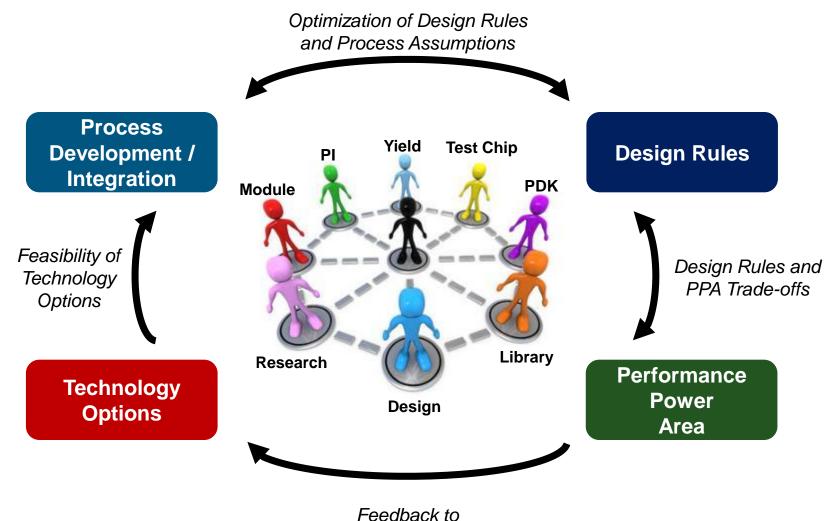

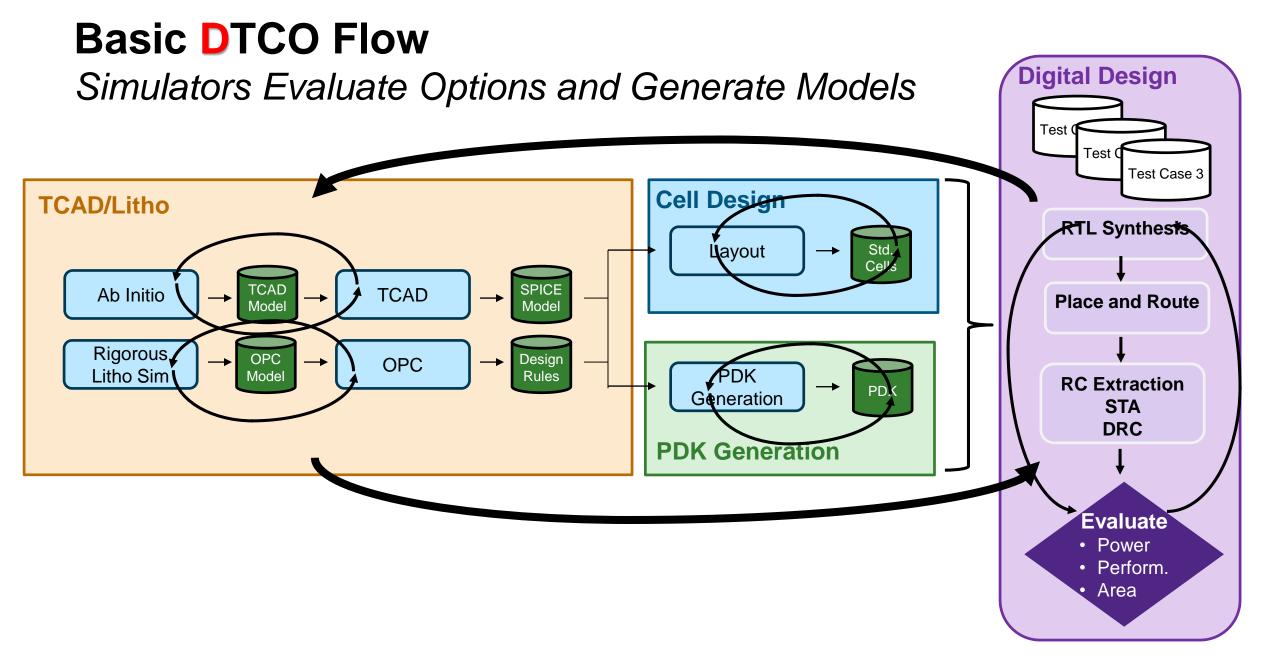

#### **DTCO Enables Landscape Exploration**

Introduces Use of Larger Circuits for Technology Assessment

Technology Research

⇒ Where Do We Stand & What Lies Ahead

Lithography & Devices

⇒ DTCO: Design And [Process] Technology Co-Optimization

#### **Evaluate Multiple Options**

Deliver a Competitive Technology as Quickly as Possible

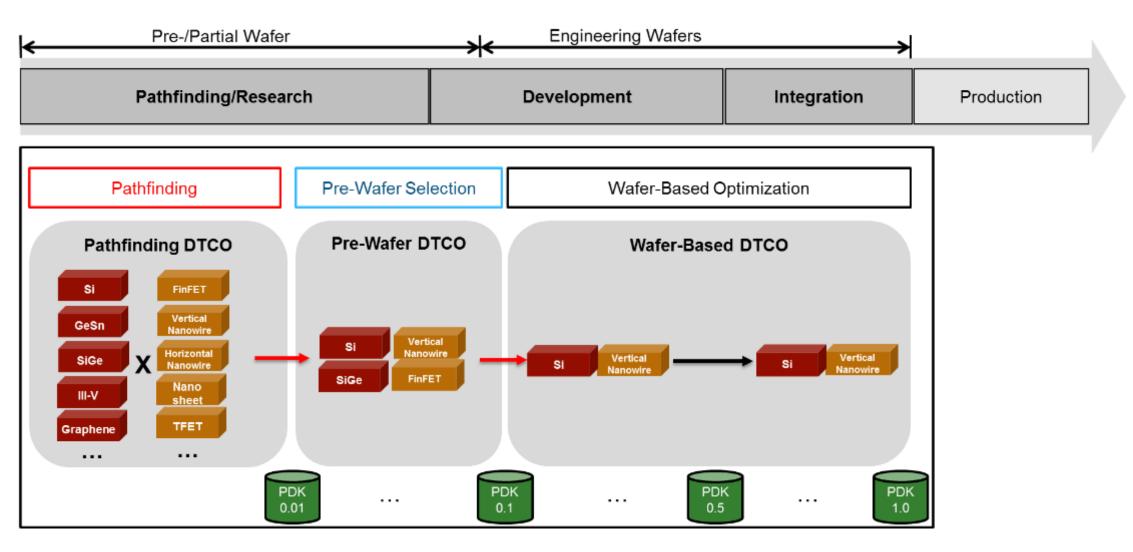

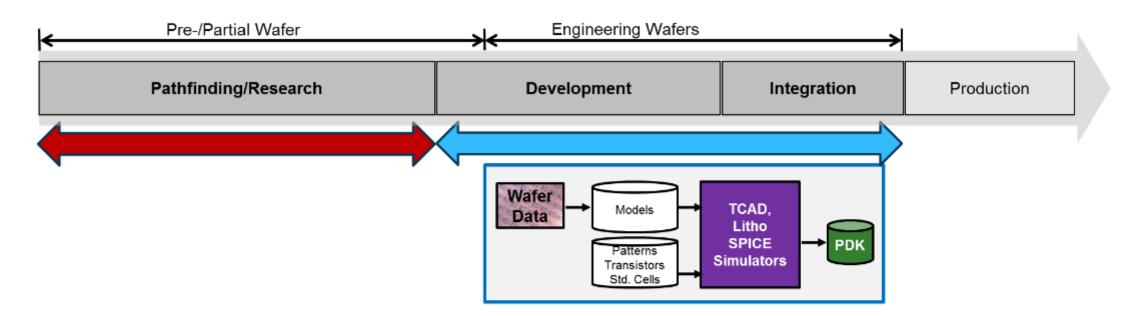

#### **Reduce Process Technology Development Time**

By Enabling Selection through Early Process, Design Rules & IP Co-Development

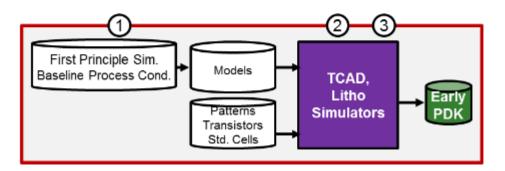

#### Research phase selection and evaluation enabled by:

- 1. First Principle Simulators and Baseline Process Conditions to create models for TCAD and litho simulation

- 2. Automated TCAD-to-SPICE model creation for PPA evaluation of full circuits

- TCAD, lithography, SPICE simulation to achieve early maturity in litho/OPC and design rules, and analyze/optimize performance, power, area, yield of transistors, patterns, and circuits

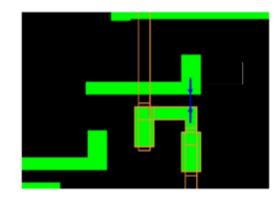

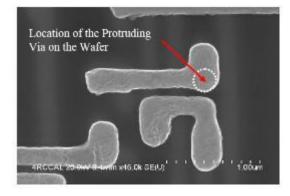

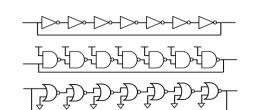

#### Traditionally, Small Structures Are Used To Develop And Evaluate Devices/Process

- Single transistors

- Simple logic (inverter)

- Metal patterns for lithography

- Etc.

- Problem: Complicated, actual designs often reveal fundamental problems after the process is delivered to production

- For example: A particular layout pattern causes systematic yield loss

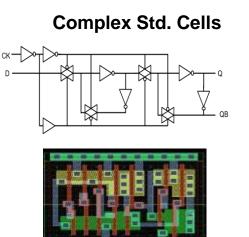

### DTCO: Early Use Of Larger Circuits For The Evaluation Of Technology Options Minimizes Late Surprises

- Single transistors

- Simple logic (inverter)

- Metal patterns for lithography

- Etc.

DTCO: Use larger, more realistic test cases earlier in development to better evaluate how well the device/process options meet the requirements of real designs

**Customer Blocks**

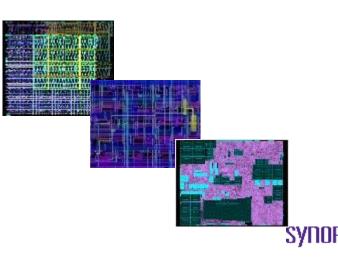

#### Fast Process Simulation, Automatic Generation of SPICE Models & Early PDK Enables Use Of Larger Test Cases

| Test Cases | Cells                                  |                                                |                                          |  |  |  |  |

|------------|----------------------------------------|------------------------------------------------|------------------------------------------|--|--|--|--|

|            | Pathfinding                            | Pre-Wafer                                      | Wafer-Based                              |  |  |  |  |

| Size       | ~10T                                   | ~40T to ~200T                                  | ~40T to 100K Gates                       |  |  |  |  |

| Number     | ~5                                     | ~100                                           | ~1000                                    |  |  |  |  |

| Examples   | Transistor,<br>Inverter, NAND,<br>SRAM | + MUX, Flip-<br>Flop,<br>Ring Osc<br>USB Logic | + Full Std. Cell Lib.<br>Customer Blocks |  |  |  |  |

- Where Do We Stand & What Lies Ahead Lithography & Devices

- ⇒ DTCO: Design And [Process] Technology Co-Optimization

- ⇒ Back To… The Future !

[Heterogeneous] Integration

#### Where Do We Stand ? What Lies Ahead ? Heterogeneous Integration

|                                         | FinFET<br>Will stay until 3nm                                               | EUV                                                                 |  |

|-----------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|--|

|                                         | No clear "heir" yet<br>Silicon nano-sheets and<br>nano-wires top contenders | Mainstream at 5nm<br>LE/LELE for M0/M1<br>2D rules temporarily back |  |

| GPU, CPU, NPU, TPU,<br>5.5D-IC (Passive | SI/Substrate)                                                               | APU, A&M/S<br>3D-IC (Active SI)                                     |  |

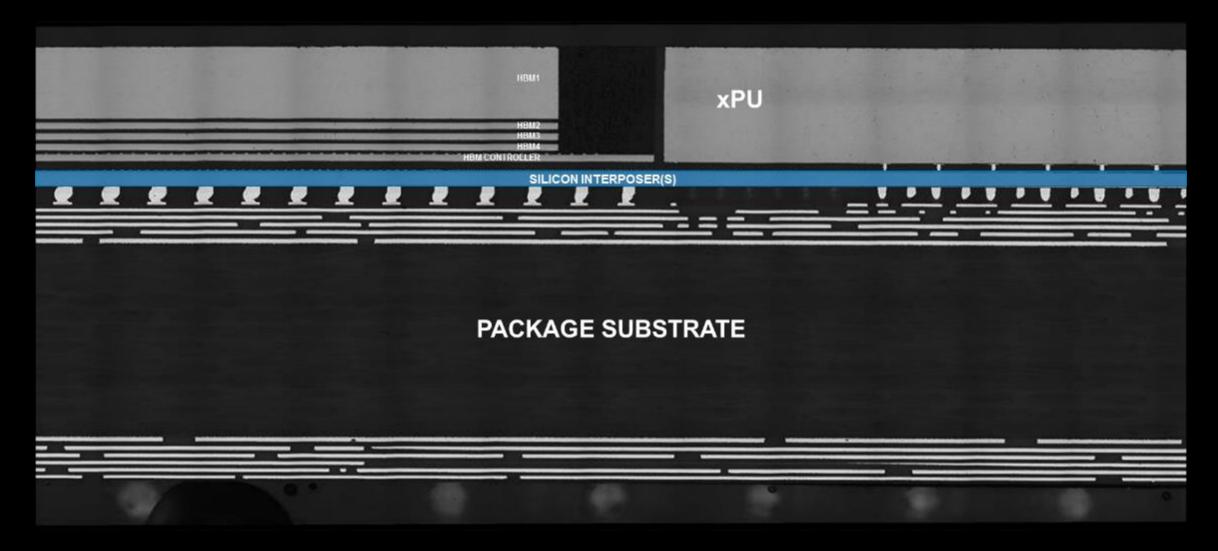

#### Integration Implications – Beyond The Die Multiple Die/Stacks Onto Multiple Silicon Interposers

Source: Synopsys Research, 2017

#### Integration Implications – 2.5D-IC Multiple Die/Stacks Onto Multiple Silicon Interposers

"Pascal" 5.5D-IC (3D + 2.5D) Integration; Source: L. Nyland, et al., NVIDIA, GPU Technology Conference 2016

#### Typical 5.5D-IC (3D + 2.5D) HBM-Based Application GPU Die (21B Transistors @ 12 Nanometers) + 4 HBM2 Stacks (4 × 4GB) Onto Two ? Three ? Or Four ? Silicon Interposer Die Stitched Together

$GPU = 815 \text{ mm}^2$

100000

silicon Interposer(s) = 1,400 mm<sup>2</sup>

"Volta" 5.5D-IC (3D + 2.5D) Integration; Source: J.-H. Huang, et al., NVIDIA, GPU Technology Conference 2017

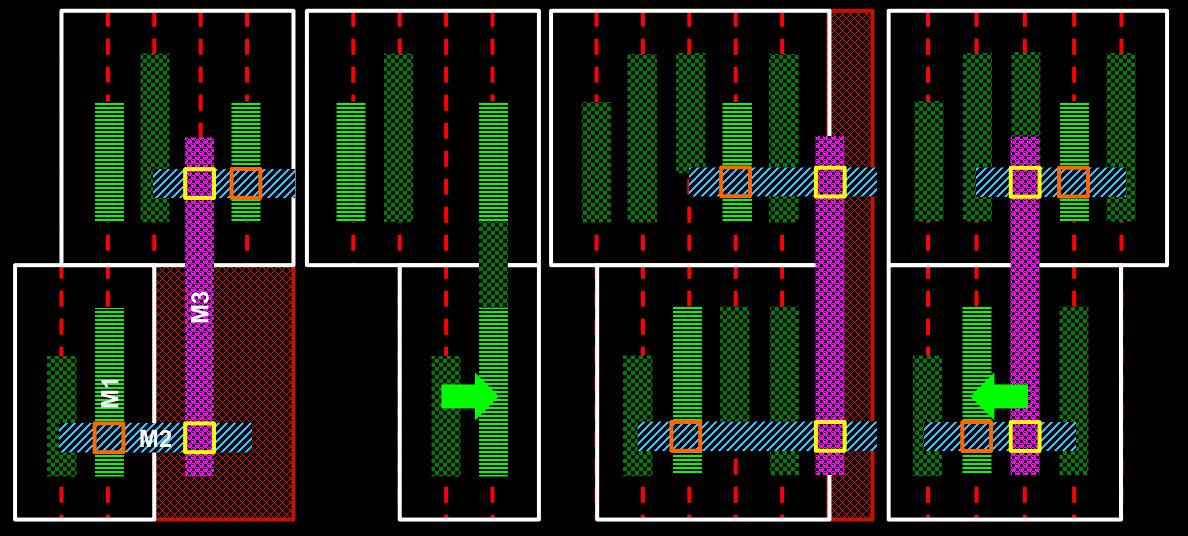

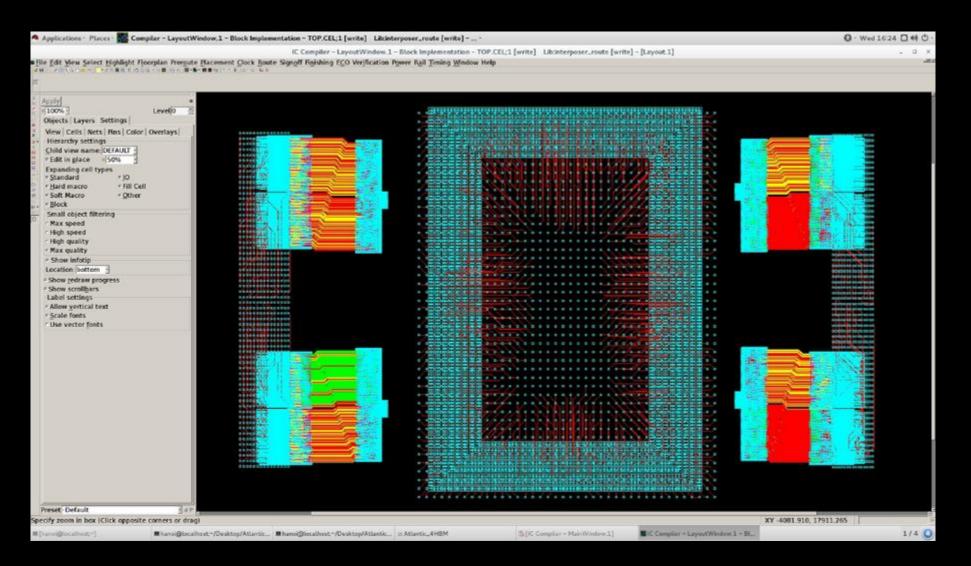

#### HBM2 Die-To-Die Routing Onto The Silicon Interposer

Signals Routed on M2 & M3, Offset by One Track, Run Between VSS Routes VSS Mesh Provided on M4 (AP) and M1 for M3 & M2 Shielding, Respectively

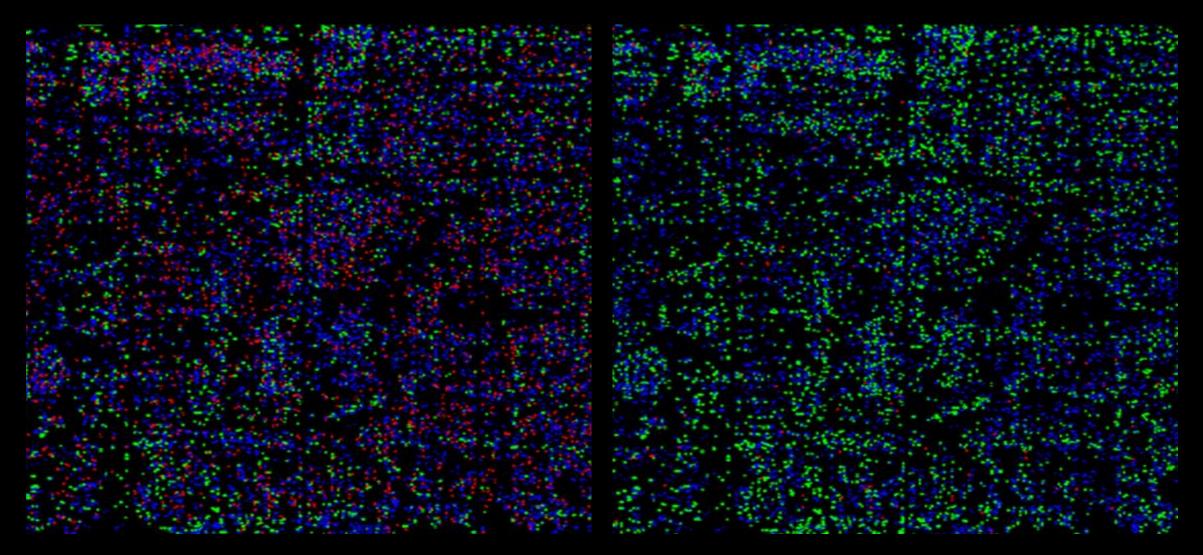

#### **HBM2 Die-To-Die Routing Solution Space**

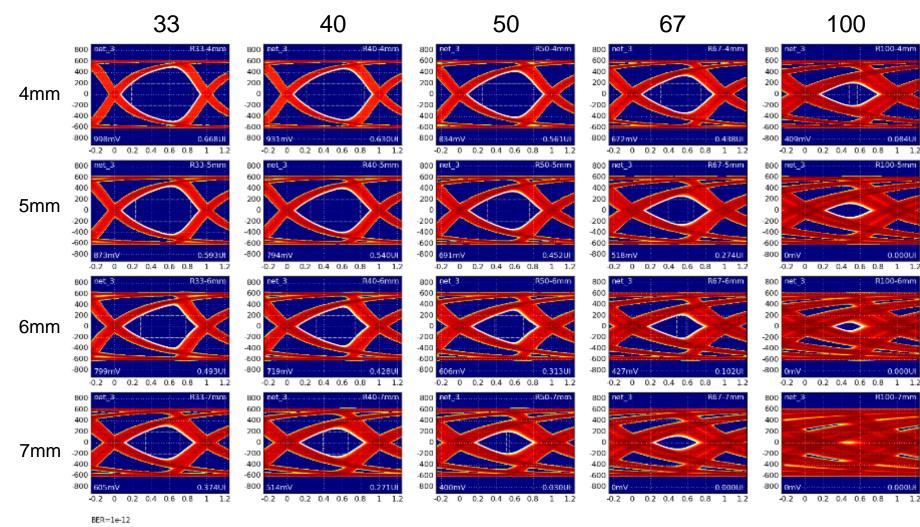

Driving Strength (33, 40, 50, 67, 100  $\Omega$ ) and Channel Length (4, 5, 6, 7 mm)

- Assuming Linear Ideal IO model at 2.4Gbps speed

- VDD=1.2

- <sup>•</sup> Cpad@PHY = 0.4pF

- Cpad@DRAM = 0.4pF

- TX Jitter = 0.1UI UDJ

- Expected RX metric (FOM) = 0.5UI

- 4mm and 5mm will pass the FOM with some driver strength(s)

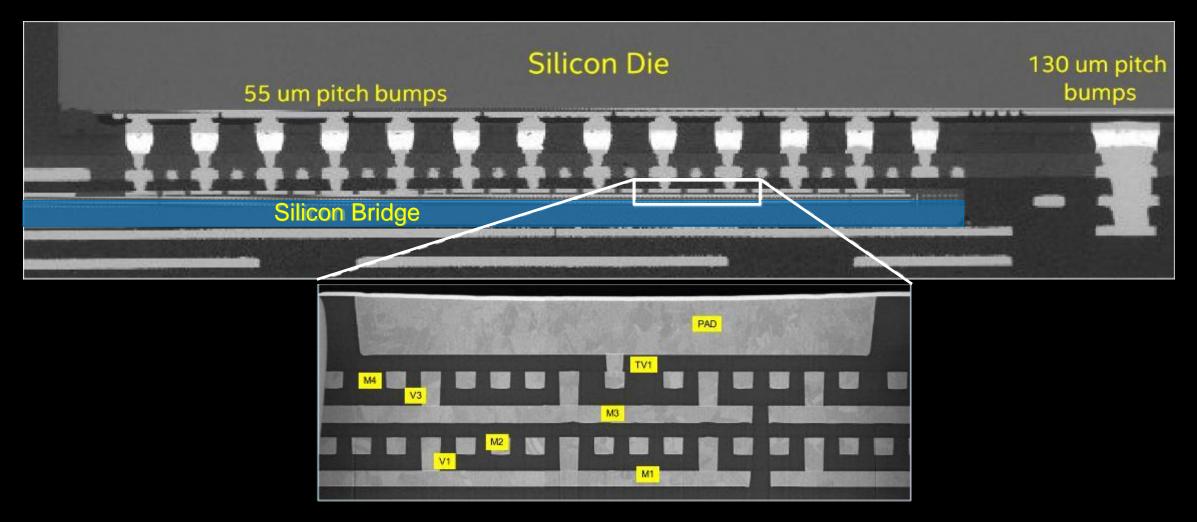

#### Integration Implications – 2.5D-IC Multiple Die/Stacks Onto a Package Substrate with EMIB

© 2017 Synopsys, Inc. 41

10 Nanometer EMIB; Source: M. Bohr, Technology & Manufacturing Day 2017

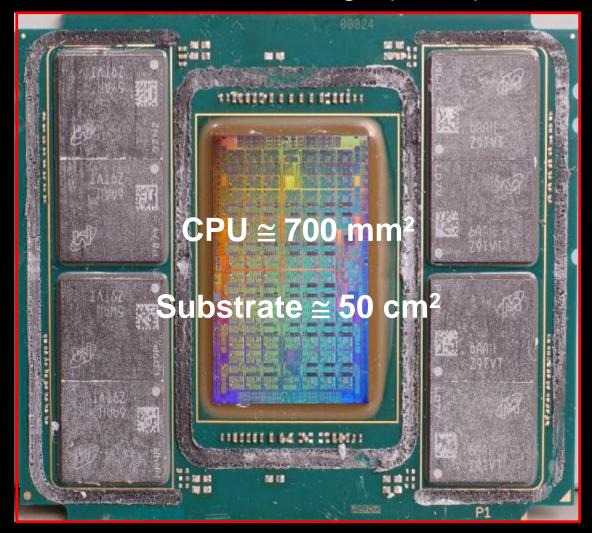

#### Typical 5.5D-IC (3D + 2.5D) Application

CPU Die + 8 HBM1 Stacks (8 × 2GB) Onto a Package Substrate with Intel Embedded Multi-Die Interconnect Bridge (EMIB)

© 2017 Synopsys, Inc. 42 "Knights Landing" Xeon Phi 5.5D-IC (3D + 2.5D) Integration; Source: Intel 2016 ; Synopsys Research 2017

- Where Do We Stand & What Lies Ahead Lithography & Devices

- ⇒ Design And [Process] Technology Co-Optimization

- $\Rightarrow$  Back To... The Future !

Integration

⇒ Closing Remarks

### **Closing Remarks**

- Our ability to etch taller/thinner fins went the extra-mile, thus extending FinFET lifespan beyond the most optimistic forecasts

- GAA expected to replace finFETs at 7nm, but managed to push finFET down to 5nm

- EUV is finally here, and will be introduced at some point for 7nm

- There are still drawbacks to be solved, such as power source degradation, mirrors, pellicles, resists, wafer planarization, metrology, etc

- EUV is not the panacea some dreamt about

- EUV is actually a very expensive etchnology

- Multi-patterning will be back at 5nm

- 3D-IC, attractive because of memory and bandwith requirements, now being used in many applications: CPU, GPU, TPU, Network Processors (NPU)

## **Closing Remarks**

- A lot of the challenges of the coming technologies fall on physical design

- Sheer complexity remains the #1 challenge:

- 1T transistors at 3nm (30Å) translate into 100B placeable instances

- # of polygons & LRC values may exceed  $1P = 10^{15} = 50$  bits

- Significantly more complex placement rules

- Lithography changing balances

- Transistors shrink much faster (30% linear, 50% area) than interconnect (20%)

- Number of pins/gate stays equal, less tracks per cell, so routability is the key problem

- Rule complexity, both placement and routing, and "special" cells e.g. via ladders, impact the physical side of synthesis. Increasing dependence on placement, global routing, track assignment, and possibly even further

- IC integration brings challenges beyond the die

- Partitioning before place & route

# Some Implications Brought In By The Coming Semiconductor Technologies

Dr. Antun Domic, CTO Synopsys, Inc.