## Power: What's the problem? Industry trends and solutions in low power design

Steve Carlson, Low Power Solutions Systems Verification Group April 2015

cādence<sup>®</sup>

## Agenda

- Industry Trends

- Power: what's the problem

- The problem: it's not just power

- Power challenges: is not the performance, it's the thermal

- Use case and scale challenge

- Cadence technologies

- Summary

## Industry trends Drivers of design change

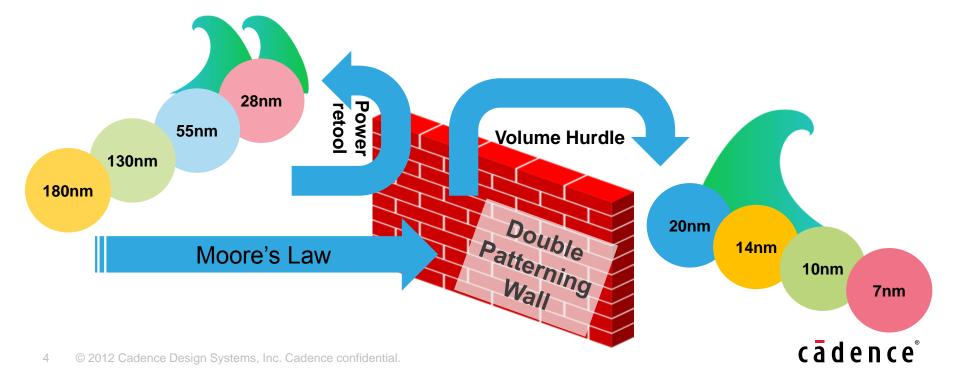

## Moore's Wall

### Macro trend bifurcates miniaturization roadmaps

#### Mature nodes evolved

- Lower and lower Vdd

- Re-design memories, analog IP, etc.

- Add LP cells for PSO, MSV, etc.

- Thermal/performance issues at near threshold Vdd values

- MEMs sensors, energy harvesting, RF

#### Advanced node

- Very high volume drivers jump the hurdle

- Multi-patterning

- New materials/devices

- Power and thermal issues hamper architectural performance gains

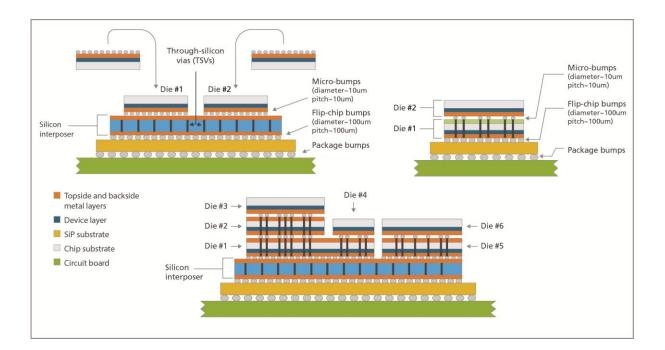

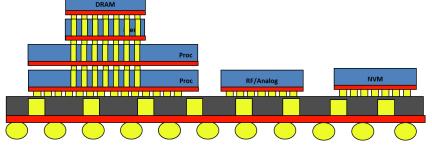

## Packaging innovation Miniaturization innovation beyond Moore

- Foundries drive Si interposer and stacking technologies

- OSATs investing in fine geometry organic substrates

- PCB embedded die

#### Product designers: litany of new choices; customization flourishes

## cādence<sup>®</sup>

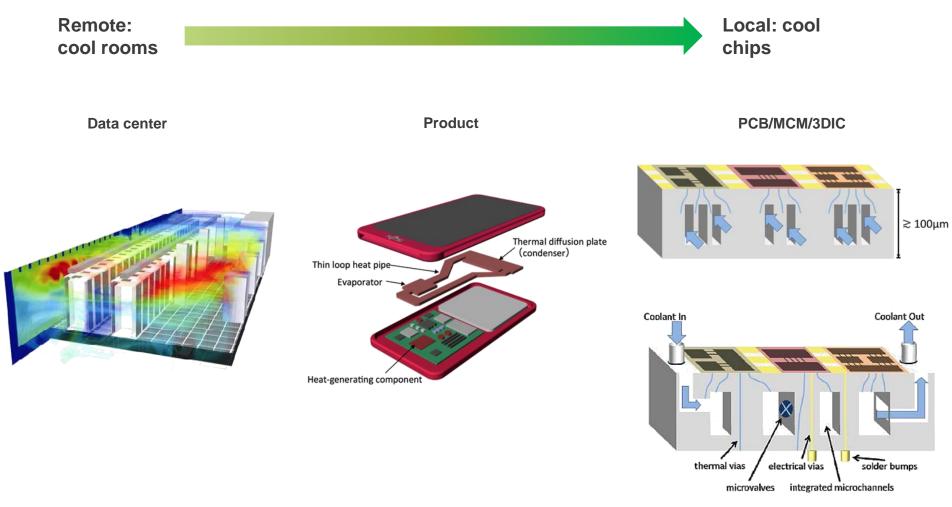

## Cooling: remote to local, materials Virtuous circle of reduction

cādence°

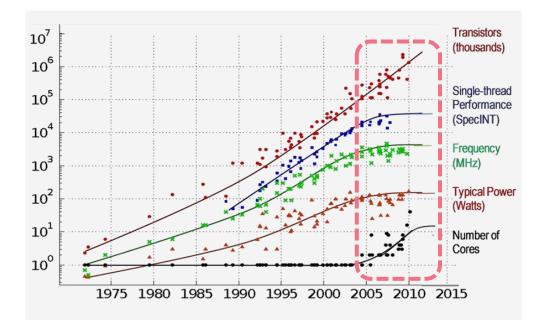

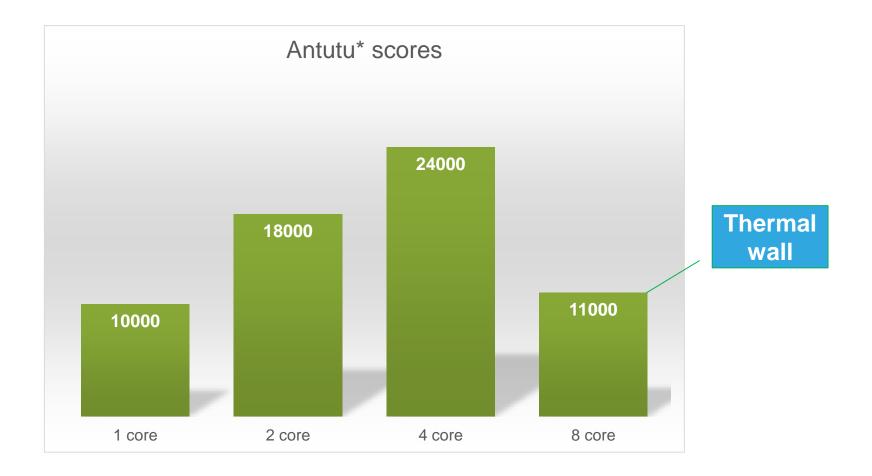

## **10 year trend summary** Physics, architecture, manufacturing changed shape

- Frequency wall based on power limit

- Single thread performance stall

- Performance gains through multi-core

- Heterogeneous cores to optimize performance-energy

- Thermal wall based on parallel execution limits

- "Dark silicon" becomes pervasive

- Complex orchestration of execution units to maximize performance and stay within thermal limits

- Simultaneous need to task energy efficiency

- Battery life in mobile

- Power/cooling cost in data center

## cādence<sup>®</sup>

## Power: what's the problem? Hot topic

## Power verification: why the surprises

## • It's simple:

- UPF/CPF provide specification

- Switches, isolation, retention, modes, ...

## • It's complicated:

- Which voltage level?

- Which frequency?

- Which corner?

- Which voltage domain?

- Which use case?

3 or more 3 or more

- 12 to 100

- 12 to 100

- 100 or more

- Billions of clock cycles

## cādence°

## Complementary LP Verification Solutions LPV App, Incisive LP Simulation & Conformal Low Power

cadence

#### Verification Formal Comprehensive LP assertion Elaborate power-aware design **Basic LP assertions** support from RTL + UPF/CPF Power-aware debug LP functional checks Models isolators, state retention LP XPROP analysis Power-aware SEC Basic power-aware "lint" • Provides LP-awareness for Static analysis of power format other apps (XPROP, FPV, CONN, CSR...) Simulation/Emulation LEC/LP Static code analysis (lint) in PSO Disable corruption of certain datatypes Replay initial blocks at power-up Logical/physical netlist structural Power aware sim checks Find design and power sequence errors Level-shifter, power switch checks Synthesis/ including incorrect isolation values, Cell mapping & library checks initialization problems, incomplete state Implementation Power-aware LEC retention, etc. PG connection & layout checks Supports custom & MS macros Power-aware gate-level verification Liberty support

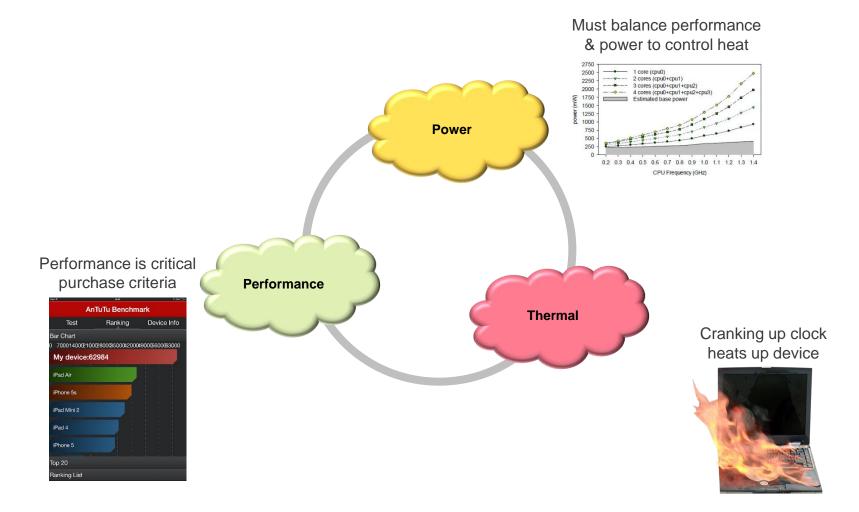

## The problem: it's not just power Interrelated design criteria

## Example: mobile processor SoC Thermal issues diminish architectural performance potential

#### \*Antutu Android benchmark (www.antutu.com)

## Performance-Thermal-Power Domain connections

cādence°

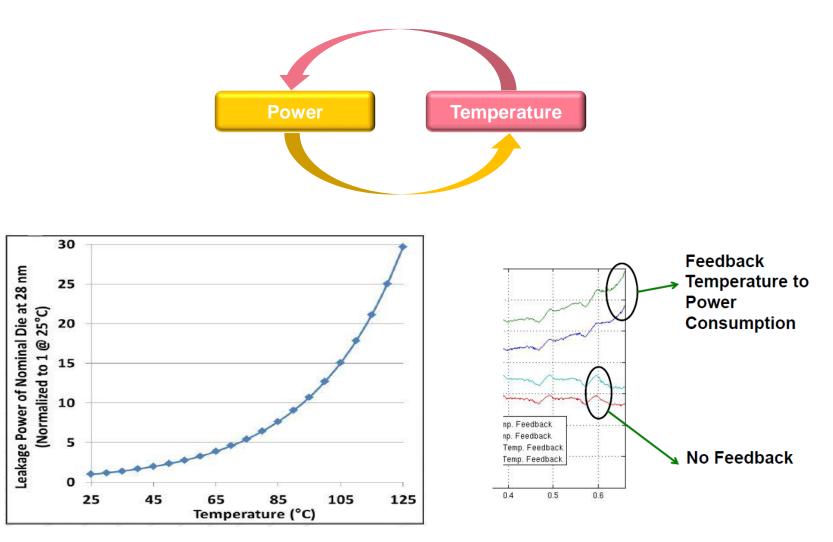

## Power ⇔ Temperature Mutual dependence ⇔ nonlinear behavior

cādence<sup>®</sup>

## Power challenges It's not the performance, it's the thermal

15 © 2012 Cadence Design Systems, Inc. Cadence confidential.

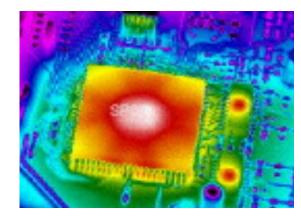

## Thermal issues in modern SoCs

- Growing thermal issues

- Technology scaling => higher power density

- 3D stacking with TSV => greater thermal issues

- Temperature impacts

- Power consumption

- Peak performance

- Ageing/reliability

- Package costs

- MP SoC architectures

- Dynamic applications, variable execution time

- Power management solutions (DVFS), can even worsen thermal properties!

- → Thermal mitigation schemes must be proposed at design time

cādence

## Thermal mitigation landscape From system to sign-off

#### Applications/OS/system

•Which applications are critical to product success? Desired user experience: speed, battery life, form factor, cost?

#### Architecture

•What computation elements needed to achieve performance/efficiency/cost?

#### Design

•How to link modules, create microarchitecture, drive mapping to process?

#### Implementatior

•Which node, what library, what flow, which tools, ... ?

- Thermal-aware OS features

- Register re-mapping

- Thread migration

- Weighted task scheduling

- Processor choice(s), IP selection

- Hard-wired versus programmable

- Voltage/power domains

- Package/enclosure selection

- Micro-architecture optimization

- Power management

- Power optimization

- Clock gating

- Lower local layout density

- Spread hot units far apart

- Interconnect pitch control

- Power optimization

## cādence<sup>®</sup>

# Use case & scale challenge

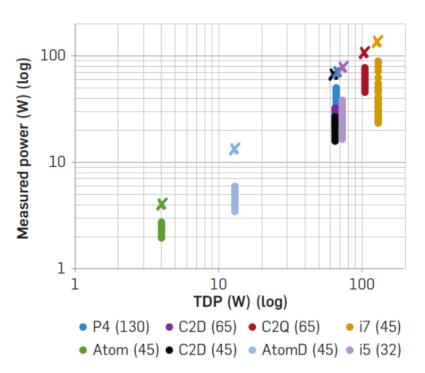

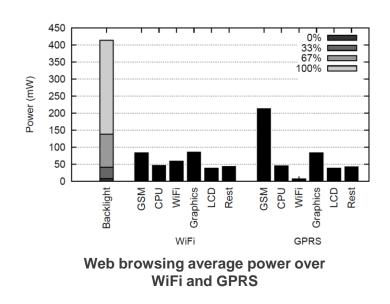

## Use case challenge: huge dependency Performance benchmarks vary 8-10X

Measured power for each processor running 61 benchmarks. Each point represents measured power for one benchmark. The "X"s are the reported TDP for each processor.

**Finding**: power is application dependent

Cao et al, CACM 2012

## cādence<sup>®</sup>

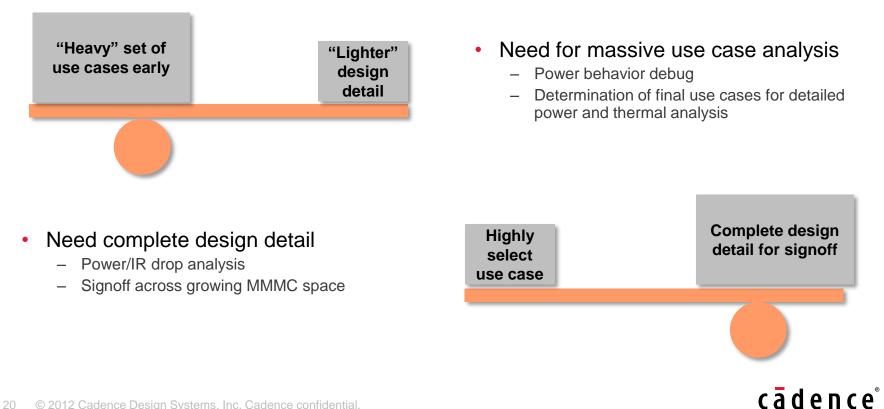

## Early power visibility Abstraction hinders and helps

- Abstraction of design <u>hinders</u> accuracy •

- Abstraction of design <u>helps</u> processing more use cases •

## Cadence Technologies

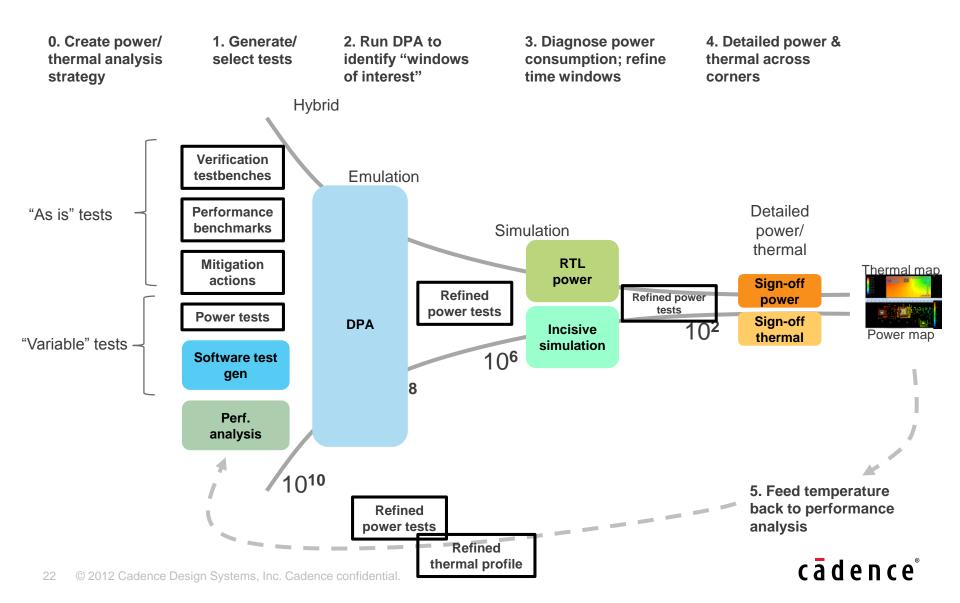

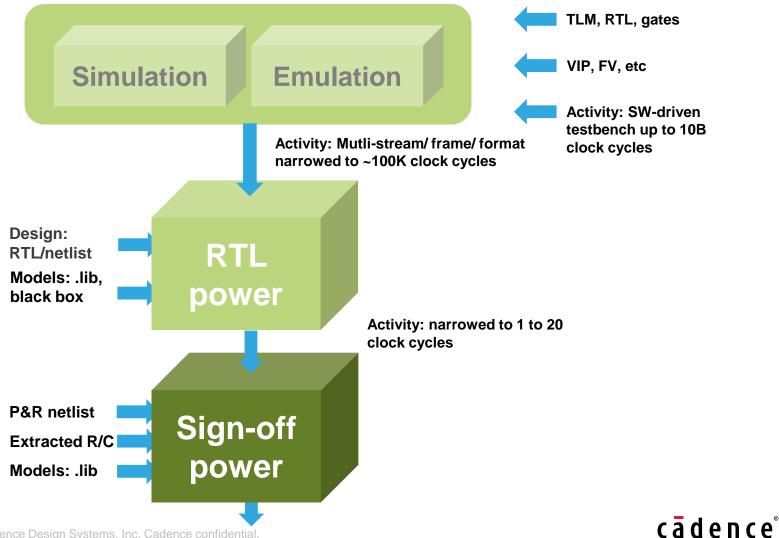

## High-level view of flow Use case "funnel" drives flow

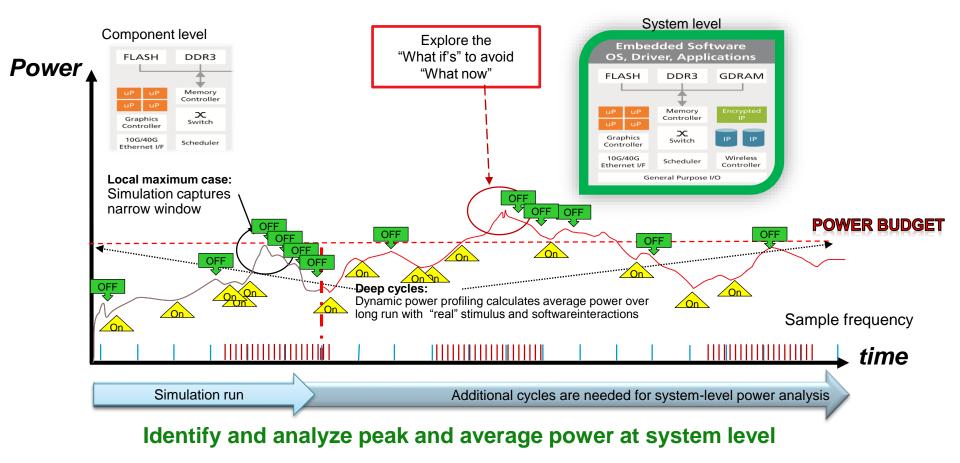

## SoC power analysis requires "deep" cycles

At 100MHz for 10 seconds => 1 billion cycles

cadence

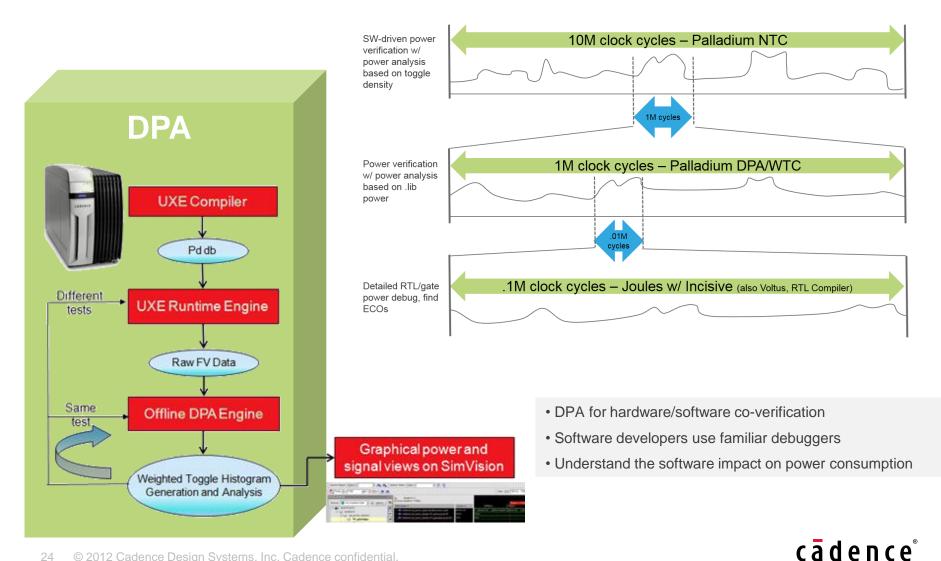

## Power analysis: Emulation DPA (dynamic power analysis) RTL & gate power w/ "deep cycles" capability

#### 24 © 2012 Cadence Design Systems, Inc. Cadence confidential.

## Characterize, virtualize

Case for hybrid model – many use cases are not CPU-dominated

GSM phone call average power

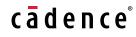

## The emulation/VSP hybrid solution

- Bring-up SW early, finish by Tapeout

- Bring-up and test Linux and drivers days after first RTL drop

- Bring-up and test Android weeks before tape-out

- Complete Linux / Android-based SoC testing by tape out

- Accelerate SW-driven SoC verification

- 100X faster boot

- 4X Faster OGL tests

- Full HW/SW debug

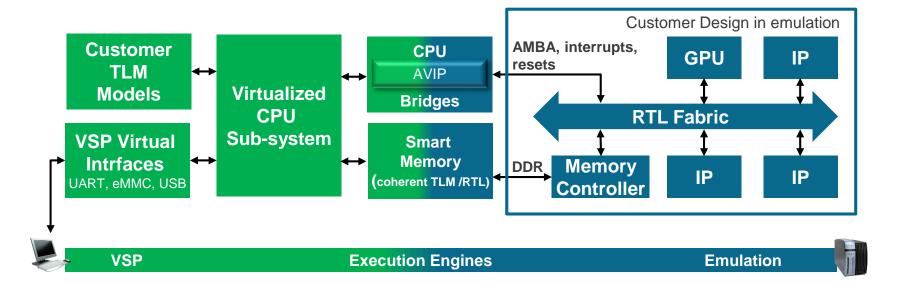

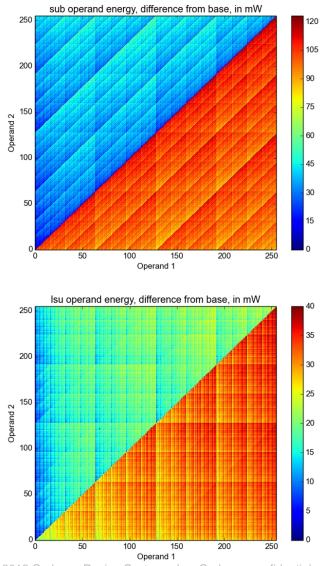

## Data dependency: 10X difference per operation Statistical distribution assumptions become important

Eder et al, Univ Bristol, 2015

27 © 2012 Cadence Design Systems, Inc. Cadence confidential.

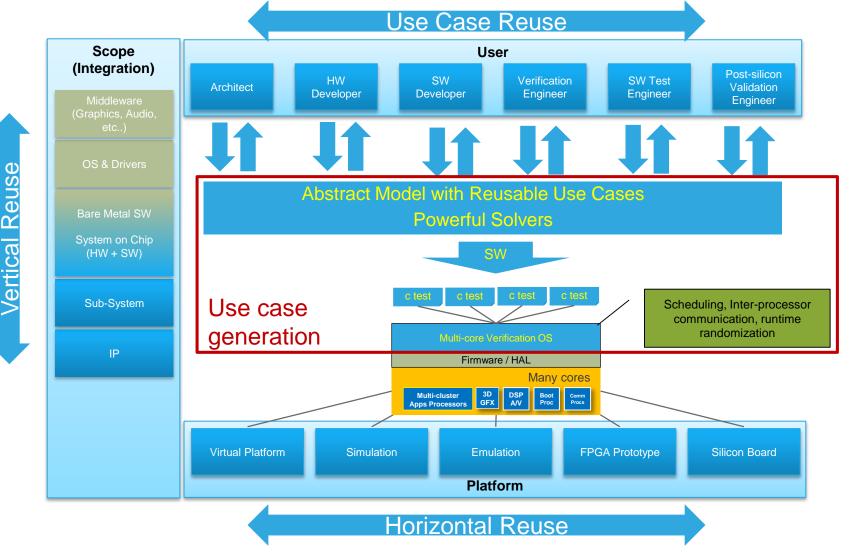

## The Solution: Automated use case generation Software test generation

cādence®

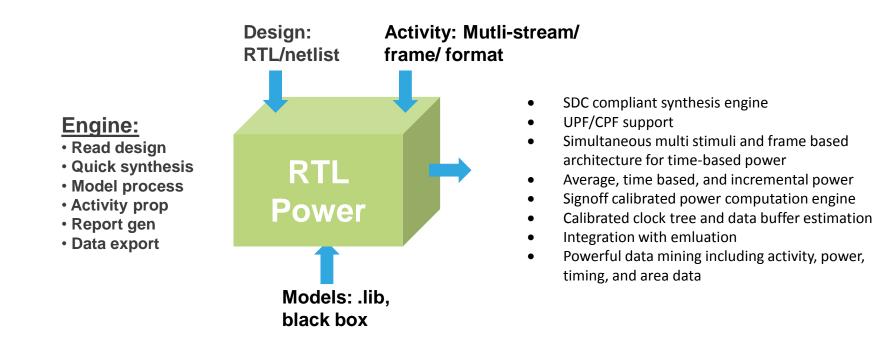

## Power Analysis RTL and gate power based on .lib models

## Power Analysis: Joules & Voltus progression RTL and gate power based on .lib models

© 2012 Cadence Design Systems, Inc. Cadence confidential.

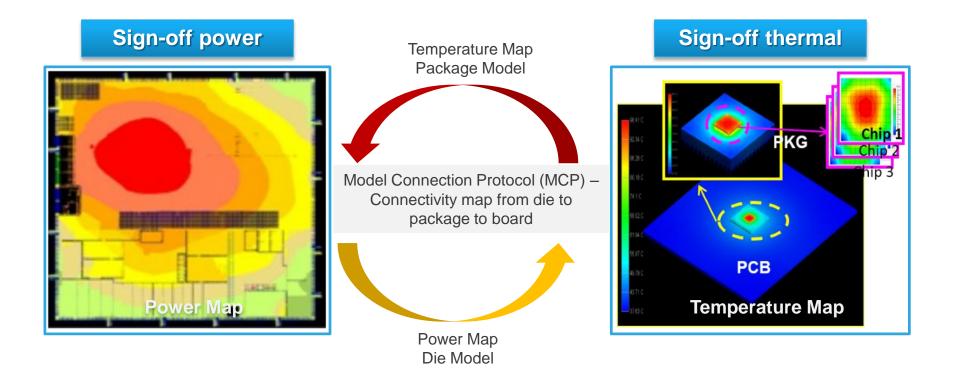

## Chip-package-board thermal co-simulation

- Thermal computes Temperature map including chip, package and board

- Power computes temperature dependent power map of die

- Co-simulation until results converge

## cādence®

## Summary

## • Power: is it a problem?

- Verification technologies and methodologies are deployed

- Analysis needs to migrate forward and encompass more use cases

## Power: it's not just about power

- Performance and thermal are intimately interrelated to power

- Need to progress towards holistic P-T-P solution

## Technologies

- Verification technologies applicable for performance/thermal/power

- Full suite across fabrics for design and analysis

## Power: No problem ! ③

# Thank You

33 © 2012 Cadence Design Systems, Inc. Cadence confidential.

# cādence®