# Hybrid Virtual Platforms: Are they the highbred Virtual Platforms?

Dr. Vinoo Srinivasan Pre-Si Systems Solutions, Intel April 2015

#### System view

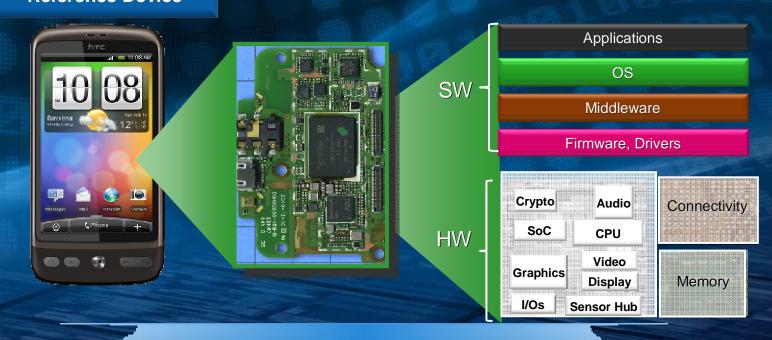

<u>System</u> Form Factor Reference Device

Platform Board + SoC + SW Stack

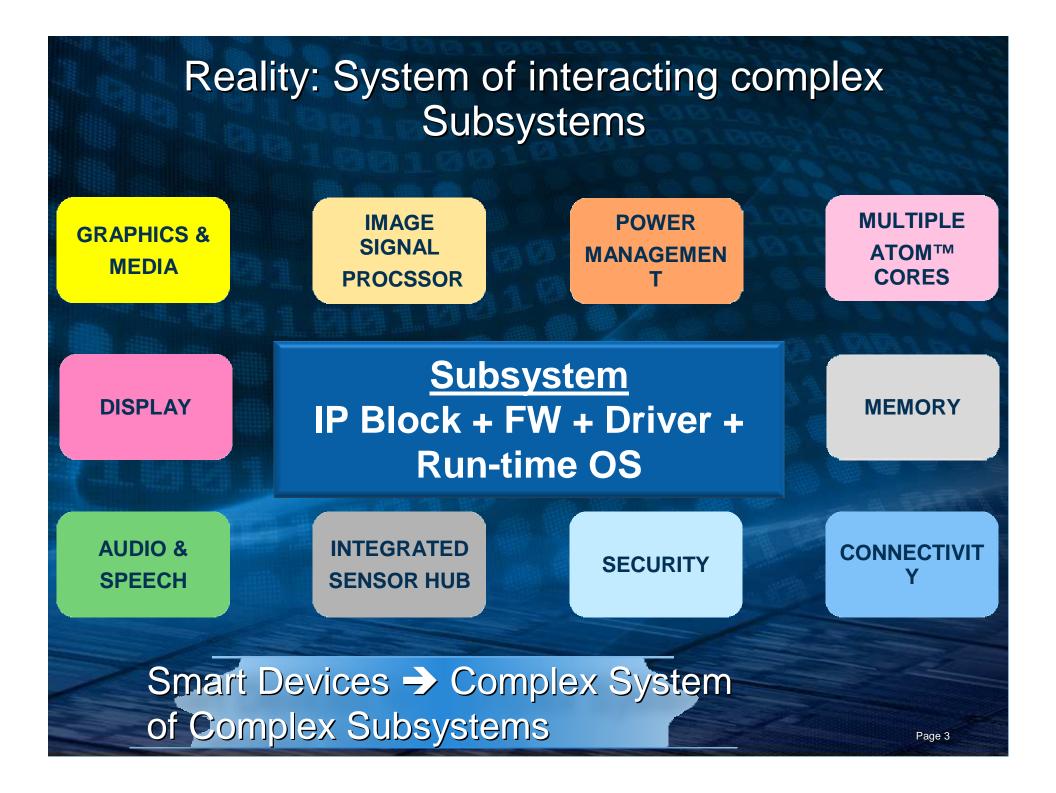

Smart Devices → Complex System

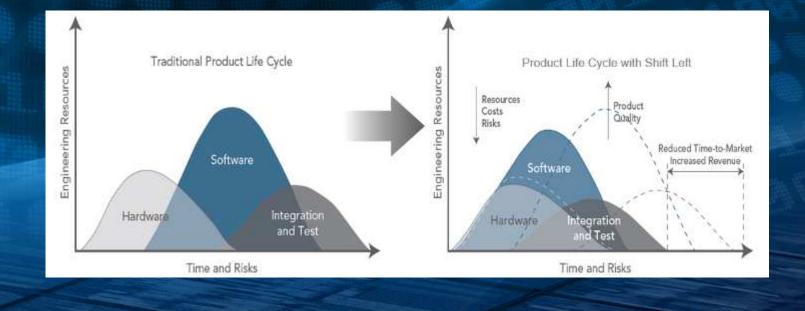

# Shift Left

## Achieving TTM Requires Shift-Left

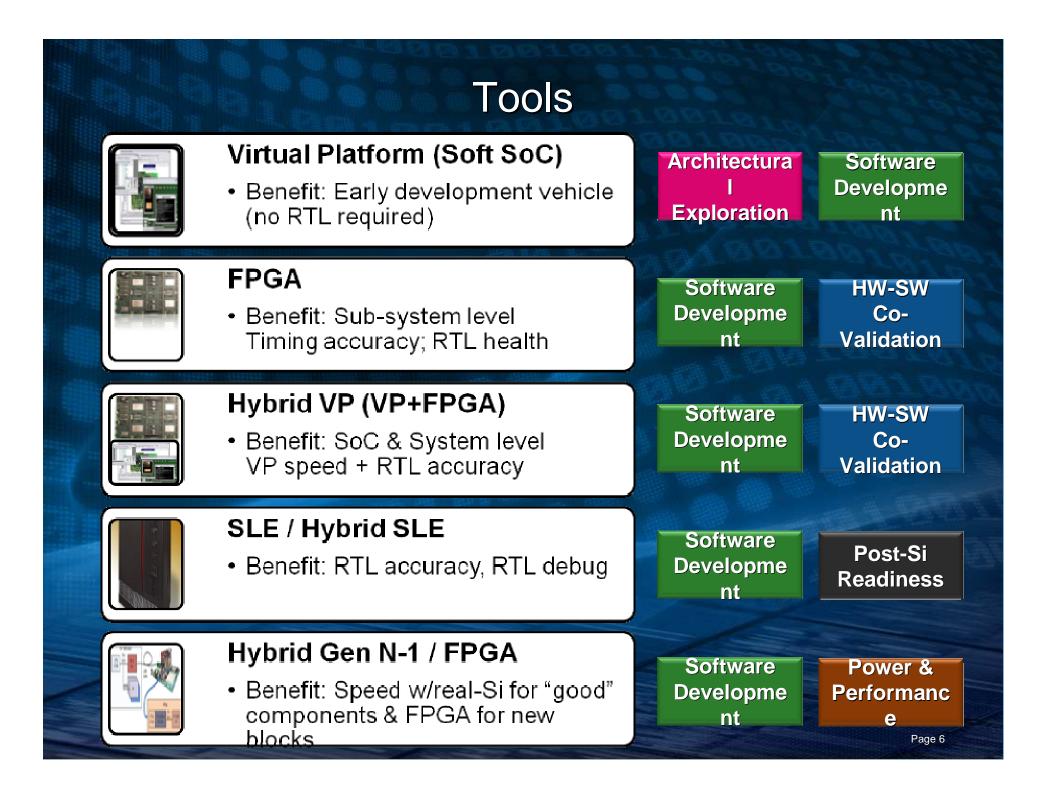

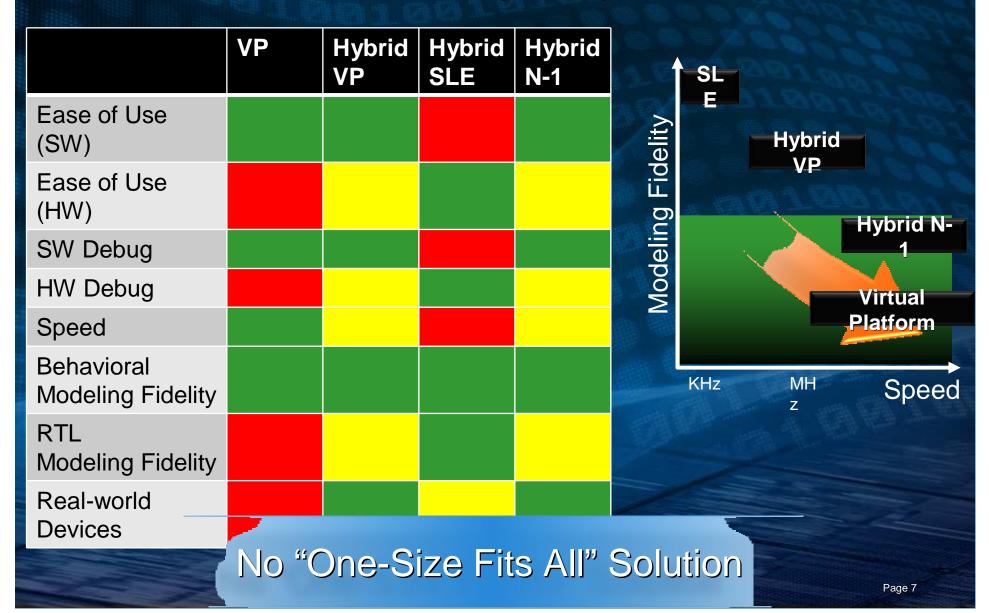

## **Tools & Technologies**

#### Achieving Shift Left Requires Better Tools & Methodologies

Page 5

#### The need for Hybrid platforms

# Hybrid may fit your needs ..... But Can You match what Hybrid needs?

#### Hybrid Challenges

Complex integration of many HW & SW components

Narrow window of opportunity (after stable RTL)

Multi-team, multi-skill dependency

Cost: FPGA/Emu are expensive

Tooling: FPGA tool chain is still maturing

Velocity: DEBUG!!! Where in the stack is the bug?

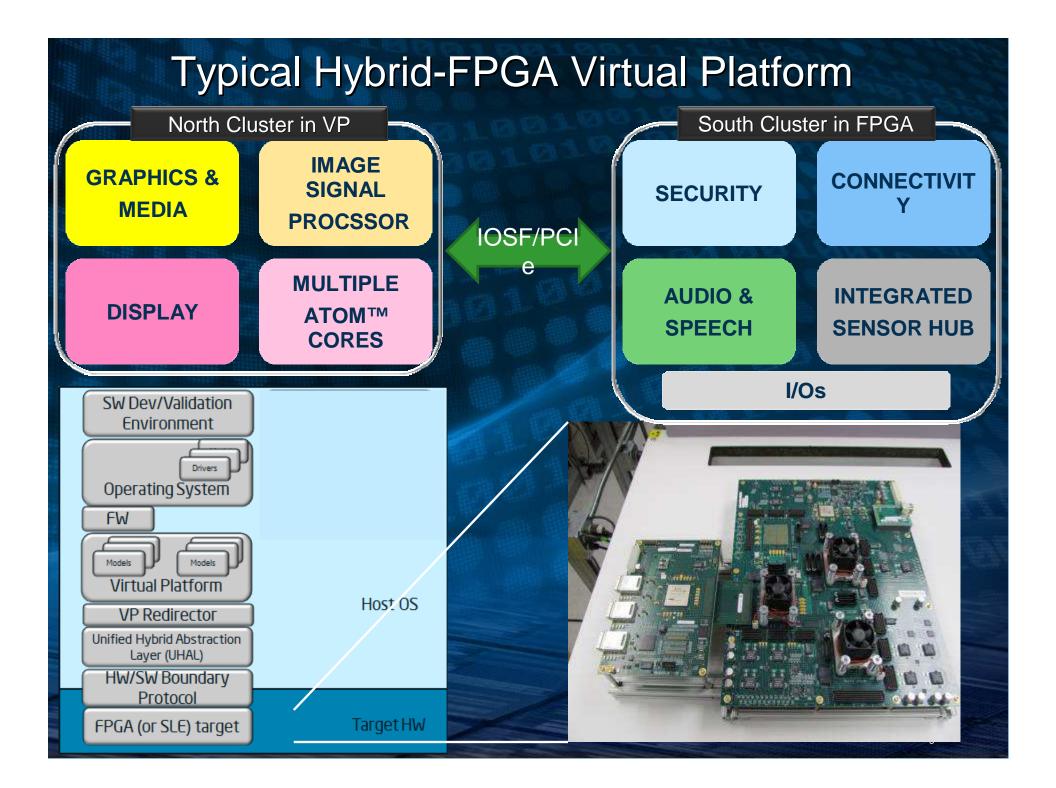

SW Dev/Validation Environment

**Operating System**

Virtual Platform VP Redirector Unified Hybrid Abstraction Layer (UHAL)

HW/SW Boundary Protocol FPGA (or SLE) target

FW

Models

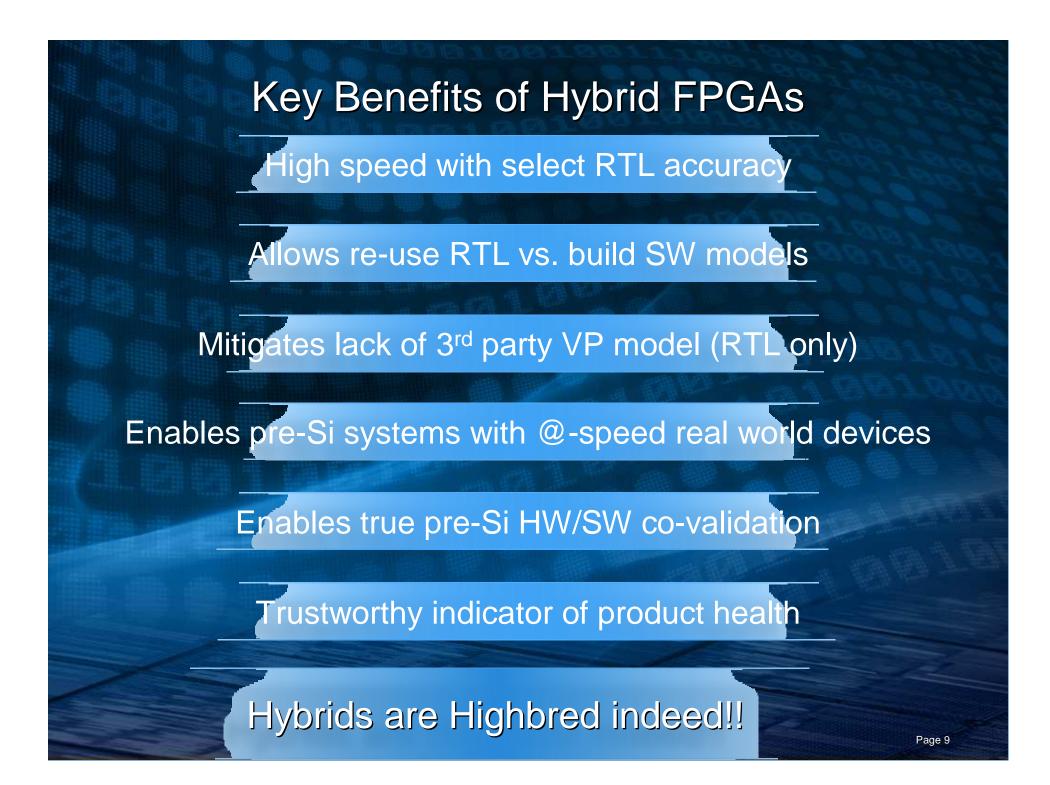

### Summary

#### Hybrid Virtual Platforms: Are they the highbred Virtual Platforms?

Yes they are...

but be prepared for the challenges before you breed them