#### Multi-Die Packaging – How Ready Are We?

**EDPS 2015**

Rich Rice ASE Group April 23<sup>rd</sup>, 2015

## Agenda

#### • ASE Brief

- Integration Drivers

- Multi-Chip Packaging

- 2.5D / 3D / SiP / SiM

- Design / Co-Design Challenges: an OSAT Perspective

- o Summary

## Brief Backgrounder

Established 1984, production commenced at flagship factory in Kaohsiung, Taiwan. Achieved global market leadership in 2004, surpassing all players in OSAT industry. Operations now at 12 facilities worldwide, serving multiple markets, applications, & geographies. >50K employees: Global team comprises operations, engineering, R&D, sales, & marketing. ASE Group overall revenue of \$8.4B in 2014, 14% over 2013. ATM\* overall revenue of \$5.3B in 2014, 9% over 2013.

ATM\*: Assembly, Test, Material

## **Integration Drivers**

3

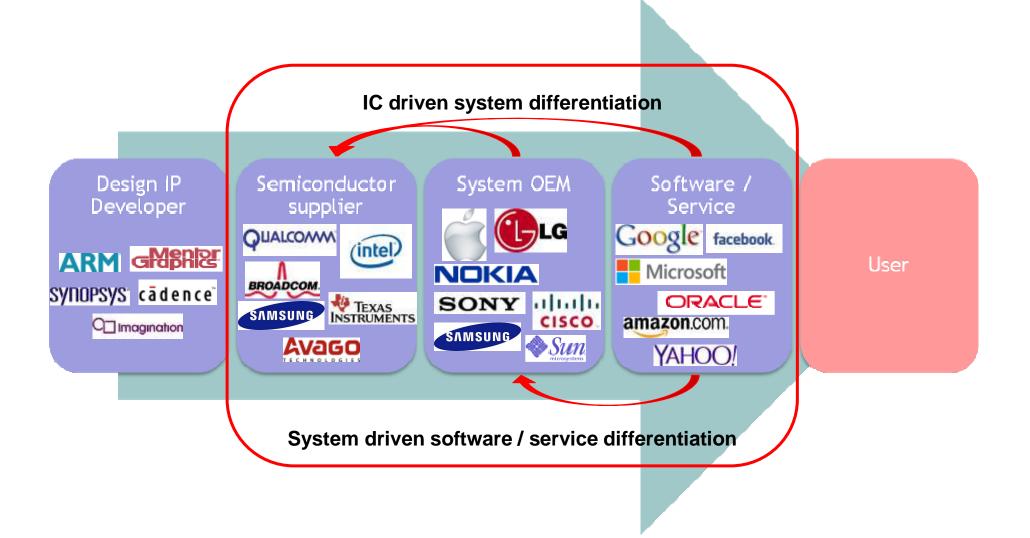

## Value Chain Consolidation

#### **Creating Differentiation**

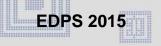

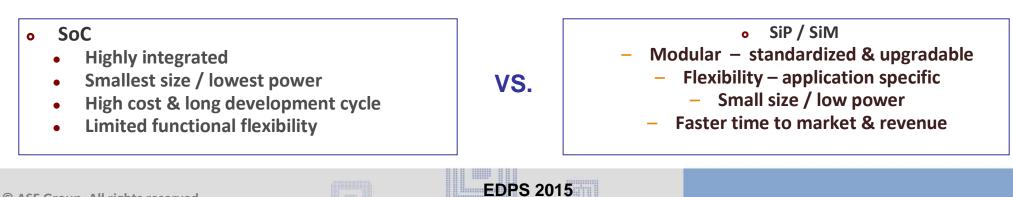

## SoC-SiP-SiM Evolution

5

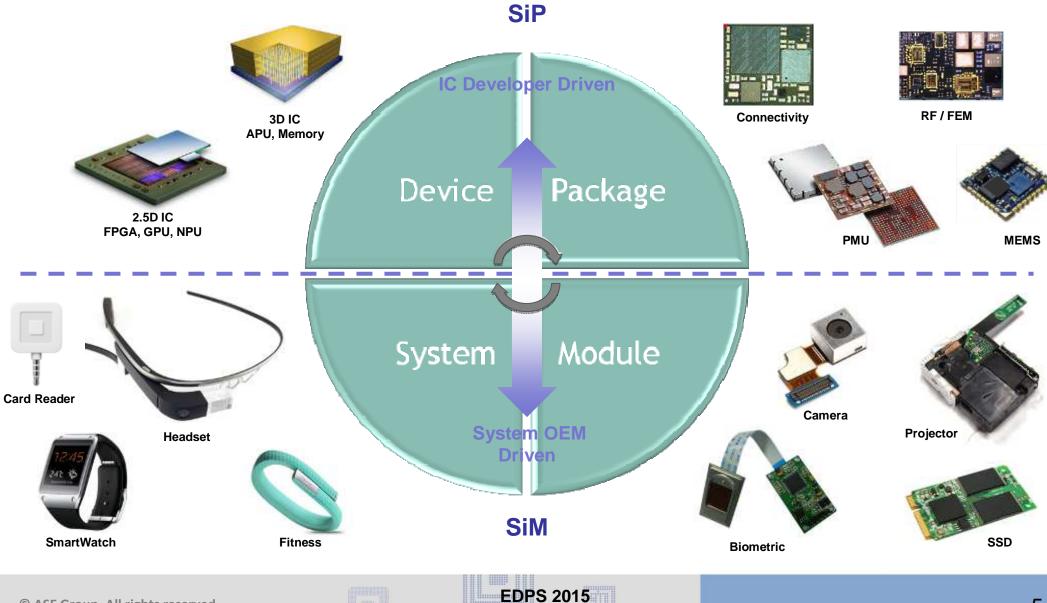

## Basic IoT SoC / System

Source: Tyson Tuttle – CEO SiLabs

- Instrumented

- Able to sense and monitor environment

- Intelligent

- Capable of analytics

- Can make decisions based on data

- Interconnected

- Shares data through cloud

- Interacts with people and other systems

- Can remotely monitored and controlled

- Secured

- Protects data from malware, theft or tampering

# Multi Chip Packaging

7

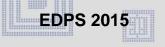

#### 2D & 2.5/3D Packaging Technology

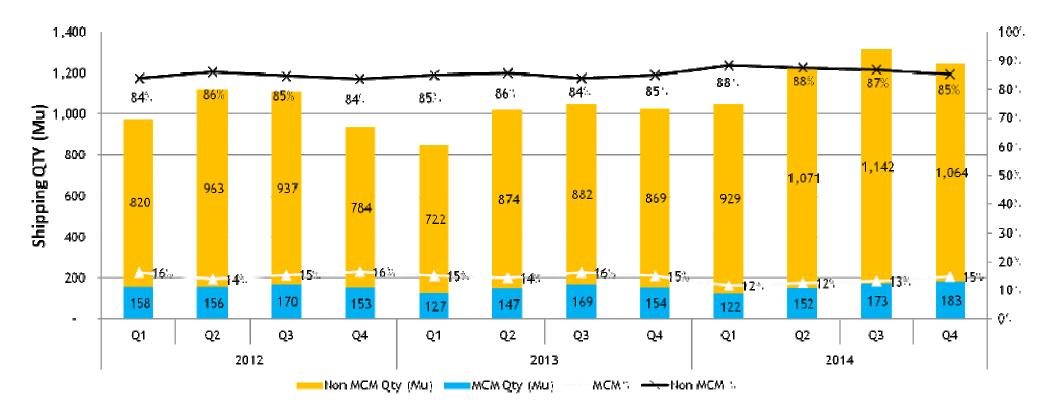

#### **Multi-Dice Loading Trend**

#### • Data covers WB and Flip Chip products

| Year             | 2012 |       |       | 2013 |     |       |       | 2014  |       |       |       |       |

|------------------|------|-------|-------|------|-----|-------|-------|-------|-------|-------|-------|-------|

| Quarter          | Q1   | Q2    | Q3    | Q4   | Q1  | Q2    | Q3    | Q4    | Q1    | Q2    | Q3    | Q4    |

| MCM Qty (Mu)     | 158  | 156   | 170   | 153  | 127 | 147   | 169   | 154   | 122   | 152   | 173   | 183   |

| Non MCM Qty (Mu) | 820  | 963   | 937   | 784  | 722 | 874   | 882   | 869   | 929   | 1,071 | 1,142 | 1,064 |

| MCM %            | 16%  | 14%   | 15%   | 16%  | 15% | 14%   | 16%   | 15%   | 12%   | 12%   | 13%   | 15%   |

| Non MCM %        | 84%  | 86%   | 85%   | 84%  | 85% | 86%   | 84%   | 85%   | 88%   | 88%   | 87%   | 85%   |

| TTL Qty (Mu)     | 978  | 1,119 | 1,107 | 937  | 849 | 1,021 | 1,051 | 1,024 | 1,051 | 1,223 | 1,316 | 1,248 |

## **Yield Status**

#### Incoming Die

- Standard inspections, same as single die

- Probed before assembly

- Assembly

- ◆ 2 Dice : >= 99.9%

- ♦ > 2 Dice : >= 99.5%

- Wirebond, Flip Chip, and combination of both

- "Mature" subordinate die are commonplace

#### • Final Test

- Most customers are doing FT with BIST

- Typical Yields : > 98.5%

- Very few customers do full functional testing on memory after assembly

# 2.5D / 3D / SiP / SiM

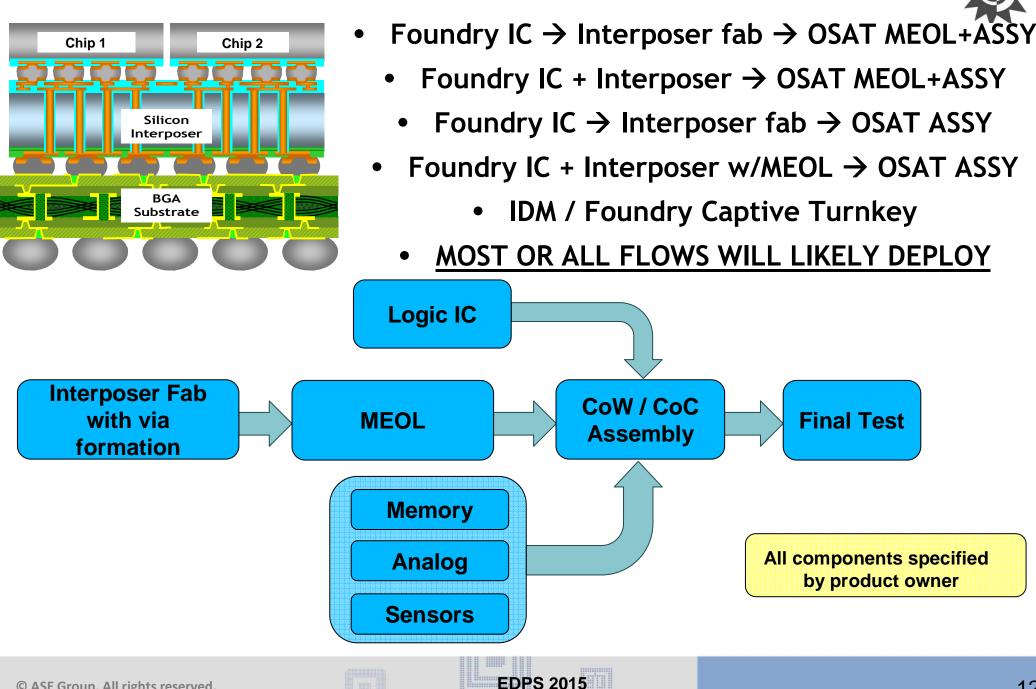

#### **2.5D IC Ecosystem Models**

#### Industry 2.5D / 3D IC Manufacturing Readiness

| Product Type                      |               | Oritoria            | 300 mm Wafer Readiness |              |        |  |  |  |

|-----------------------------------|---------------|---------------------|------------------------|--------------|--------|--|--|--|

|                                   |               | Criteria            | Y2009                  | Y2012        | Y2014  |  |  |  |

| Wafer Thinning / Grinding         |               | 50 µm               |                        |              |        |  |  |  |

| Via<br>Last                       | Via Etching   | 20 ~ 50 µm, AR 10   |                        |              |        |  |  |  |

|                                   | Via Isolation | 20 ~ 50 µm, AR 10   |                        |              |        |  |  |  |

|                                   | Via Seedlayer | 20 ~ 50 µm, AR 10   |                        |              |        |  |  |  |

| Via<br>First                      | Via Etching   | 5 ~ 10 µm, AR 10    |                        |              |        |  |  |  |

|                                   | Via Isolation | 5 ~ 10 µm, AR 10    |                        |              |        |  |  |  |

|                                   | Via Seedlayer | 5 ~ 10 µm, AR 10    |                        |              |        |  |  |  |

| Thin Wafer Handling               |               | 50 µm               |                        | With Carrier |        |  |  |  |

| Via Surface Finish                |               | No Cu Dishing       |                        |              |        |  |  |  |

| Re-distribution (Double<br>Sides) |               | -                   |                        |              |        |  |  |  |

| Micro-bumping                     |               | 30 µm Pitch         |                        |              |        |  |  |  |

| TSV Wafer Probing & Testing       |               | 30 µm Pitch         |                        | 50 um Now    |        |  |  |  |

| Wafer Singulation                 |               | -                   |                        |              |        |  |  |  |

| CtW/CtS Bonding                   |               | Solder / Micro Bump |                        | тсв          | Reflow |  |  |  |

| Assembly                          |               | -                   |                        |              |        |  |  |  |

| Final Test                        |               | -                   |                        |              |        |  |  |  |

Ready for Mass Production Ready for Qualification

**Ready for Prototyping**

No Solution Yet

## 2.5/3D IC Test Challenges

#### ASE GROUP • Wafer Probing • Package Test Heterogeneous cores • Thinned wafer handling Logic + analog + memory » Grinding before/after test **Embedded** passive » Assembly flow vs. Test Embedded die • TSV test Assembly and test process flow » TSV defect integration » Double-sided wafer probing? • Die/wafer contact interface material Test Methodologies » Bond pads/ micro bumps/ KGD fault coverage TSV New fault types » Cu pillars DFT • Contact force of high I/O number vs System Level test wafer thickness » Probe Force Cost of test » Probe material One insertion/multi insertions • Fine Pitch **ATE or Customized Bench** » Area array pitch < 50um > 1000 contacts Fundamental Study Capability Is Required Joint Development among IC Design/ for Assembly and Test Subcontractors Foundry/ Assembly & Test companies

**EDPS 2015**

# Design and Co-Design: an OSAT Perspective

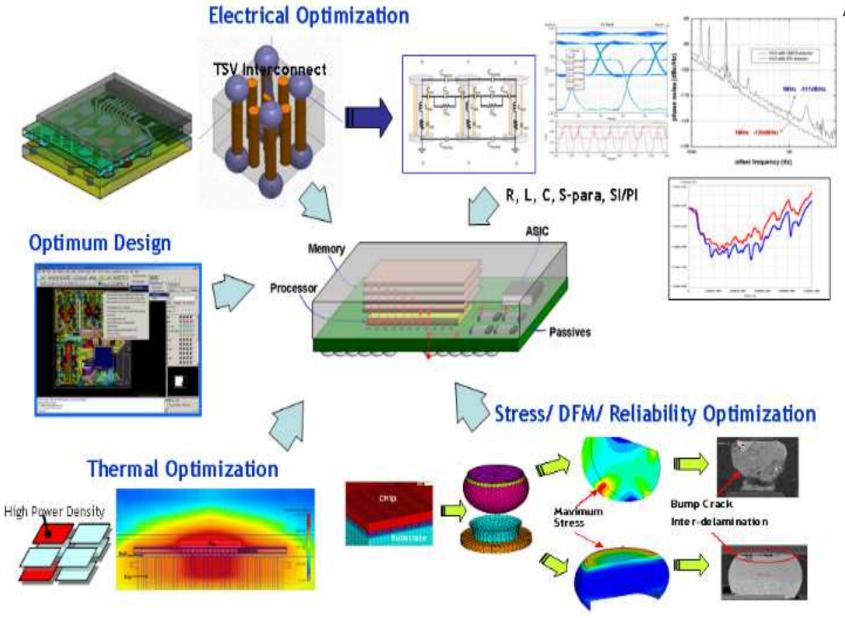

#### 3D IC Concurrent Package & System Modeling & Validation

**EDPS 2015**

# Summary

#### Summary

- Industry drive towards functional integration is at an all time high

- Multi chip packaging has been practiced in large volume, but simpler formats

- SiP, as well as 2.5/3D products, bring a heightened level of complication related to physical interconnect, cost, and business models to produce them.

- Modeling and simulation must be enhanced to enable 2.5/3D products due to sub-system and system level performance requirements

## **Thank You**

www.aseglobal.com