#### 3D-IC Designs for Power, Performance, and Cost

Brandon Wang

Group Director, Strategic Program at Cadence 04-23-2015

cādence°

### Short-, medium-, and long-term path to 3D-IC

© 2015 Cadence Design Systems, Inc. All Rights Reserved. 2

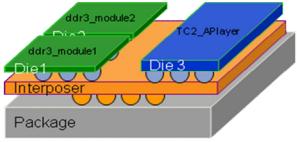

# 2.5D Silicon Interposer for Performance Driven Applications

- Interposer enables high performance/high bandwidth applications through massive interconnects among dies, particularly logic dies and memory dies;

- TSVs in SI Interposer die provide shorter routes for high speed signals, and deliver adequate power/ground connections to both logic and memory dies;

- Metal mesh and MiM Cap in Silicon interposer further enhance the performance through better SI and PI

- Silicon interposer as better heat conductor for improved thermal dissipation for higher performance

cādence

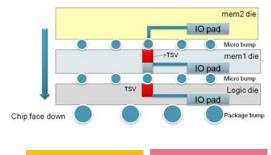

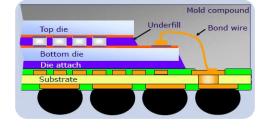

# **3D Stack and/or Monolithic 3D for lower cost**

Interconnect

(Solder ball)

- No additional SI Interposer cost

- TSV-Less Integration

- No wafer thinning, less yield loss

- Face2face uBump connection for multi-die stack

- Integrated Fan out WLP

Mold Compound

Redistribution

Chip

Tier 1

Tier 0

Monolithic 3D-IC

4 © 2015 Cadence Design Systems, Inc. All Rights Reserved.

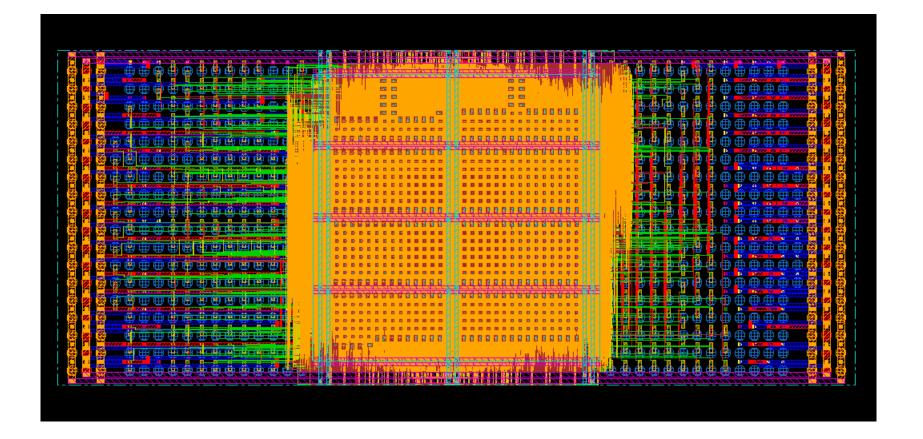

#### 3D-IC using uBumps for inter-die P&R Optimization using EDI/Innovus

cādence°

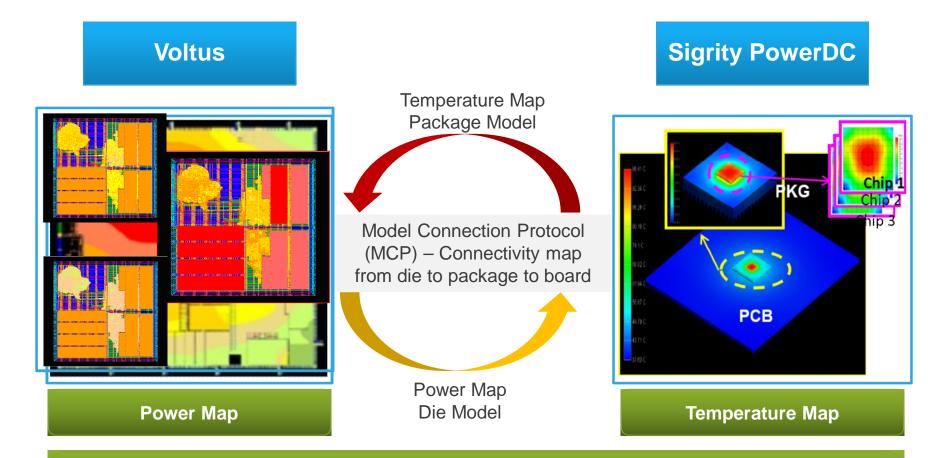

# Multi-Dies-package-board thermal co-simulation

Sigrity PowerDC computes Temperature map including multiple dies, package and board

cādence<sup>°</sup>

- Voltus computes temperature dependent Power map of each die (leakage, dynamic)

- Iterate co-simulation until results converge ( equilibrium, transit)

# Summary

- Different 3D-IC integration technologies are needed for high performance centric, or low cost applications;

- All 3D-IC integration technologies, whether high performance, or lower cost, will reduce system power consumption;

- IoT, Wearable in consumer applications will drive the TSV less 3D integration technologies such as InFO WLP to mass production;

- Monolithic 3D integration will both bring even higher performance and lower power in smaller form factor in near future;

- Implementation method varies for different 3D integration technologies, but electrical and thermal co-analysis are commonly required at die-package at plan/design phases.

# cādence®