## **Beyond Soft IP Quality to Predictable Soft IP Reuse**

TSMC 2013 Open Innovation Platform® Presented at Ecosystem Forum, 2013

Open Innovation Platform®

## Agenda

**Soft IP Quality – Establishing a Baseline With TSMC**

Soft IP Quality – What We Checked and What We Found

Soft IP Reuse – Methodology and RTL Signoff

Summary and Next Steps

## **TSMC & Atrenta IP Kit - History**

#### Atrenta Announces SpyGlass Tool Used in TSMC Soft IP Qualification Flow

Quality reports generated by SpyGlass® to be available on TSMC web site

San Jose, Calif. and HSINCHU, Taiwan, R.O.C. — May 26, 2011 — Atrenta Inc. today announced the deployment of a comprehensive soft IP qualification program using Atrenta's SpyGlass® platform and a targeted subset of

#### Atrenta and TSMC IP Quality Initiative Gains Broad Industry Acceptance

SAN JOSE, Calif. - March 5, 2012 - Atrenta Inc., a leading provider of SoC Realization solutions for the semiconductor and electronic systems industries, today announced that 10 intellectual property (IP) providers have qualified their soft IP for inclusion in the TSMC 9000 IP library using the Atrenta IP Handoff Kit.

#### Atrenta and TSMC Announce SpyGlass® IP Kit 2.0 Availability

Digi Inc.;

info

sem

its G

qua

TSN

New soft IP qualification platform more comprehensive and easier to use

SAN JOSE, Calif and HSINCHU, Taiwan, R.O.C. — Oct 31, 2012 — Atrenta Inc., the leading provider of SoC Realization solutions for the semiconductor and consumer electronics industries, with TSMC announced today the planned availability of IP Kit 2.0.

© 2013 Atrenta Inc.

7

## **TSMC/Atrenta Collaboration**

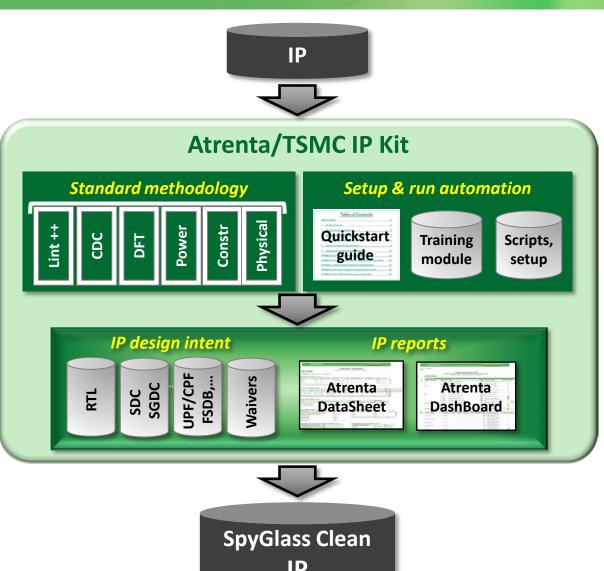

Golden Rules for soft IP handoff analysis

- Definition of quality metrics to assess soft IP

- Modified severity of errors to conform to quality requirements

- Enable various IP packaging types

- Optimize work flow to ensure ease-of-use and reliable, fast operation

- Tuned mandatory vs. optional goals

- Joint roll out plan development and beta testing with IP partners

- Ease of use a critical requirement

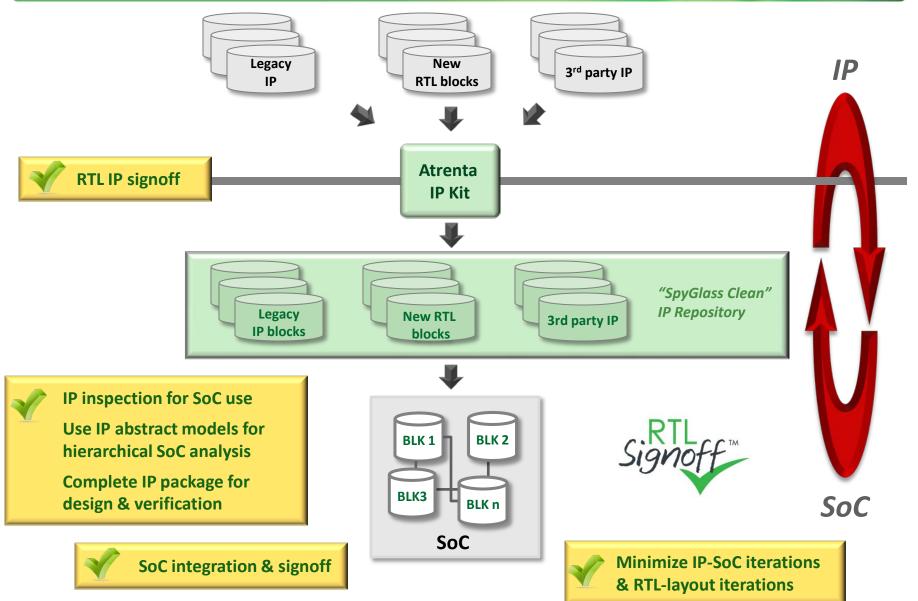

## **IP Kit – Establishing IP Quality Baseline**

**IP**

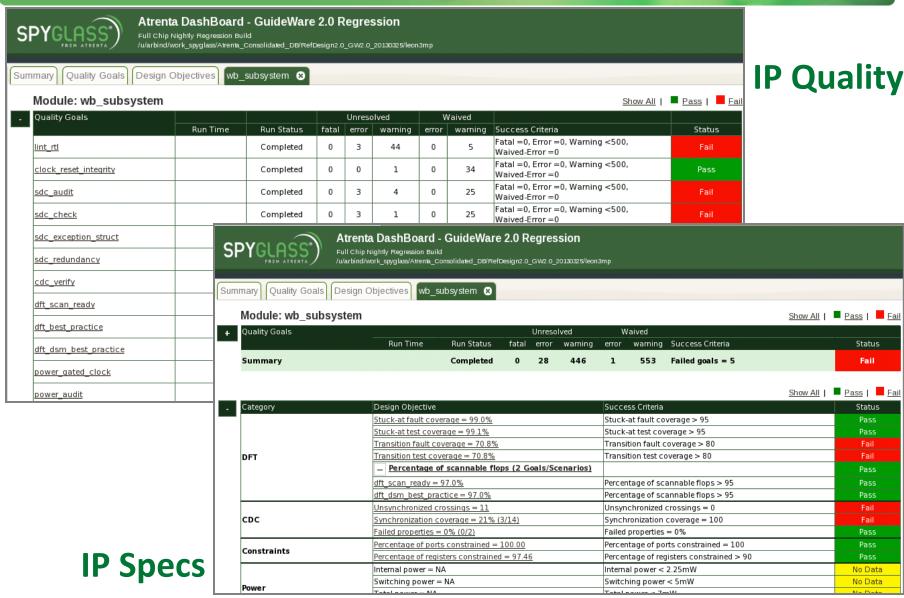

## **IP DashBoard Report**

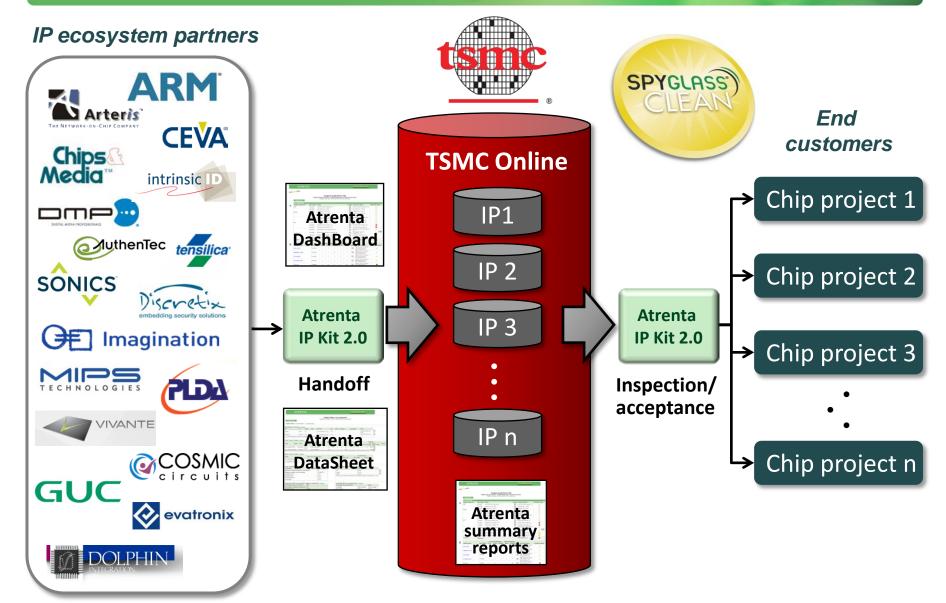

## **TSMC Soft IP Qualification Program**

## **Strong Uptake on the Program**

#### **DAC 2012**

#### **DAC 2013**

## Agenda

■ Soft IP Quality – Establishing a Baseline With TSMC

Soft IP Quality – What We Checked and What We Found

Soft IP Reuse – Methodology and RTL Signoff

Summary and Next Steps

## **IP Kit – Sample Tests**

Power

What will the average power dissipation be?

Are my power domains correctly defined?

Are clock and reset constraints set properly?

Are clock definitions consistent, correct and complete?

Clocks & Timing

- Are clock domain crossing synchronizers bug-free?

- Are timing constraints consistent across block boundaries?

- Are false path and multi-cycle paths correctly identified?

Lint

Is the design ready for simulation and synthesis?

What will the stuck-at and at-speed test coverage be?

Can all sequential elements be scanned?

#### What Did We Find?

# Many items that would impact integration/debug time and chip function were found & fixed

#### Some examples:

- Missing synchronizers on CDC paths causing possible chip function issues

- Data loss on fast-slow CDC paths

- Uncontrolled data path impacting transition fault coverage

- Index out of range which causes synthesizability issues

- Unconstrained I/O ports leading to poor SDC coverage

Faster time to silicon

## Agenda

- Soft IP Quality Establishing a Baseline With TSMC

- Soft IP Quality What We Checked and What We Found

Summary and Next Steps

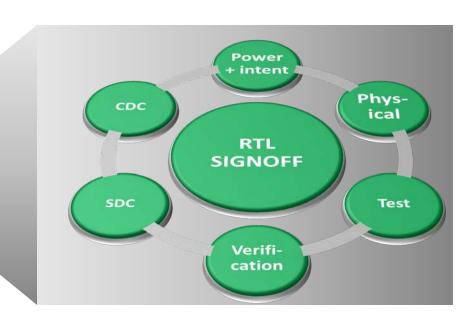

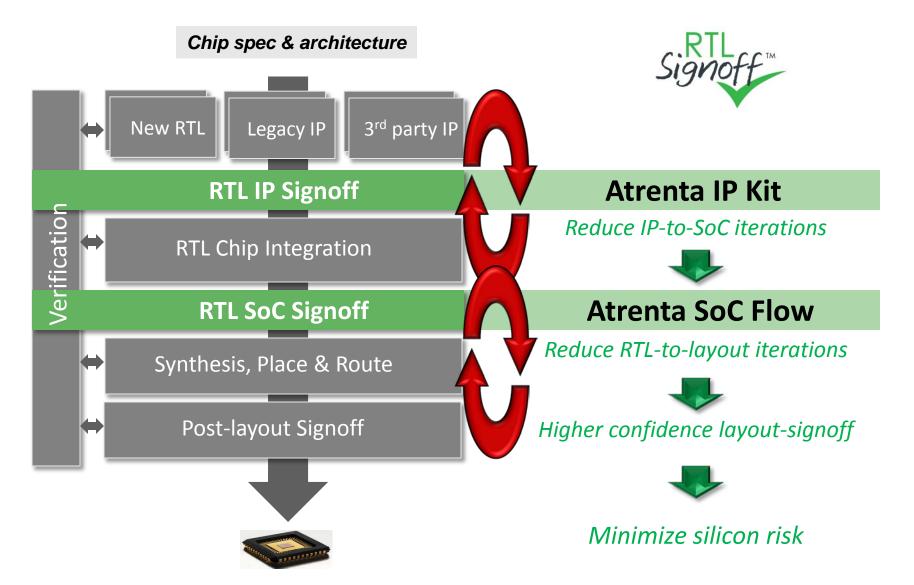

## Journey – Soft IP Quality to Soft IP Reuse

- Soft IP quality is a necessary but not sufficient condition for soft IP reuse

- Enforcing a known standard of quality for IP blocks is important

- How those blocks are assembled is just as important

- The concept of <u>RTL Signoff</u>\* is a critical enabler for successful soft IP reuse

\* RTL Signoff: A series of must-pass requirements before the flow proceeds

## **Traditional Signoff**

#### A series of <u>must pass</u> requirements before tapeout

- Typically done post-layout

- Requires iterations with layout, synthesis and even RTL

- Design convergence becomes worse at 28→14 nm

- 3<sup>rd</sup> party IP's further increase the design risk

- Too late in the flow, too much design risk

RTL **Synthesis** Layout **SIGNOFF** Fab

Traditional signoff no longer sufficient

## **RTL Signoff Emerges**

RTL

**RTL SIGNOFF**

**Synthesis**

Layout

**LAYOUT SIGNOFF**

Fab

#### A series of <u>must pass</u> requirements before synthesis

- Does not replace, but augments post-layout signoff

- Minimize late stage surprises & iterations

- Must be applied to the entire design including 3<sup>rd</sup> party IP's

- Run times are an order of magnitude faster than post-layout

Only viable approach to address soft IP reuse

## **RTL Signoff Requirements**

| Signoff Domain     | MUST PASS Requirements                                                                                                                           |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Verification       | <ul> <li>✓ Functional coverage signoff</li> <li>✓ High quality assertions checked into simulation regressions</li> </ul>                         |  |  |  |  |  |

| CDC                | <ul> <li>✓ Clock, reset, data synchronization signoff</li> <li>✓ Static (structural + formal), Dynamic (simulation) signoff</li> </ul>           |  |  |  |  |  |

| SDC                | <ul> <li>✓ Complete and consistent SDC to synthesis</li> <li>✓ False &amp; multi-cycle paths fully verified</li> </ul>                           |  |  |  |  |  |

| Power intent (*PF) | <ul> <li>✓ Power intent (UPF/CPF) signed off</li> <li>✓ Must be done before &amp; after insertion of level shifters, isolation logic,</li> </ul> |  |  |  |  |  |

| Power              | <ul> <li>✓ Efficient clock gating for registers and memories</li> <li>✓ RTL meets power spec - taking into account physical effects</li> </ul>   |  |  |  |  |  |

| Test               | <ul> <li>✓ RTL meets stuck-at test coverage requirements</li> <li>✓ RTL meets at-speed test coverage requirements</li> </ul>                     |  |  |  |  |  |

| Physical           | <ul> <li>✓ RTL is congestion-free,</li> <li>✓ RTL meets area &amp; timing targets</li> </ul>                                                     |  |  |  |  |  |

RTL Signoff applies to IP/blocks and full SoC

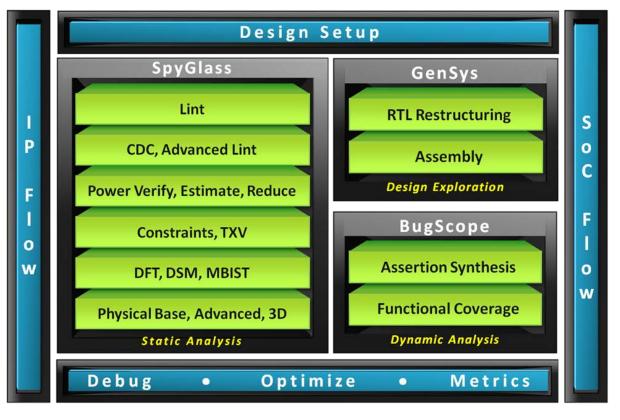

## **Complete Platform for RTL Signoff**

## **RTL Signoff with Atrenta**

## Agenda

- Soft IP Quality Establishing a Baseline With TSMC

- Soft IP Quality What We Checked and What We Found

- Soft IP Reuse Methodology and RTL Signoff

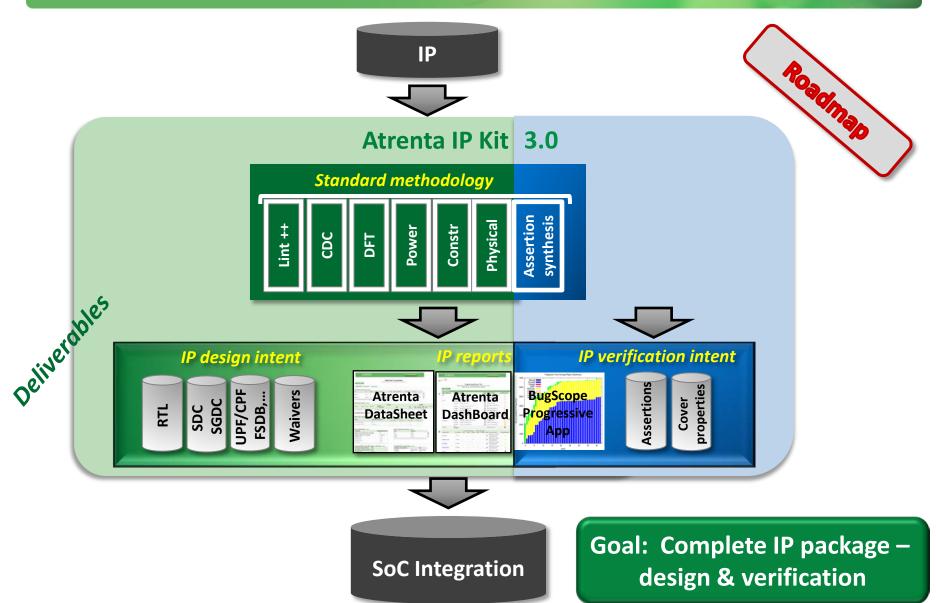

### Atrenta IP Kit 3.0 – Includes Verification

### **Hierarchical SoC Abstraction Flow**

21

|               |                 |             | Runtime [Hrs] |      | Memory GB |      | # Violations |      |

|---------------|-----------------|-------------|---------------|------|-----------|------|--------------|------|

| Design        | Size<br>[Gates] | #<br>Blocks | Flat          | Hier | Flat      | Hier | Flat         | Hier |

| Graphics chip | 1,4 B           | 14          | 96            | 2    | 1300      | 100  | > 1 M        | 346  |

| Networking    | 155 M           | 12          | 20            | 0.5  | 300       | 30   | 6678         | 2    |

| D-TV chip     | / 110 M         | 26          | 33            | 1    | 400       | 50   | 1289         | 102  |

| Mobile phone  | 100 M           | 9           | 8             | 0.5  | 200       | 40   | 1687         | 200  |

**Billion+ gate capacity**

**15-50X faster**

**5-10X lower memory**

Goal: Manage Complexity

**10-100X reduction in noise**

## Soft IP Reuse – The Big Picture

## Thank you!