# Improved Circuit Reliability/Robustness

## **Carey Robertson**

*Product Marketing Director* Mentor Graphics Corporation

## Reliability Requirements are Growing in all Market Segments

Transportation

General CPU / Server Farms

- Exhaustive specs/testing for reliability

- Chips need to be robust against a number of extreme environmental factors

- Stable platform for 10+ years

- Pushing the limits of low power, performance and functionality

- Smaller nodes => smaller oxides

- Heterogeneous on-chip content drives higher probability of latch-up, cross-power domain issues

- Aggressively pursuing smallest process node, performance and functionality. .

- Design complexity very high. Often an SoC with many (internal) IP providers. Higher probability of latch-up, cross-power domain issues

## **Limitations of Traditional Verification**

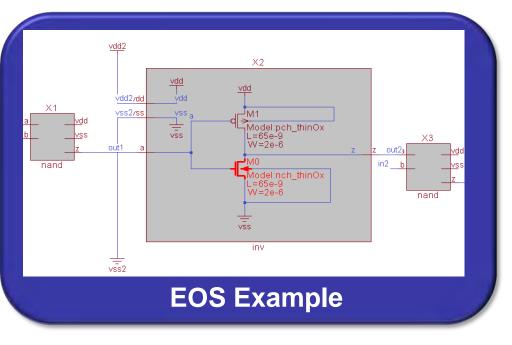

Circuit Failure due to Electrical Overstress (EOS)

- Thinner-oxide is lower voltage is less power

Some power domain design errors lead to oxide breakdown and failure over time. NBTI (PMOS), HCI (NMOS), SBD

- Complex Management of *bulk* and *power* pins

- IP blocks may have internal global signals

# LVS:<br/>Schematic Matches LayoutXSchematic Correct?Simulation:<br/>Static TimingXCircuit SimulationX

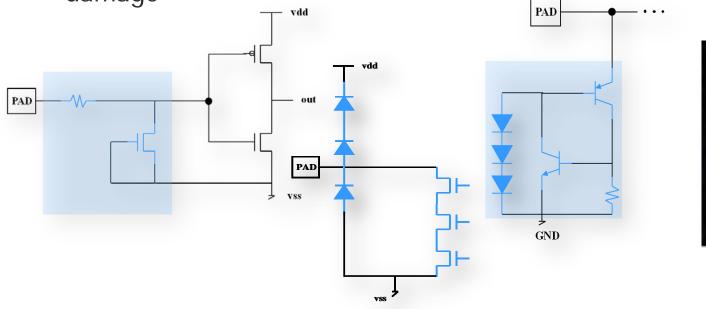

## **ESD Design Rules**

- Electrostatic discharge (ESD) causes severe damage to ICs

- Several protection schemes have been proposed to mitigate this damage

#### Checking for proper ESD protection circuits is needed for reliable design

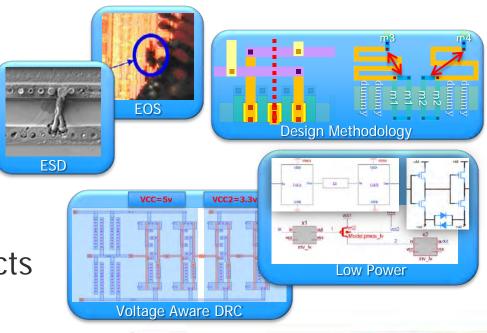

# **A Reliability Verification Platform**

- Calibre PERC provides a robust platform for circuit reliability verification

- Not just a point tool solution

- A system view of how design elements interact is needed

- Used throughout the design flow: schematic, layout, final verification

- Typical application areas

- ESD

- EOS

- Voltage-aware DRC

- Low/Multi-power designs

- Latch-up

- Understand IC layout impacts on device performance

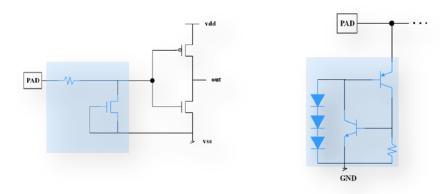

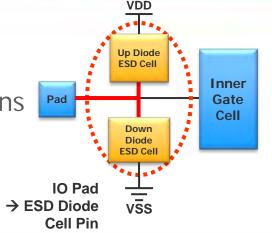

## **ESD Verification** Device and Cell Based Verifications

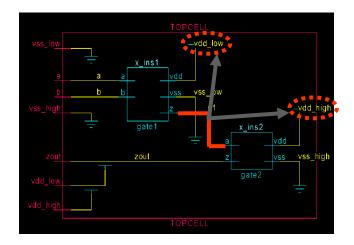

- Topological and Layout based checks

- Reference cell names

- Verify signals crossing multiple power domains

- Addresses reliability concerns / EOS

- Layout centric verification with P2P, CD and DRC

- Logic Driven Layout (LDL)

- User defined checks and feedback

**Current density simulation**

© 2012 Mentor Graphics Corp. Company Confidential www.mentor.com

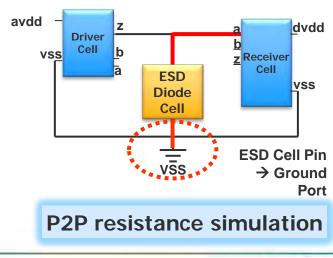

## Understanding EOS without Simulation Voltage Propagation

- EOS has historically been one of the leading causes of integrated circuit failures, regardless of the semiconductor manufacturer

- The result of an EOS event can range from no damage or degradation to the IC up to catastrophic damage where the IC is permanently non-functional

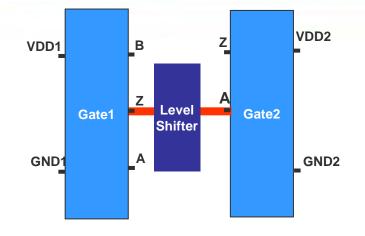

## **Power Domain Checking**

- Multi-power verification requires system knowledge

- Tracking of large numbers of domains

- PERC identifies power regions

- Verifies appropriate level-shifting circuitry

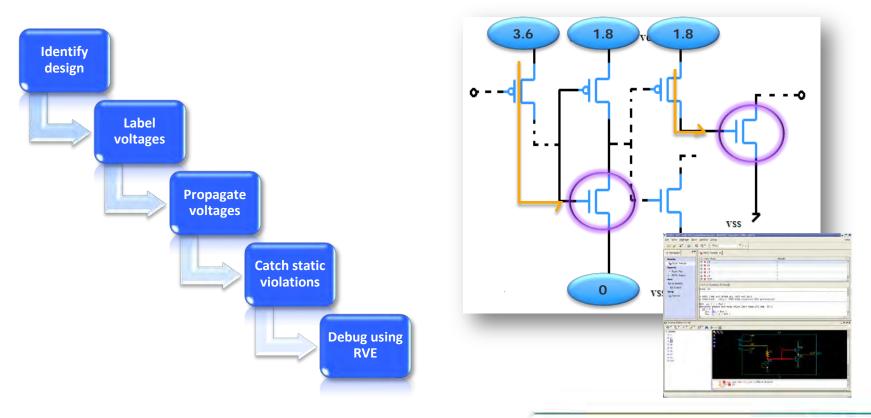

## **Post-Layout Verification** Topology-based Geometrical Checking

## Partnering with TSMC

### Improving ESD coverage

- Traditional DRC/LVS decks car coverage of TSMC's rules

- Having rules that can not be ea problem for everyone: TSMC, Il customers

- The workaround of marker laye errors

- Error costs are increasingly expe but more importantly product dela

## Better ESD coverage with Calibre PERC

- TSMC has selected Calibre PERC as the first solution to provide the required ESD and ERC coverage

- The use of Calibre PERC will become a requirement for TSMC9000 in N20SoC, N16FF and below

- Calibre PERC decks are planned for N28 as well

- For IP Alliance partners

SOLD TSUCH IN

Mentor and TSMC will work with you for accessing Calibre PERC for the new reliability checks

#### Open Innovation Platform\*

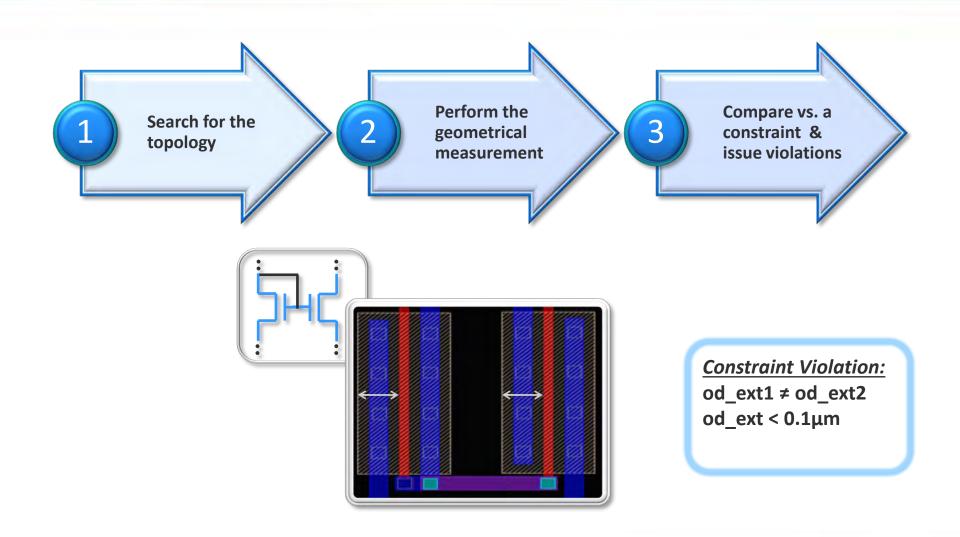

## **Reliability Rules Are Complex**

- ESD/Latch-up Rules

- 35% of ESD and latch-up rules "un-checkable" with standard EDA tools

- The other 65% of rules need additional manually-placed marker layers

## **TSMC9000 with Calibre PERC**

## Focus on three categories of rules

— Example checks shown, final determination underway

|                                | Rule Description                                                                                                      |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| IO Cells                       | most of rules in DRM ESD/LUP kit are applicable                                                                       |

| IP with multiple power domains | CDM rules are applicable                                                                                              |

| analog IP                      | No dangling input / output port<br>MOS gate can't directly connect to power<br>MOS can't directly connect to I/O port |

|                                | for logic gates in two different power domains, there must be appropriate protection                                  |

|                                | MOS connect to pad through resistor can't connect it's gate directly to power or ground                               |

Analog IP here, includes Interface IP, mixed signal, etc.

Other categories explored with additional IP

## Industry Support Customer Adoption/Industry Validation

#### FOR IMMEDIATE RELEASE For more information, please contact:

Gene Forte Mentor Graphics 503.685.1193 gene forte@mentor.com Sonia Harrison Mentor Graphics 503.685.1165 sonia harrison@mentor.com

#### Mentor Graphics and TSMC Collaborate to Improve and Exp IC Physical Verification Offering

#### Calibre PERC Kit for N20 Now Available

WILSONVILLE, Ore., May 28, 2013—Mentor Graphics Corp. (NASDAQ: MEN announced significant achievements in its continued collaboration with TSMC on 2 verification kit optimizations. This joint effort has reduced Calibre® nmDRC<sup>TM</sup> 20 runtimes by at least a factor of 3X and memory requirements by 60% compared to

kits released last year. In addition, Calibre PERC<sup>™</sup> N20 design kits are now available to TSMC customers as part of the companies' ongoing collaboration for IC reliability improvement. The collaboration will continue as mutual customers ramp their releases of N20 production designs, with the goal of maintaining rapid turnaround on full-chip signoff runs for the largest SoC designs in the industry.

Winner of the Customers' Choice Award at TSMC's 2011 Open Innovation Platform<sup>®</sup> Ecosystem Forum

#### News Rel NEWS ANNOUNCEMENT

Graphics

FOR IMMEDIATE RELEASE

TowerJazz Releases Rule Decks for Advanced ESD and Power Domain Checking Using Mentor's Calibre PERC

MIGDAL HAEMEK, Israel and WILSONVILLE, Ore., March 4, 2013 – TowerJazz, the global specialty foundry leader, has announced the Mentor®'s Calibre® PERC™ rule decks are now available for TowerJazz customers to perform circuit reliability verification for its latest 0.18 micron products, including highly customized electrostatic discharge (ESD) and power management circuit checks. Many of these checks have been automated for the first time by taking advantage of the Calibre PERC product's unique ability to combine schematic (netlist) and physical lavout information

Electronic Products Magazine 2009 Product

© 2012 Mentor Graphics Corn. Company Confidential www.mentor.com

# **THANK YOU!**