## **Making Design Reuse Work**

**Ranjit Adhikary**

## ClioSoft – a brief introduction

- Founded in 1997. Headquartered in Fremont, CA

- Over 150+ customers ...

- Provides software for collaborative design release and derivate management & IP Management

- Integrated with tools from Cadence, Synopsys, Mentor

Graphics & Agilent technologies

Mission: Improve productivity of design teams

# Challenges faced by SoC designers

- Shrinking time-to-market window

- Changing consumer demands

- Increased competition

- Increasing SoC Complexity

- Digital convergence; more and more IPs being integrated on a single chip.

- Increased use of analog designs

- Shrinking process technology

- Increase designer productivity to keep pace with Moores law

- Integrating more and more functionality on a chip has always existed as a trend

#### The solution

- Hire more designers across geographical boundaries

- Move from ad hoc block reuse to reusing aggregates of IP blocks and a integration platform

- Helps reuse best architectures and design approaches

- Reduces design effort and risk

- Improves time to market

- ☐ Improved design flow methodologies.

- Work with EDA vendors

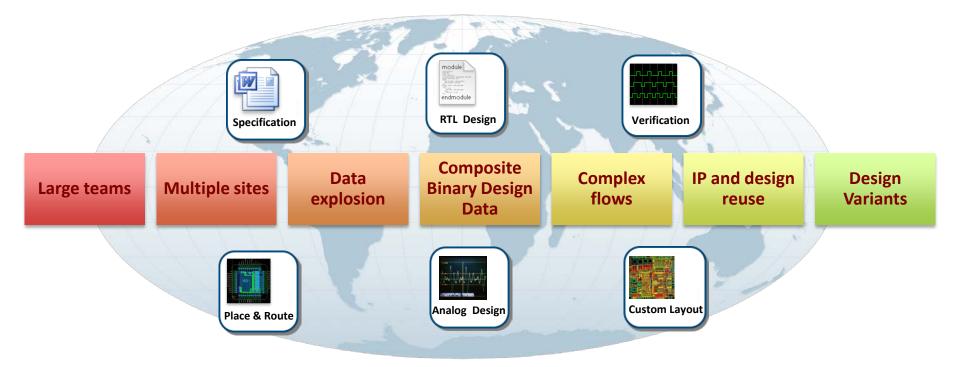

# But new problems emerge... (1/2)

#### Remote design sites

- Designers in different sites must communicate & collaborate closely.

- Large amounts of data must be synchronized between the groups and individuals efficiently & accurately.

- Release and derivative management needs to be managed.

- Track changes & keep backup revisions

# But new problems emerge... (2/2)

#### IP Reuse

- Ensuring functional correctness of the IP

- Performance what if the final timing is not satisfied due to the IP

- Keeping track of the bug fixes and new updates to the IP's being integrated.

- Keeping track of the IP history when IP is partly modified

- Version Control

- Licensing issues

## Streamlined design process

- A 'data bus' to streamline the design process and helps collaboration

- Makes data synchronization & team collaboration efficient and predictable whether team members are in the same building or on the other side of the globe

- Integrated with version control, issue tracking & provides release & derivative management

- ☐ Better control and visibility Improved predictability

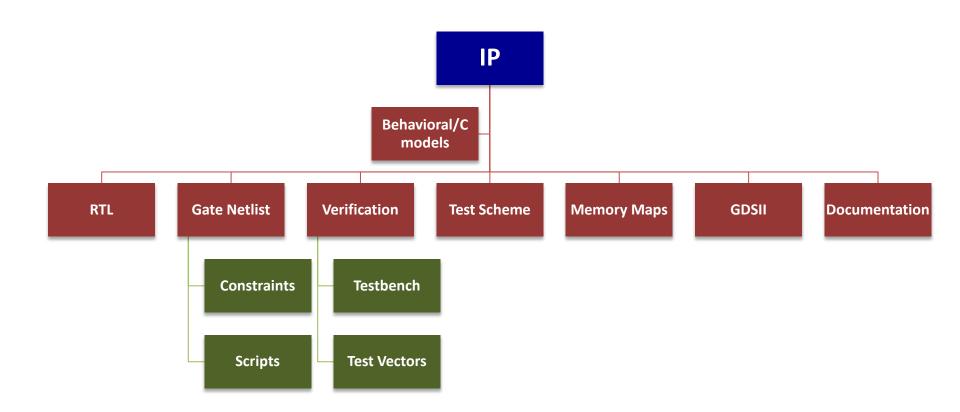

## **IP** Definition

Traditional definition of IP

### **IP** Definition

- Need to move beyond traditional definition of IP

- Must include scripts, methodologies

- Scripts for stitching IO Fabric

- Regression scripts

- Synthesis scripts

- Shareable documentation

Enables designers to leverage off existing work instead of reinventing the wheel

# Motivating designers to share

- Need to incentivize the designers to share their work

- Make designs reusable where possible

- Share ideas, scripts, documentation, work-around for known flow issues

- □ Carrot or the stick?

- Recognition (fame) is incentive to share knowledge/IP

- Corporate mandate

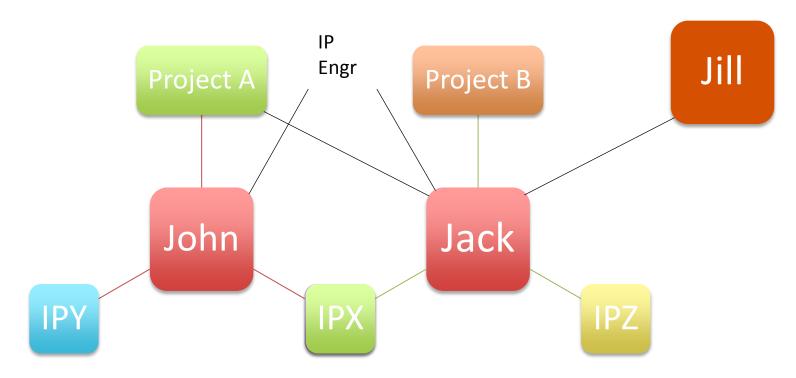

# User centric mode (1/2)

- □ Provide a forum for sharing the IP's.

- Enable designers to

- Follow IP's

- Read/Review

- Reference without modification

- Download and modify

- Publish document or IP and share with

- Selected groups

- Members of selected projects or IP

- All

# User centric model (2/2)

- □ Follow IP, Project, person or group

- News feed with updates from all followed sources

- Rating/like system to help grade quality

### **Conclusion**

- To increasing design reuse within a company

- Need to extend the definition of an IP

- Motivate users to collaborate

- Ability to leverage of databases

- Move from a IP centric to a user centric model