# Collaborate to Innovate – FinFET Design Ecosystem Challenges and Solutions

#### **Tom Quan**

Deputy Director, Open Innovation Platform®

TSMC

- Lifestyle Trends Drive Product Requirements

- Concurrent Technology and Design Development

- FinFET Design Challenges

- FinFET Ecosystem Solutions

- Lifestyle Trends Drive Product Requirements

- Concurrent Technology and Design Development

- FinFET Design Challenges

- FinFET Ecosystem Solutions

### **Future Lifestyle Trends**

**Mobile Convergence**

**Augmented Reality**

**Cloud Computing**

**Ubiquitous Connectivity**

**Internet of Things**

### **Enabling Product Requirements**

#### **Mobile Convergence**

#### Connectivity

- Integration

- Battery life

- Form factor

#### **Cloud Computing**

- Latency

- Throughput

- Performance/ W/ \$

- **Augmented Reality**

- Service availability

- Latency

- Bandwidth

- Battery life

- Service availability

- Bandwidth

- Battery life

**Ubiquitous Connectivity**

- Connectivity

- Reliability

- Battery life

- Cost

**Internet of Things**

### **Enabling Product Functionality**

#### TSMC Propert

#### **Mobile Convergence**

#### **Augmented Reality**

- CMOS Image Sensor

- Wireless Transceiver

- Pico Projector

- Gyroscope

- Accelerometer

- Power Management

- CMOS Image Sensor

- Wireless Transceiver

- Power Management

- Accelerometer

- Gyroscope

- E-Compass

#### **Cloud Computing**

Power Management

- Wireless Transceiver

- Power Management

- Micro-controller

- Wireless Transceiver

- Power Management

**Ubiquitous Connectivity**

**Internet of Things**

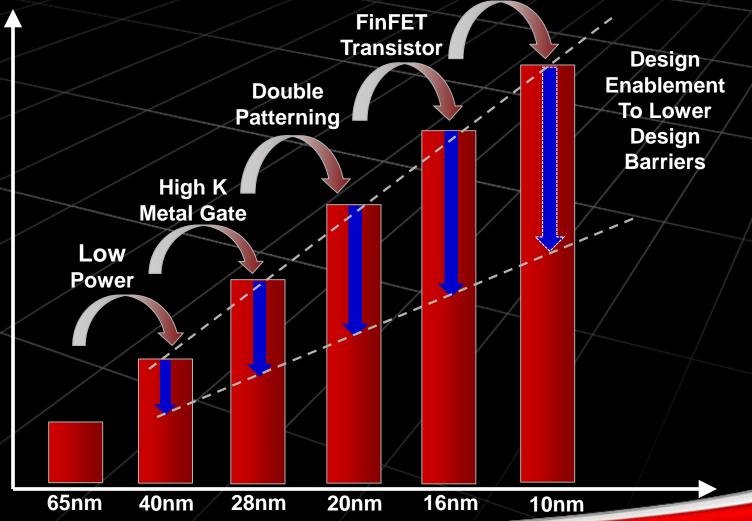

## Design Collaboration to Reduce New Technology Challenges

**Multi-Patterning & Spacer**

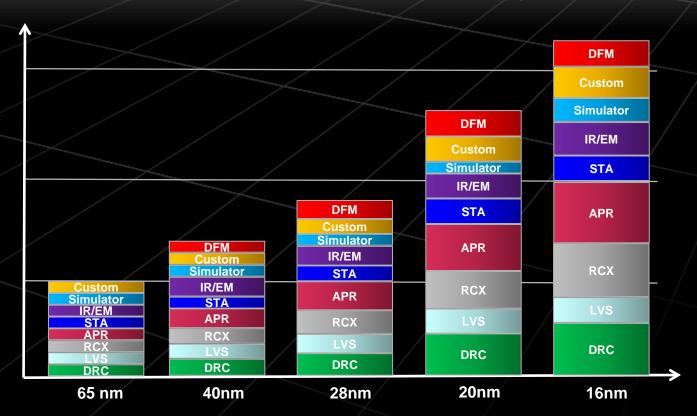

## Increasing EDA Tools and Feature Sets to Enable Customer Designs

**Number of Supported EDA Tools and Features by Process Node**

- Lifestyle Trends Drive Product Requirements

- Concurrent Technology and Design Development

- FinFET Design Challenges

- FinFET Ecosystem Solutions

### An Ecosystem for Innovation

TSMC Property

Customer Product Roadmap

Design Service Mask Making / OPC

**Process Definition**

**EDA**

**Enablement**

Design Enablement

Customer Tape-out

Design Productization

Test Chip Validation Wafer Fabrication

Backend Service

Customer Product Launch

IP Enablement

Open Innovation Platform®

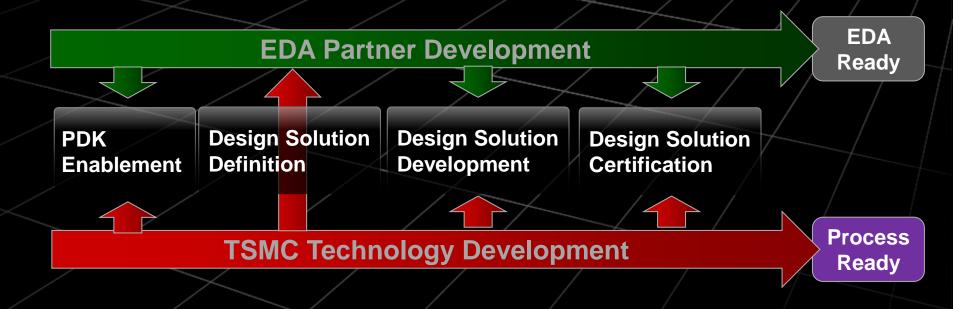

## Concurrent Technology and DesignEDA Partner Collaboration

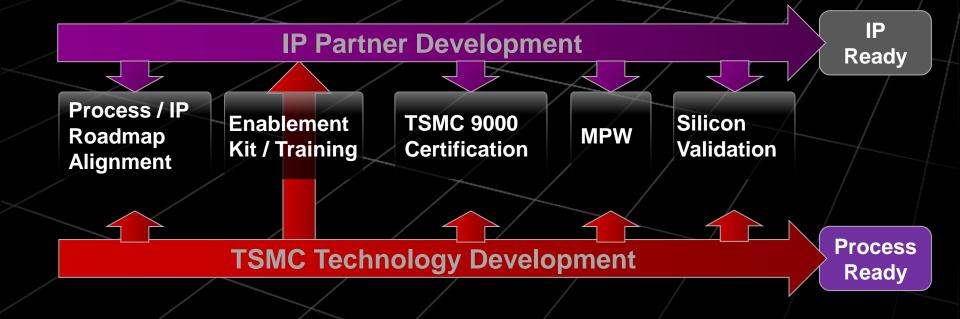

## Concurrent Technology and Design -- IP Partner Collaboration

### TSMC Bronethy

## Concurrent Technology and DesignDesign Partner Collaboration

TSMC Property

**Design Partner Development**

Design Ready

Technology Optimization TV Plan

Design Kits

Foundation IP

Design Guideline

**TV Validation**

Product Tapeout

**TSMC Technology Development**

Process Ready

## Concurrent Design & Technology Readiness

#### **TSMC-Online**

- Design rules

- SPICE model

- Tech files/PDK

- Design kits

- Utilities

- Ref Flow

#### **Certified EDA Tools**

- DRC/LVS/RC

- DFM

- P&R

- STA/IR/EM

- Simulation

- Layout editor

#### **Certified IP Portfolio**

- Foundation IP

- Interface IP

- Embedded CPU

- Embedded GPU

- Analog IP

- OTP/MTP

Design

- Lifestyle Trends Drive Product Requirements

- Concurrent Technology and Design Development

- FinFET Design Challenges

- FinFET Ecosystem Solutions

### A look back at 50 years of Silicon

**Julius Blank**

**Eugene Kleiner**

**Robert Noyce**

**Victor Grinich**

Jay Last

**Sheldon Roberts**

Jean Hoerni

**Gordon Moore**

### **Transistor to IC**

**First Transistor Bell Labs** 1947

First IC 1958

First Planar IC **Fairchild** 1960

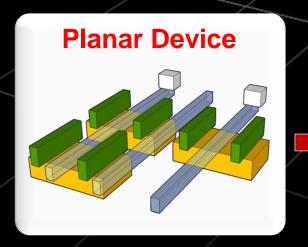

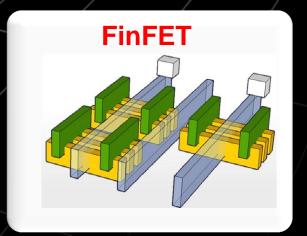

### FinFET vs. Planar Characteristics

- FinFET Benefits

- Lower leakage

- Higher driving current

- **■** Low-voltage operability

- Better mismatch

- **■** Higher intrinsic gain

- FinFET Challenges

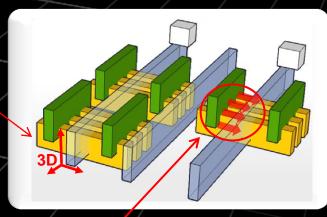

- Higher parasitic capacitance due to 3D profile

- Higher parasitic resistance due to local interconnect

- Quantized device widths

### **FinFET Value Proposition**

- ~2X gate density improvement compared to 28nm

- 16nmFinFET offers extra 20% speed gain @ same total power or 35% power saving @ same speed with similar gate density compared to 20nm

|                                 | <u>16FF</u> /28HPM | <u>16FF</u> /20SoC |

|---------------------------------|--------------------|--------------------|

| Speed @ same total power        | 38%                | 20%                |

| Total power saving @ same speed | 54%                | 35%                |

| Gate density                    | 2X                 | 1.1X               |

# FinFET Design Enablement Requires Collaboration Among Foundry, EDA and Lead Partners

- Parasitic RC extraction: 3D profile support, accuracy

- Design methodology for low voltage operation

- Design methodology for interconnect resistance minimization

- EM reliability and power integrity:

High drive current

- Lifestyle Trends Drive Product Requirements

- Concurrent Technology and Design Development

- FinFET Design Challenges

- FinFET Ecosystem Solutions

### FinFET Design Flow Requirements

- 3D FinFET device structure

- Advanced SPICE modeling for 3D structure

- Modeling layout dependent effects in 3D structure

- Accurate RC extraction

- Higher parasitic capacitance due to 3D profile

- Higher parasitic resistance due to local interconnects

- Quantized device width due to fin pitch/grid requirements

- PODE device handling in designs, EDA tools and IPs

- High-drive current leads to EM reliability and power integrity issues

### **FinFET EDA Tool Certification**

- Two levels of tool certification

- Tool certifications as the foundation of FinFET design infrastructure

Integrated Tool Certification

Using Cortex-A15

Tool Certifications

**Individual Tool Certification**

| STA | P&R | DRC | LVS              | FastSpice |  |

|-----|-----|-----|------------------|-----------|--|

| RC  | ЕМ  | IR  | Custom<br>Design | Lib Char  |  |

### Summary

Technology advancements are driving earlier, wider and deeper ecosystem collaboration to deliver enabling design solutions

- TSMC's collaborative ecosystem unleashes innovations to address FinFET design challenges

- TSMC Open Innovation Platform® has a proven record of success and is more critical than ever for 16nm and beyond