## Hybrid Memory Cube Mike Black

©2013 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings are not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

18 April, 2013

### The Situation

- Continued global demand for mobility

- Device proliferation

- Impact of the Cloud

- Big data analytics challenge

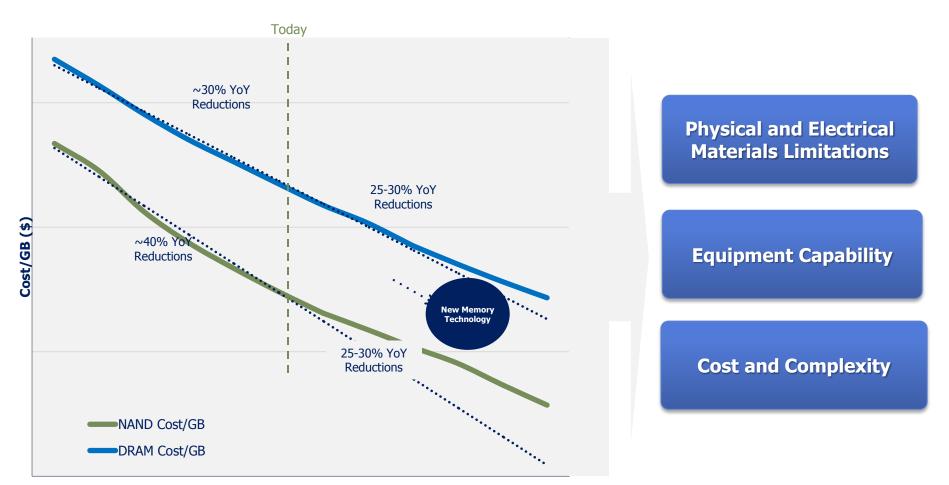

# The Roadmap

#### **Memory Cost Scaling Over Time**

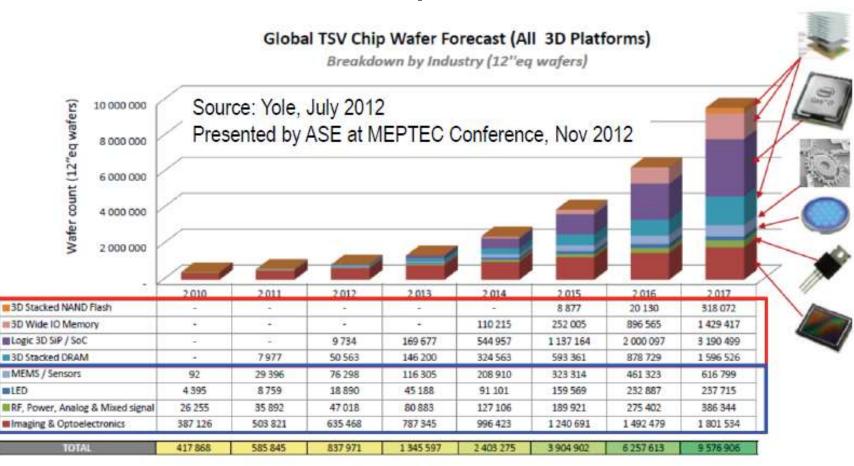

#### Global Revenue Forecast 3D TSV Devices

Comparison with total semiconductors market value (B\$)

\*: Excluding Interposer Revenues !

#### Global Forecast TSV Chip Wafers

Micron

### The Innovation: **HMC**

#### Revolutionary Approach to Break Through the "Memory Wall"

- Evolutionary DRAM roadmaps hit limitations of bandwidth and power efficiency

- Micron introduces a new class of memory: Hybrid Memory Cube

- Unique combination of DRAMs on Logic

#### **Key Features**

- Micron-designed logic controller

- High speed link to CPU

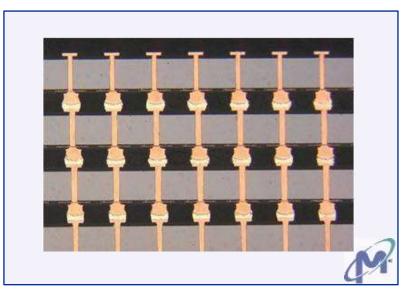

- Massively parallel "Through Silicon Via" connection to DRAM

#### **Unparalleled performance**

- Up to 15X the bandwidth of a DDR3 module

- 70% less energy usage per bit than existing technologies

- Occupying nearly 90% less space than today's RDIMMs

#### Full silicon prototypes in silicon **TODAY**

Targeting high performance computing and networking, eventually migrating into computing and consumer

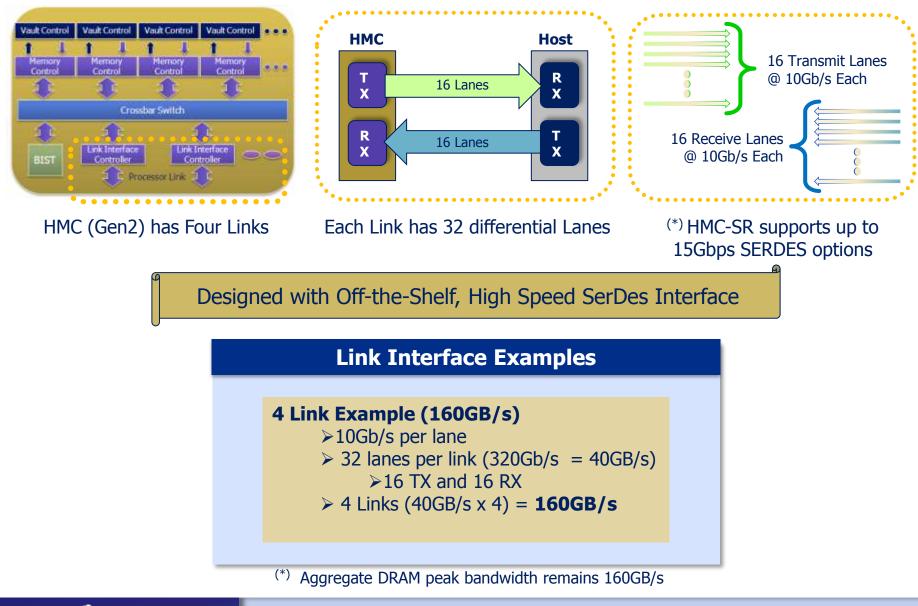

#### Link Controller Interface

#### **HMC Near Memory**

- All links between host CPU and HMC logic layer Processor Maximum bandwidth per GB capacity HPC/Server – CPU/GPU • Graphics •

- Networking systems

- Test equipment

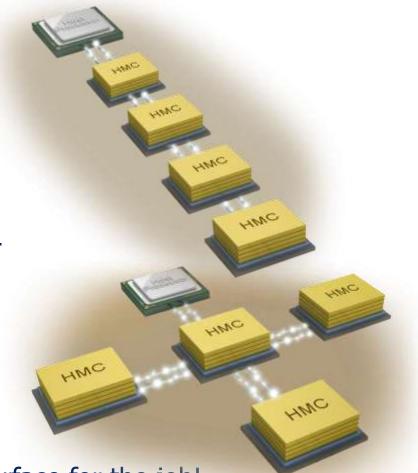

### HMC "Far" Memory

#### • Far memory:

- Some HMC links connect to host, some to other cubes

- Scalable to meet system requirements

- Can be in module form or soldereddown

- Future interfaces may include:

- Higher speed electrical (SERDES)

- Optical

- Whatever the most appropriate interface for the job!

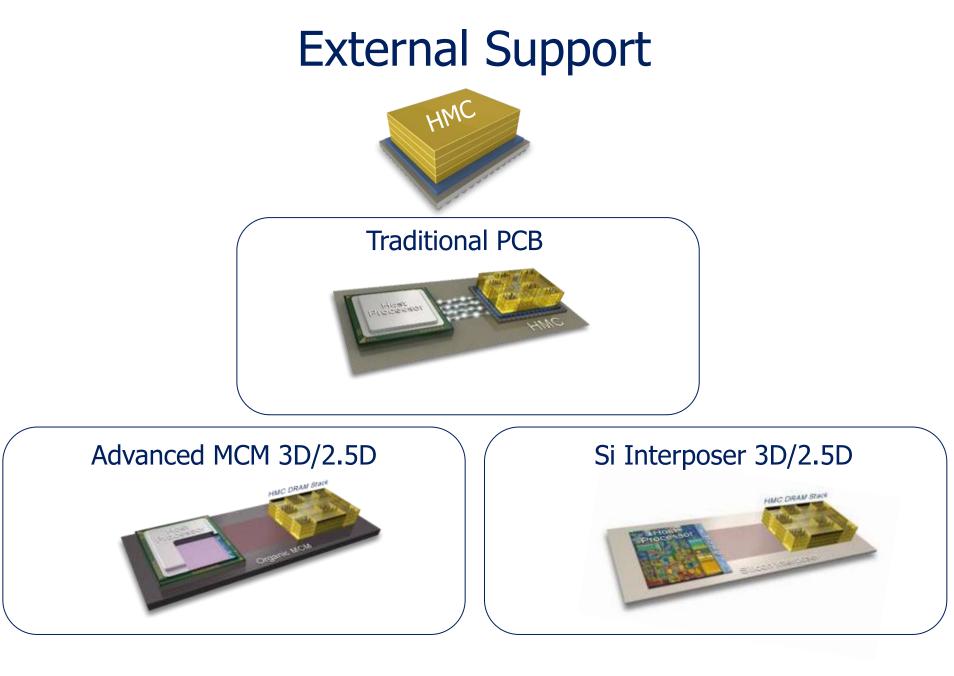

### The Requirements

- Major industry transitions demand innovative business models:

- Joint R &D efforts

- Agreed-upon design standards

- Cross-industry coordination

- Customer education and hands-on training

### **Internal Support**

- Micron design and verification tools

- Memory and logic design

- Interconnect modeling

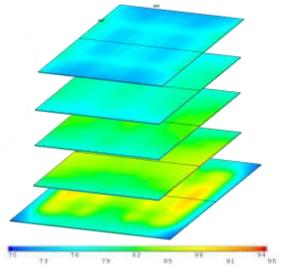

- Thermal modeling

### **HMC** Design Environment Examples

#### **Design of Memory Cells and Array Matrix**

| Design Ste               | р                 | Challenges           | EDA Solution                           |                  |  |  |

|--------------------------|-------------------|----------------------|----------------------------------------|------------------|--|--|

| Core Cells Optimization  |                   | Area, Speed, Power   | HSPICE, FineSim, Verilog               | $\checkmark$     |  |  |

| Drivers and Sense Amps   |                   | Speed, Noise         | HSPICE, FineSim, Verilog               | $\checkmark$     |  |  |

| Design of Logic Die      |                   |                      |                                        |                  |  |  |

| Design Ste               | р                 | Challenges           | EDA Solution                           | Status           |  |  |

| Core Logic C             | Optimization      | Area, Speed, Power   | Cadence RC, EDI, EPS,<br>ETS           | $\checkmark$     |  |  |

| I/O Drivers and Package  |                   | Speed, Noise, EM,    | Cadence ADE, Spectre,                  | $\checkmark$     |  |  |

| Integration in           | to a Printed Circ | VPS                  |                                        |                  |  |  |

| Design Ste               | р                 | Challenges           | EDA Solution                           | Status           |  |  |

| DC & AC Mo               | dels for I/Os     | Accuracy vs runtime  | Nimbic-Apex, Ansoft-<br>Q3D, TPA, HFSS | ✓                |  |  |

| Power & Ter              | np. Analysis      | For Die, Pkg, Board  | Icepack, FloTHERM                      | $\checkmark$     |  |  |

| System-level Integration |                   |                      |                                        |                  |  |  |

| Design Ste               | р                 | Challenges           | EDA Solution                           | Status           |  |  |

| HMC Function             | onal Model(s)     | Comply with Standard | To be determined                       | By Q2            |  |  |

| HMC Timing Model(s)      |                   | Language a, b, c     | To be determined                       | By Q2            |  |  |

| <b>April</b> , 2013      |                   | , 2013               | ©2013 Micron                           | Technology, Inc. |  |  |

Micron

18 April, 2013

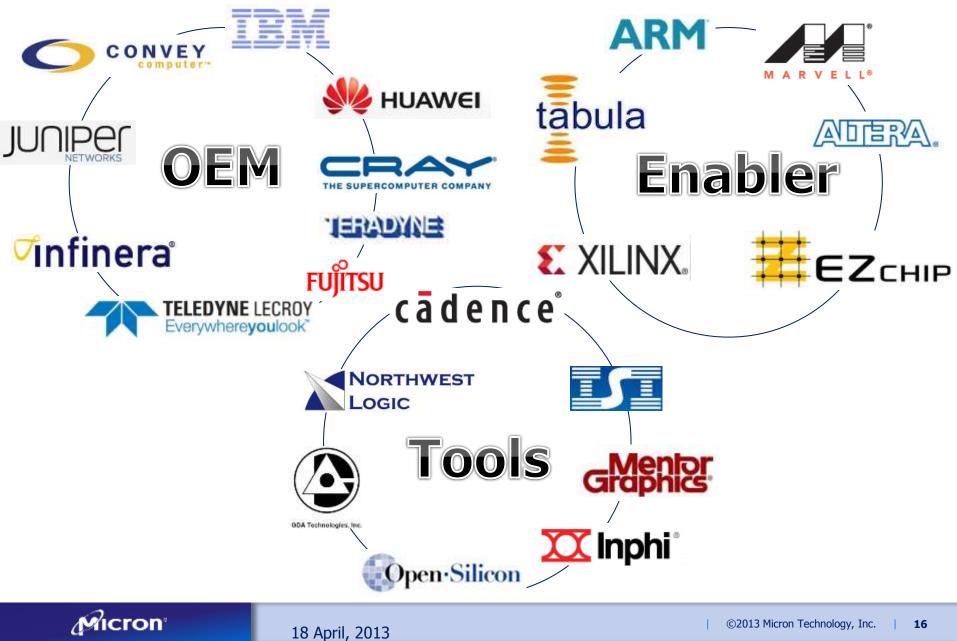

### **Broad Industry Adoption**

#### **HMCC Mission**

Promote widespread adoption and acceptance of an industry standard serial interface and protocol for Hybrid Memory Cube

http://www.hybridmemorycube.org/

### **HMC Consortium Update**

- HMCC specification final and available!

- Visit <u>hybridmemorycube.org</u> for more information.

- Developers working on next speed grade for SR and USR PHY:

- SR speed bump to 28Gb/s

- USR speed bump to 15Gb/s

| Over 100 Adopters to date!        |                                        |                           |                                             |  |  |

|-----------------------------------|----------------------------------------|---------------------------|---------------------------------------------|--|--|

| Accel, Ltd                        | Fujitsu Limited                        | Luxtera Inc.              | Pico Computing                              |  |  |

| ADATA Technology Co., LTD         | Galaxy Computer System Co., Ltd.       | Marvell                   | Renesas Electronics Corporation             |  |  |

| AIRBUS                            | GDA Technologies                       | Mattozetta Technologies   | Science & Technology Innovations            |  |  |

| Altior                            | GLOBALFOUNDRIES                        | Maxeler Technologies Ltd. | SEAKR Engineering                           |  |  |

| APIC Corporation                  | GraphStream Incorporated               | MediaTek                  | ST Microelectronics                         |  |  |

| Arira Design                      | HGST, a Western Digital Company        | Memoir Systems Inc.       | Suitcase TV Ltd                             |  |  |

| Arnold&Richter Cine Technik       | HiSilicon Technologies Co., Ltd        | Mentor Graphics           | Tabula                                      |  |  |

| Atria Logic, Inc.                 | HOY Technologies                       | Miranda                   | Tech-Trek                                   |  |  |

| BroadPak                          | Huawei Technologies                    | Mobiveil, Inc.            | Teradyne, Inc                               |  |  |

| Cadence Design Systems, Inc.      | Infinera Corporation                   | Montage Technology, Inc.  | The Regents of the University of California |  |  |

| Convey Computer Corporation       | Information Sciences Institute USC     | Napatech A/S              | Tilera Corporation                          |  |  |

| Cray Inc.                         | Inphi                                  | National Instruments      | Tongji University                           |  |  |

| DAVE Srl                          | ISI/Nallatech                          | NEC corpration            | T-Platforms                                 |  |  |

| Design Magnitude Inc.             | Israel Institute of Technology         | Netronome                 | TU Kaiserslautern                           |  |  |

| Dream Chip Technologies GmbH      | Juniper Networks                       | New Global Technology     | UC, Irvine                                  |  |  |

| Engineering Physics Center of MSU | Kool Chip                              | Northwest Logic           | UMC                                         |  |  |

| eSilicon Corporation              | Korea Advanced Institute of Science    | Obsidian Research         | University of Heidelberg ZITI               |  |  |

| Exablade Corporation              | Lawrence Livermore National Laboratory | OmniPhy                   | University of Rochester                     |  |  |

| Ezchip Semiconductor              | LeCroy Corporation                     | Oregon Synthesis          | Winbond Electronics Corporation             |  |  |

| FormFactor Inc.                   | LogicLink Design, Inc.                 | Perfcraft                 | Woodward McCoach, Inc.                      |  |  |

|                                   |                                        |                           | ZTE Corporation                             |  |  |

|                                   |                                        |                           |                                             |  |  |

100 Adaptars to data

Micron

18 April, 2013

©2013 Micron Technology, Inc. | 15

#### Ecosystem

#### The Future

- Memory ecosystem changing

- High performance signaling and routing opening doors for EDA growth

- ► HMC is coming THIS YEAR

- Tool and IP support needed now