# **EXILINX**ALL PROGRAMMABLE

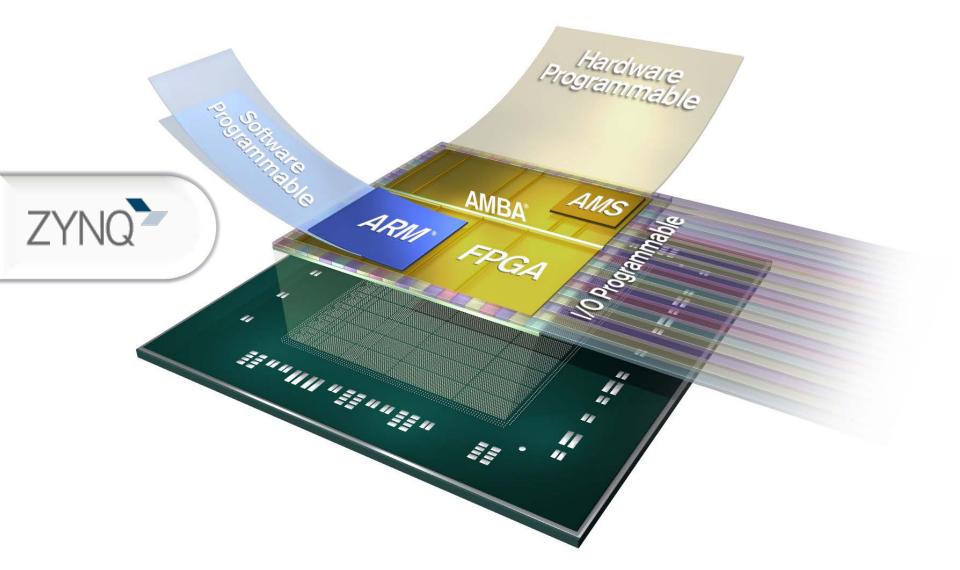

## FPGA Entering the Era of the All Programmable SoC

Ivo Bolsens, Senior Vice President & CTO

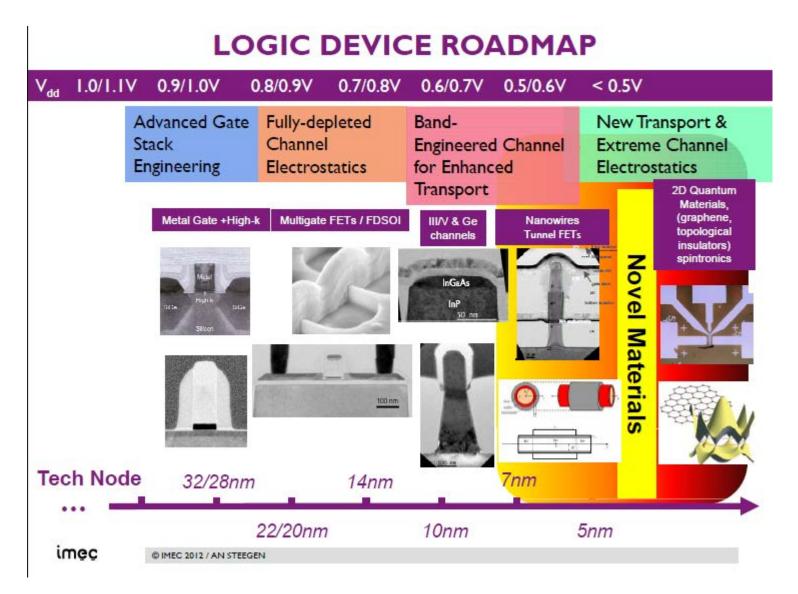

#### Moore's Law: The Technology Pipeline

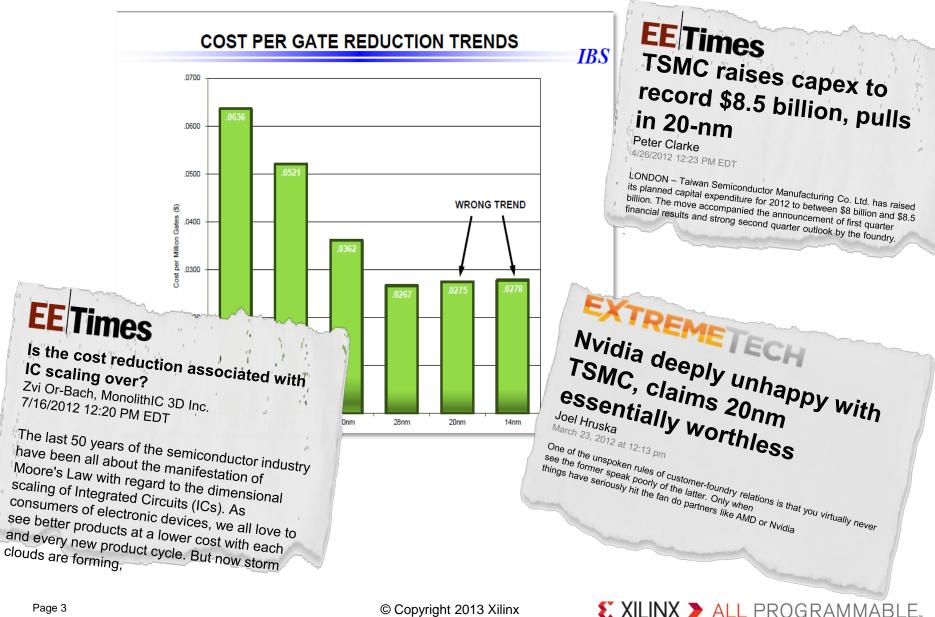

#### **Industry Debates on Cost**

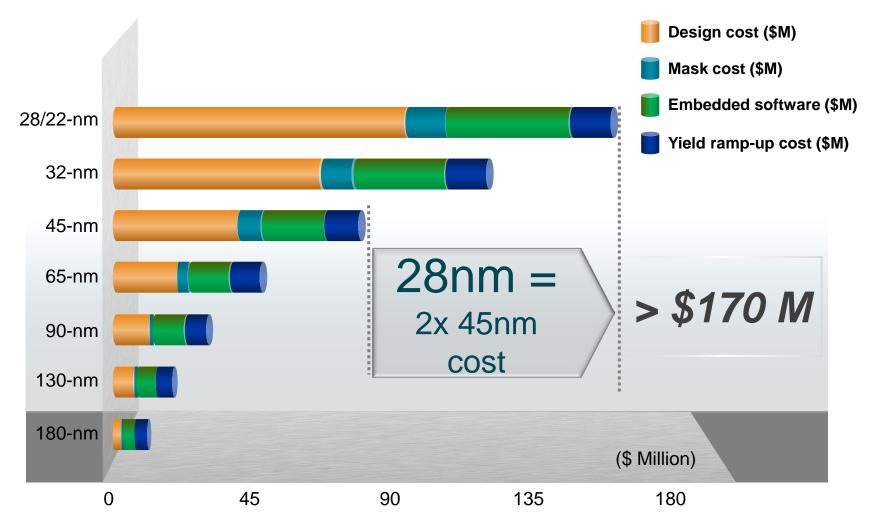

## **Design Cost**

Estimated Chip Design Cost, by Process Node, Worldwide, 2011

#### XILINX > ALL PROGRAMMABLE.

#### Internet

## What Happens in an Internet Minute?

#### XILINX > ALL PROGRAMMABLE.

#### "Don't believe everything you read on the Internet."

Abraham Lincoln, U.S. President

Photo Source: Wikipedia

## **More Intelligence in Every System**

## **SMART Data Center Revolution**

New Opportunities to Control Costs and Increase Strategic Advantage...

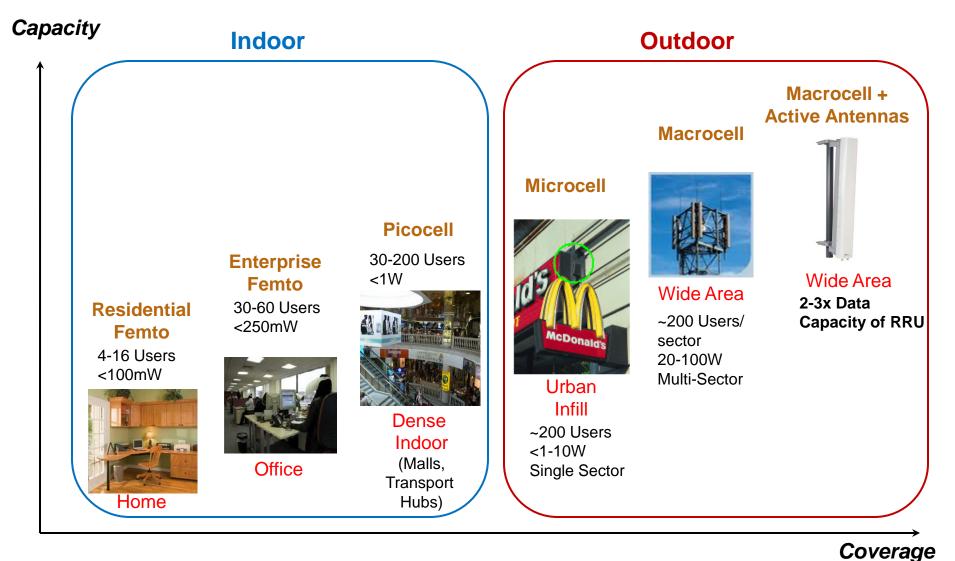

## Smart wireless networks to the rescue

Carriers are turning toward more intelligent network management...

## **Smart Factories**

For factory management in the future, it will become essential to strive to implement smart capabilities...

#### **MACHINES THAT UNDERSTAND**

## The Next Big, Digital Economy; 'Smart Energy'

The energy market is undergoing a major transformation...

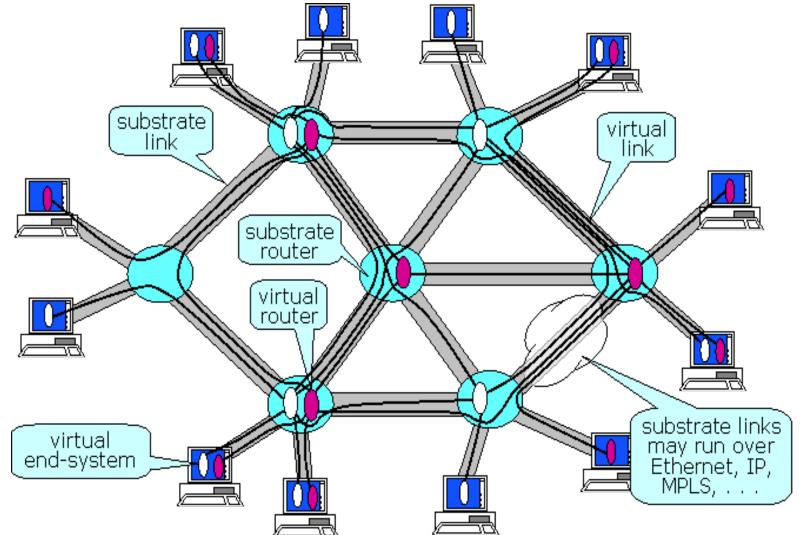

## From Dumb Pipes to Smart Networks

## **Trend Wired Infrastructure: Software Defined Networks**

Slide credit: From "Virtualizing the Net" by Jon Turner (2004)

© Copyright 2013 Xilinx

#### XILINX ➤ ALL PROGRAMMABLE.

## **Trend Wireless Infrastructure: Scalable Platforms**

#### **EXILINX >** ALL PROGRAMMABLE.

## Trend Data Center Infrastructure: Cloud Computing

## **Big Data**

Increasing Volume, Velocity, and Variety

## Low power

Reduce operation and cooling costs

Both outside and inside

XILINX > ALL PROGRAMMABLE.

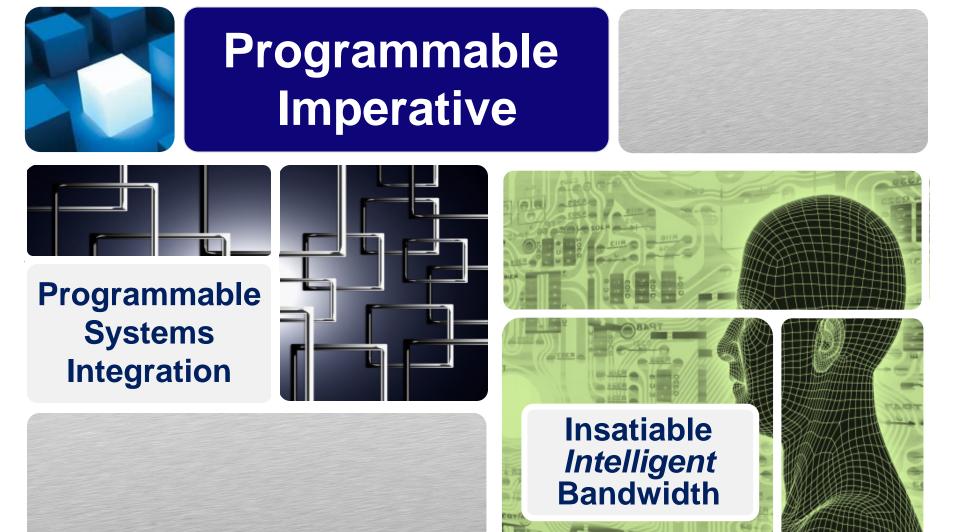

#### **Industry Mandates**

## The Era of All Programmable SoC

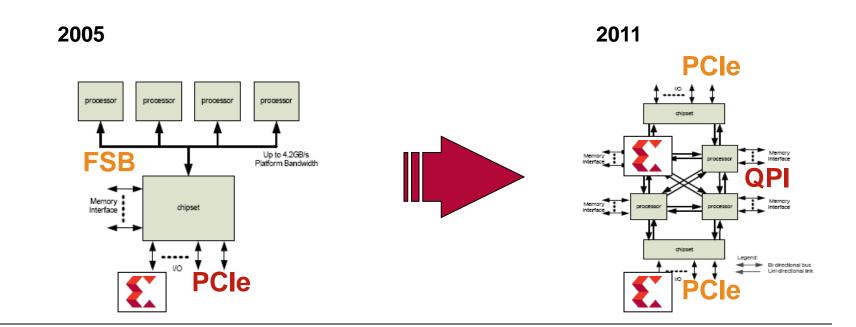

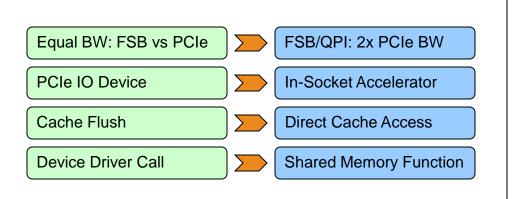

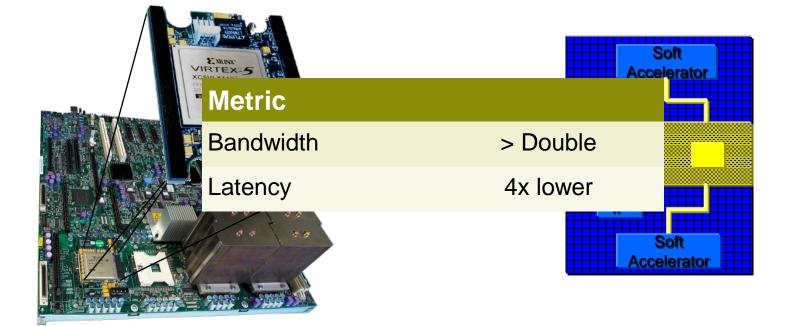

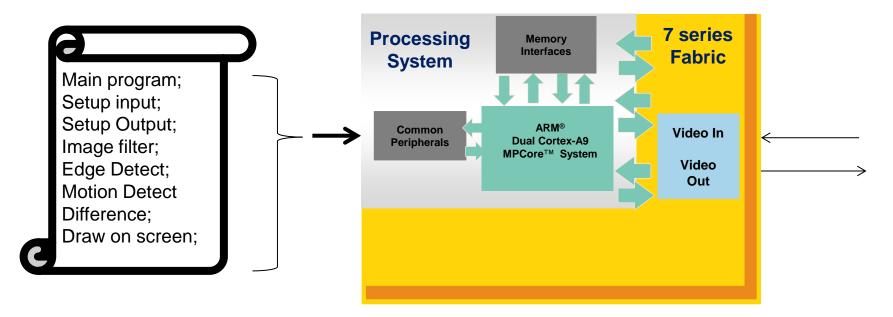

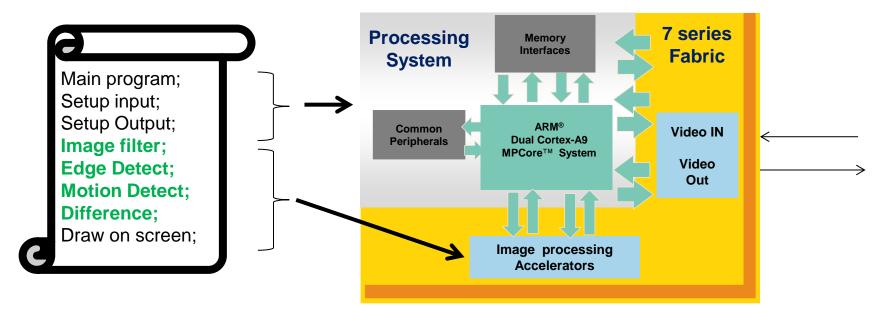

## **CPU + FPGA** Evolution

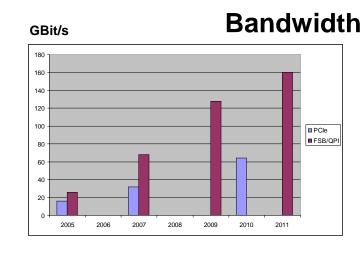

## Extended Processing: Embedded ARM

#### > Processor System boots first

- Separate power for PL\*

- Peripherals alive before PL configuration

#### > Processor controls PL configuration

- Multiple security levels supported

- Boot in secure or non-secure mode

- Download PL image via network, SD, USB

#### > Multiple AXI interfaces to PL

- Processor System can access IP in PL

- PL IP has access to Processor System peripherals and memory system at full BW

\*PL = Programmable Logic

#### **Programmable Platform Opportunity**

#### Major Leap in Cost and Performance

© Copyright 2013 Xilinx

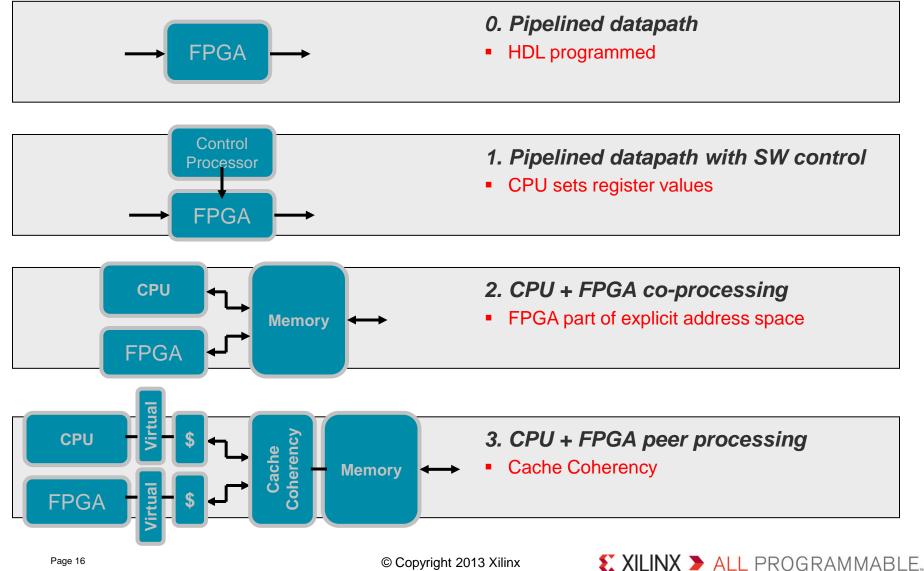

#### **FPGA/CPU Use Models**

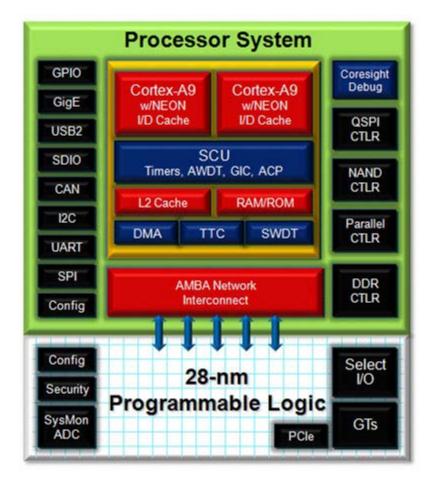

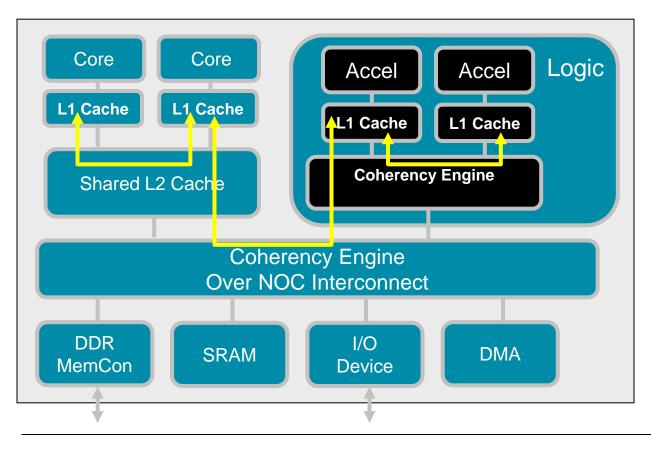

## Programmable Platform: CPU + FPGA Peer Processing

#### Capabilities

- > Coherent Caches for HW

- Coherent Caches for SW

- > Coherency Management

#### **Coherency Benefits:**

- Peer Processing: Direct Cache-2-Cache data movement

- Latency: Very low latency access to CPU (FPGA) data

- Usability: No SW cache flush needed

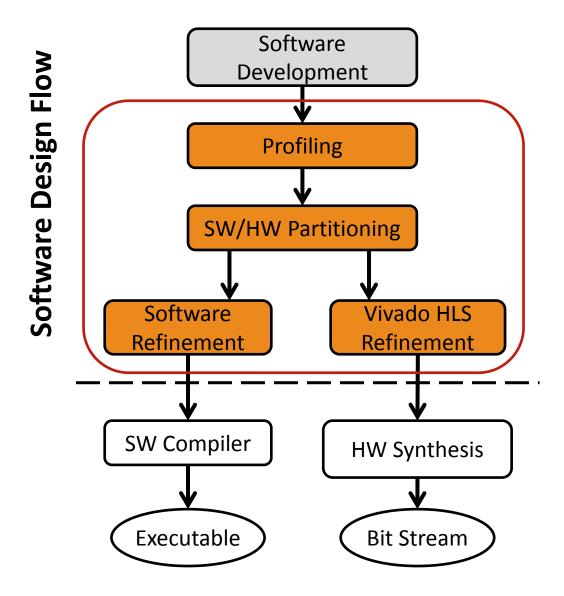

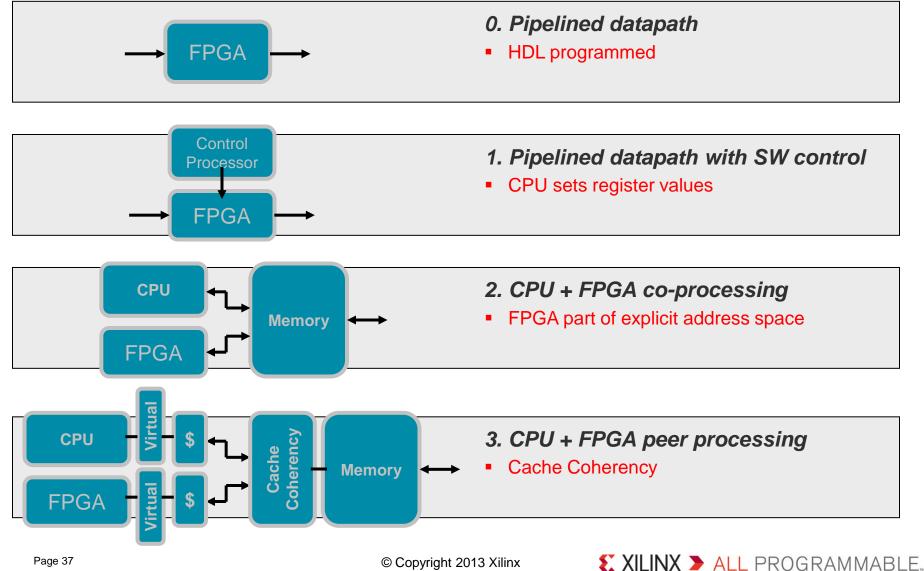

## **Design Flow Overview**

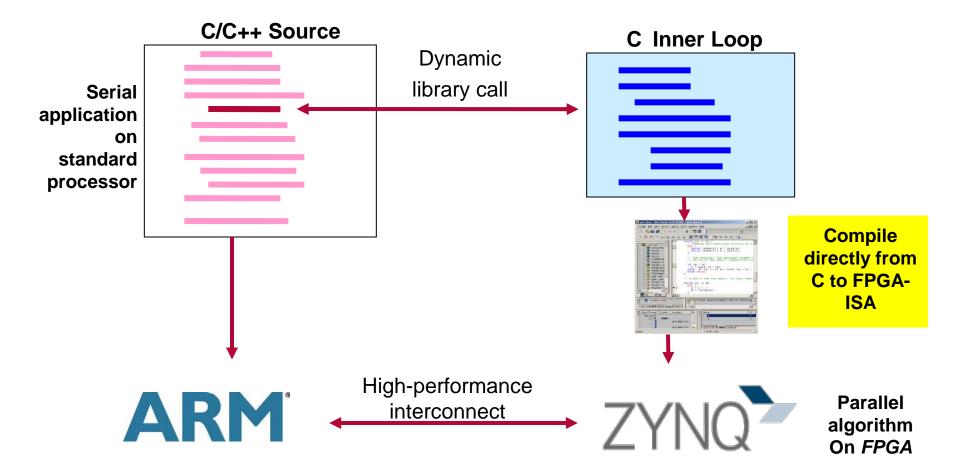

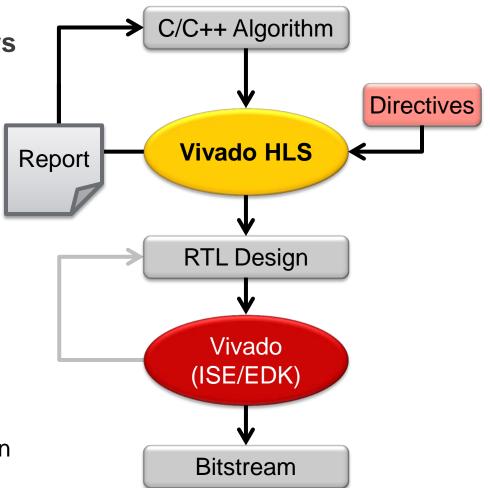

## **Programming Accelerators from C/C++**

## **Programming Accelerators from C/C++**

- Enables software programmers to target Xilinx FPGAs

- Software-programmability

- Portability: 7 series, Zynq

- Delivers productivity increase for RTL designers

- C/C++ level verification and testbench reuse

- Earlier area/latency reports

- Software-driven design exploration

#### More Turns Per Day (Verification and Architecture Exploration)

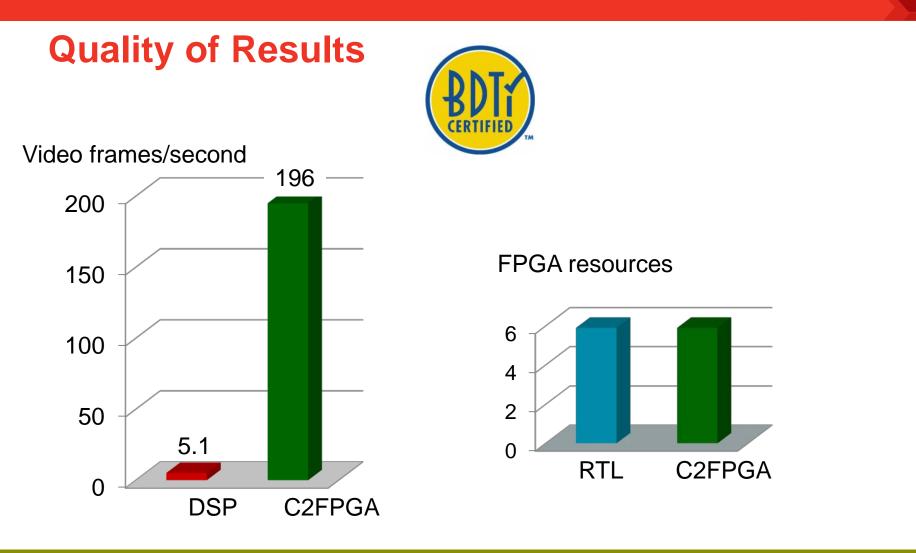

FPGA:>38 times better performance than DSP video processorQOR:C2FPGA equal to or better than RTL synthesisEase-of-use:C2FPGA 2x fewer lines of C code than DSP processor

© Copyright 2013 Xilinx

XILINX > ALL PROGRAMMABLE.

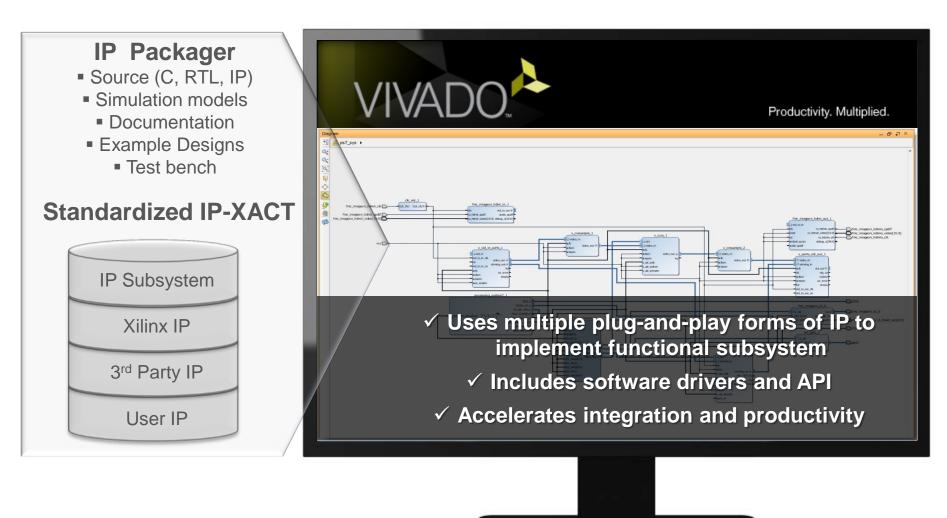

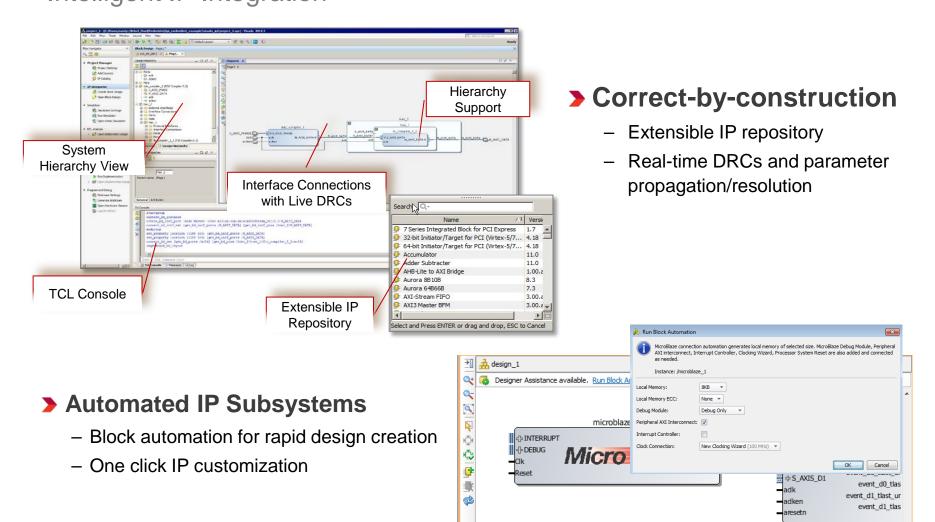

## **Vivado IP Integrator**

Enabling Reuse and Delivering Fully Functional IP Subsystems

## **Vivado IP Integrator**

Intelligent IP Integration

#### > Co-Optimized for platforms

- Target platform aware

- Supports All Programmable Zynq and 7 series kits

| Select D   |                                                      |                            |           |                    |               |               |             |                                 |                           |                           |                                                           |                         |

|------------|------------------------------------------------------|----------------------------|-----------|--------------------|---------------|---------------|-------------|---------------------------------|---------------------------|---------------------------|-----------------------------------------------------------|-------------------------|

| Parts      | Filter                                               | Pamily 7                   | a         |                    |               |               |             | Board Preview                   |                           |                           |                                                           |                         |

| Boards     |                                                      | Package A<br>Speed grade A | a         |                    | •             |               |             |                                 | 1.98 EDRS Manay<br>(SODME | PND Connation<br>(HPGLPG) | Toritopicios (Pressel)<br>Intelligae                      |                         |

|            |                                                      | obeen Grane Ly             | Reset All | Filters            |               |               |             |                                 | 11                        | 11                        |                                                           |                         |

| arch: 🔍    |                                                      |                            |           |                    |               |               |             |                                 | _                         |                           |                                                           |                         |

| arch: JQ.  |                                                      |                            | I/O Pin   | Available          | T wr          | L             | Block       | 1 10 10 10                      | _                         | 444                       |                                                           |                         |

|            | Board                                                | Part                       | Count     | 106s               | Elements      | FlipFlops     | RAMs        | Offerential One<br>Official One |                           |                           |                                                           | Linesc BP1<br>Internety |

| Virtex-7 V | C705 Evaluation Platform<br>C707 Evaluation Platform | @ xc7vx485tfg1761-2        | 900       | 500<br>700         | 203800 303600 | 407600 607200 | 445<br>1030 | 3000 Heater                     |                           | FPGA                      |                                                           | Guid-Dh<br>Manory       |

| ZYNQ-7 Z   | C702 Evaluation Board                                | xc7z020clg484-1            | 484       | 200                | 53200         | 106400        | 140         | Uan Selutar<br>Bullion, and LE  |                           |                           |                                                           | O Bpen<br>Smalle        |

|            |                                                      |                            |           |                    |               |               |             | HCMI Videv<br>Identica          |                           |                           | 2 cm a 1                                                  | Orgitey<br>consident    |

|            |                                                      |                            |           |                    |               |               |             | 1                               |                           | mm                        | μ                                                         |                         |

|            |                                                      |                            |           |                    |               |               |             |                                 |                           |                           | _                                                         |                         |

|            |                                                      |                            |           |                    |               |               |             | 110 EPPTON (A                   | Cort Series Series        | 1081-0179-044             | /St/Johnson                                               | tripe tage              |

|            |                                                      |                            |           |                    |               |               |             | PC But Sets 1                   | Corty well Tautr. Ad      | 108-c-case in eds         | ravé (GB Ormachr                                          | Terbe Calle             |

| 2          |                                                      |                            |           |                    |               |               |             | 808                             |                           |                           |                                                           |                         |

|            |                                                      |                            |           |                    |               |               |             |                                 |                           |                           |                                                           |                         |

|            |                                                      |                            |           |                    |               |               | <u>&gt;</u> | [ • ]                           |                           |                           | OK.                                                       |                         |

|            |                                                      |                            |           |                    |               |               | 1           |                                 |                           |                           | OK:                                                       | Cano                    |

| 30         |                                                      |                            |           |                    |               |               |             |                                 |                           |                           | OK:                                                       | Cano                    |

|            |                                                      | 1                          |           | _                  |               |               | 1           |                                 |                           |                           | OK:                                                       | Cano                    |

| 30         |                                                      | 1                          | _         | _                  |               |               |             |                                 |                           |                           | OK:                                                       | Cano                    |

|            | 1                                                    | 1                          |           |                    |               |               |             | -                               |                           |                           | OK:                                                       | Cano                    |

|            |                                                      | 1                          |           | c DPI Flash        | н             |               | LP          | -                               | Sile (Elw11)              | De Powe                   | r Barbah                                                  | Cano                    |

| 30         |                                                      |                            |           | BPI Flass<br>(US9) | h (J          | 2             | স           | -                               |                           | ID6                       | r Barbah                                                  | Cano                    |

| 20         |                                                      |                            |           | (US0)              | h (           | 2             | LP          | -                               |                           | De Powe                   | r Barbah                                                  | Cano                    |

| 20         |                                                      |                            |           | BPI Flash<br>(US9) | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Barbah                                                  | Cano                    |

| 20         | USD-UMPY                                             | -                          |           | (US0)              | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Gelich<br>19                                            | Cano                    |

| 30         | (IRL)<br>- CATL-REU                                  |                            |           | (US0)              | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Beilich                                                 | Cano                    |

| 20         | (101.)                                               | -                          |           | (US0)              | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Beilich<br>9)<br>- Power (149)<br>- Prog                | Cano                    |

| 20         | (JU)<br>USB-JTAG -<br>(US9)                          |                            |           | (US0)              | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Beilich<br>9)<br>- Power (149)<br>- Prog                | Cano                    |

| 20         | USB-JTAG -<br>CUS9)                                  |                            |           | (US0)              | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Battob<br>19<br>- Power (J49)<br>- Prog<br>- OPU Reset  | Cano                    |

|            | (JU)<br>USB-JTAG -<br>(US9)                          |                            |           | (US0)              | h (J          | 2             | LP          | -                               |                           | De Powe                   | r Bailton<br>6)<br>– Power (J49)<br>– Prog<br>– CPU Resat | Cano                    |

| 30         | (JU)<br>USB-JTAG -<br>(US9)                          |                            |           |                    |               | 2             | LP          | -                               |                           | De Powe                   | r Battob<br>19<br>- Power (J49)<br>- Prog<br>- OPU Reset  | Cano                    |

|            | (JU)<br>USB-JTAG -<br>(US9)                          |                            |           | (US0)              |               | 2             | -Eo E       | -                               |                           | De Powe                   | r Battob<br>19<br>- Power (J49)<br>- Prog<br>- OPU Reset  | Cano                    |

#### Co-Optimized for silicon

- IP aware automated AXI Interconnects for maximum performance or area

- Automated interface, device driver & address map generation for Zynq and MicroBlaze

#### Vivado IP Integrator Intelligent IP Integration

#### **EXILINX >** ALL PROGRAMMABLE.

F K

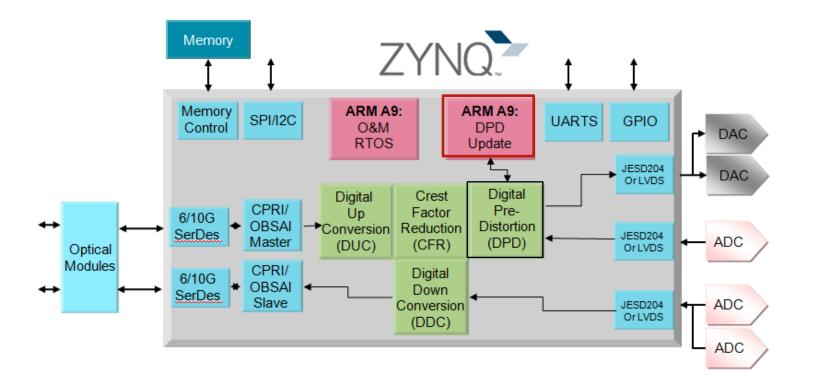

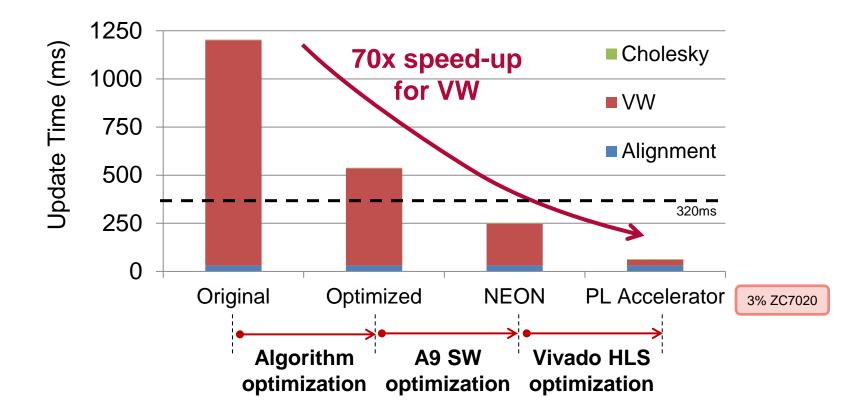

## **Zynq in Wireless Digital Front End**

- > Cost and power reduction by integrated solution

- Performance increase by exploiting the massive compute power of multi-core processors and programmable logic

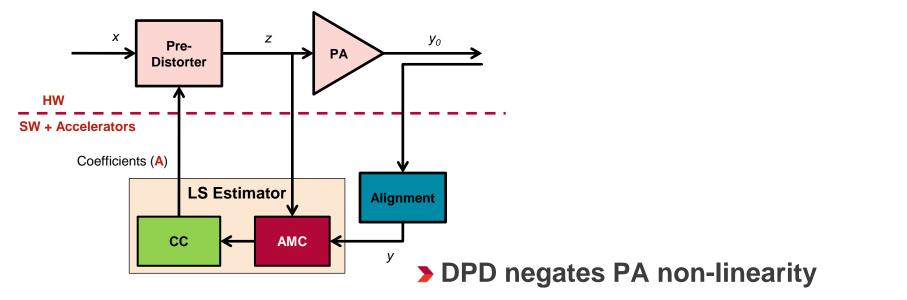

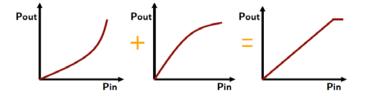

## **Programmable Digital Pre-Distortion**

- PAs consume massive static power

- DPD improves PA efficiency by ~35-40%

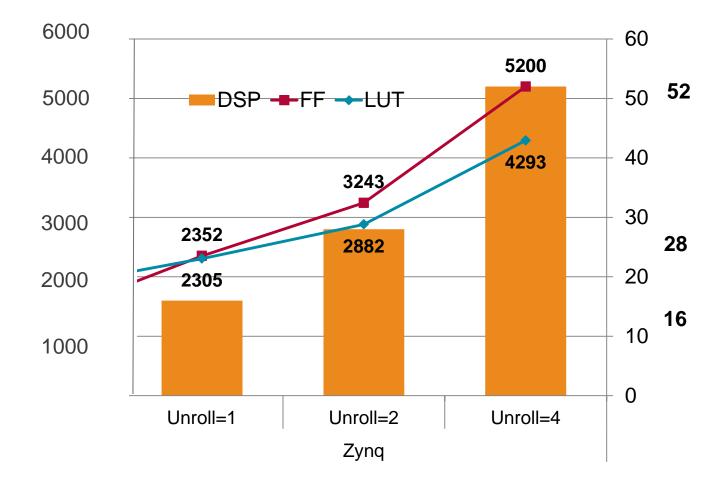

#### **HW Acceleration**

#### **HW Accelerator Resources**

**EXILINX >** ALL PROGRAMMABLE.

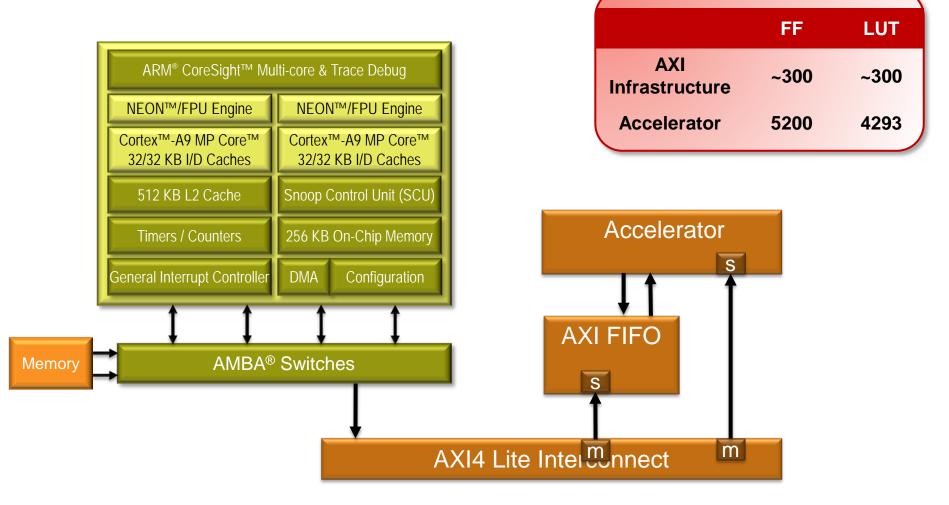

#### **DPD Architecture Data Movement**

#### **Reduced Resources Because of AXILite Infrastructure**

© Copyright 2013 Xilinx

XILINX > ALL PROGRAMMABLE.

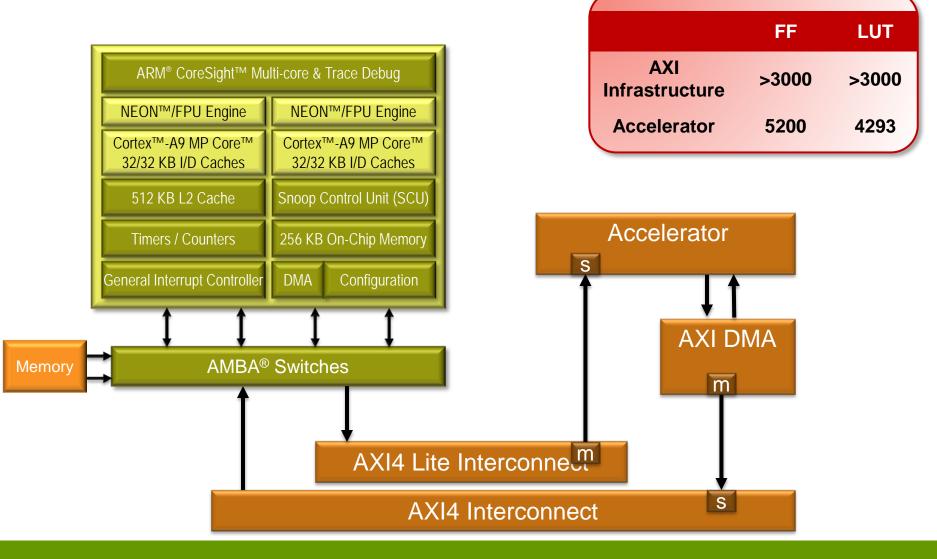

#### **DPD Architecture Data Movement**

#### **High Throughput Because of DMA Infrastructure**

XILINX > ALL PROGRAMMABLE.

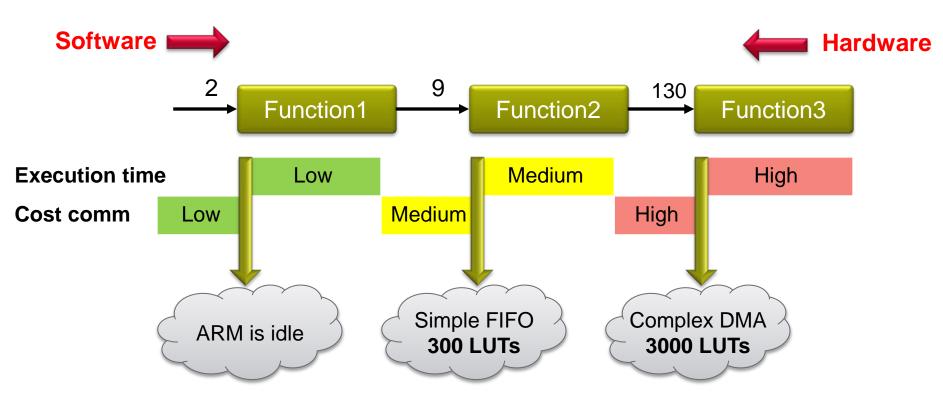

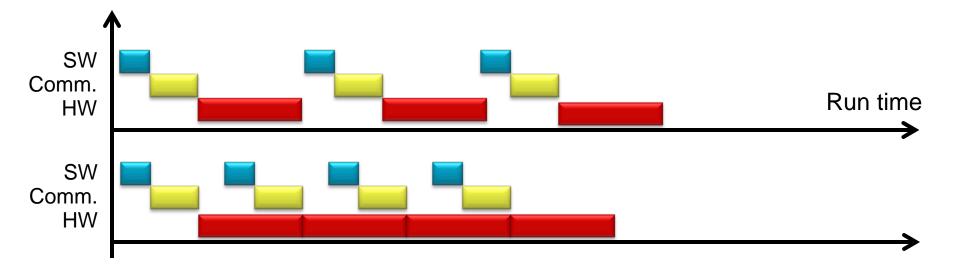

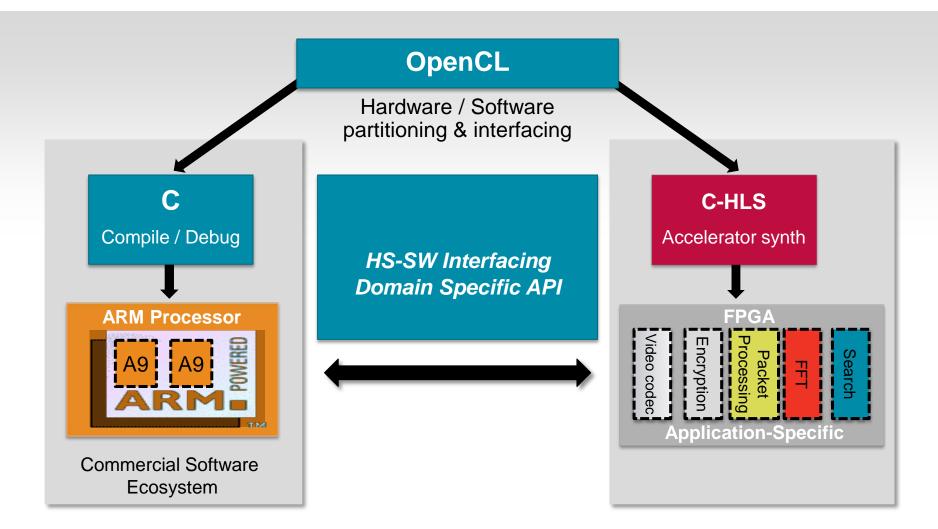

#### Hardware/Software Boundary

- > Optimal cut point depends on execution times and cost of communication

- Implement different cut points is a time consuming task

#### **Goal: Maximize Throughput and Reduce Area Resources**

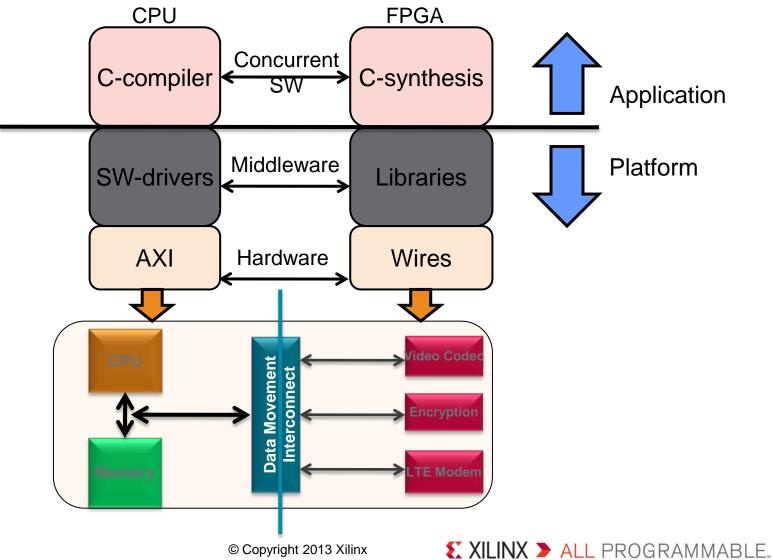

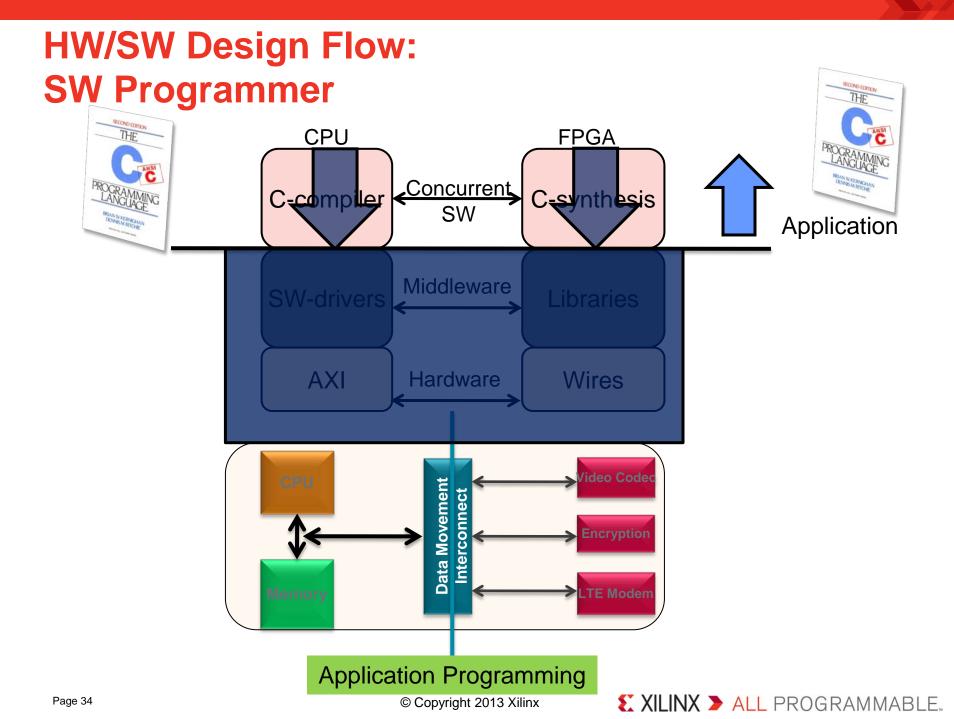

## **Software Integration**

> Accelerator implementation

- Data motion network

- > Optimal drivers

#### **Smart Software Driver is Necessary**

## **HW/SW Design Flow**

#### **Video Acceleration**

#### C/C++ Software Program

#### 1 frame per 13 seconds

#### **Processor + Fabric Solution on Zynq-7000 AP SoC**

#### C/C++ Software Program

Software video processing functions compiled onto FPGA fabric 60 frames per second, 700x speedup

#### **FPGA/CPU Use Models**

© Copyright 2013 Xilinx

#### **Towards Heterogeneous Multi-core**

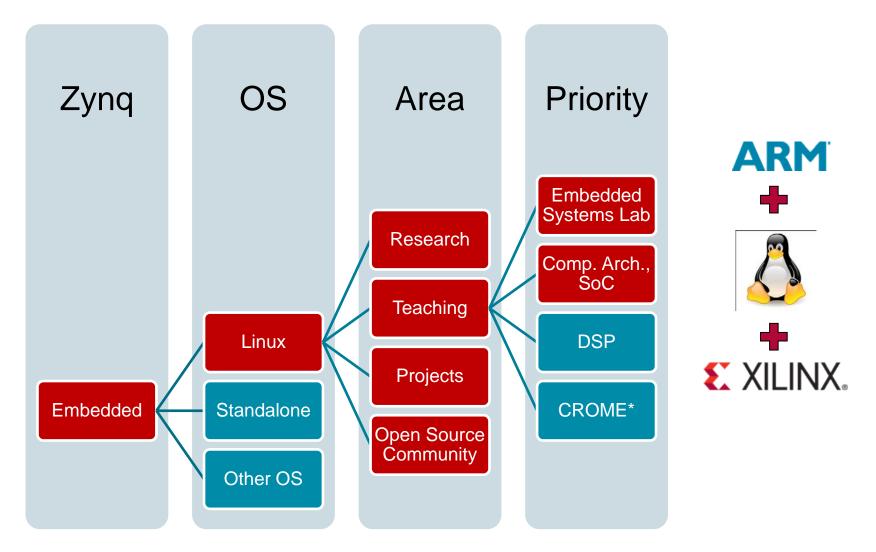

#### **Opportunities for SoC Education**

\*Controls, RObotics and MEchatronics

XILINX > ALL PROGRAMMABLE.

#### **ZED Board**

#### >ZED Board

- -Zynq Evaluation and Development Kit

- Low cost Zynq based community board (XC7Z020)

- Partnership between Avnet, Digilent, Xilinx

- Digilent will fulfill academic market for Xilinx University Program

#### ZEDboard.org

- > Open source SW and IP

- Linux

- Eclipse based IDE

- Vivado HLS: C to FPGA

- Reference designs

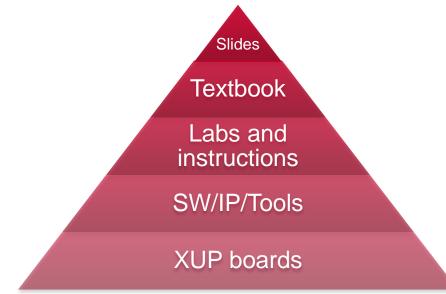

## **Target Teaching Platform (TTP)**

#### > Turn key solution for teaching labs on

- Digital Logic

- Digital Signal Processing

- Embedded System Design

- Principle of Microcomputers

- Embedded Operating Systems

- > Xilinx updates the kit as and when required

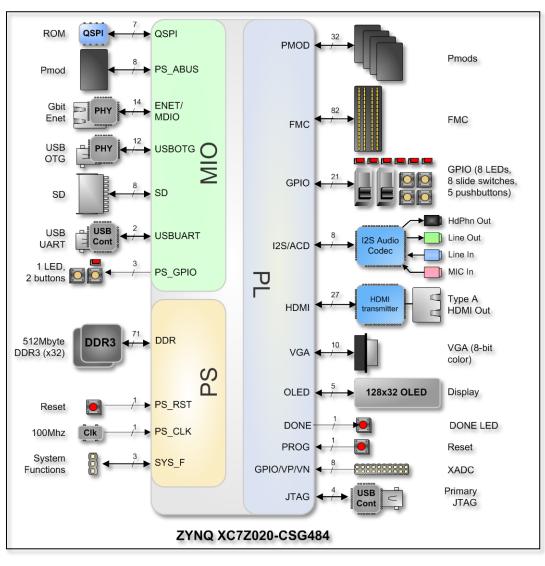

## **ZED Block Diagram & Features**

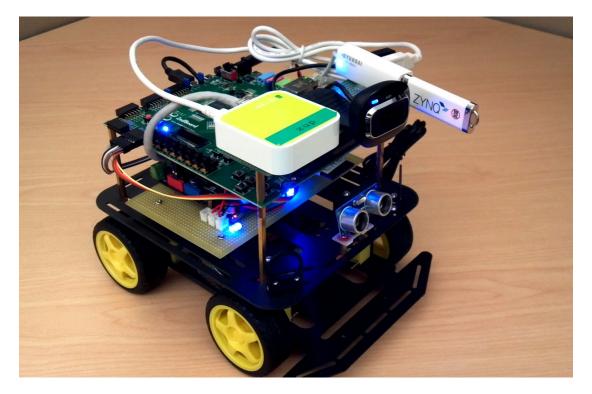

## **Targeted Teaching Platform (TTP)**

Initial version of the Smart Car TTP:

ZynqBot- Mark1

Controlled wirelessly by Android cell phone app

- >Modern FPGA is an All Programmable SoC

- **>** Software Centric Design Flow

- > Unmatched Performance/Watt

- **>** Towards Heterogeneous Multi-Core

- Targeted Teaching Platform