# The Short, Medium and Long-Term Path to the 3D Ecosystem Panel Discussion at EDPS

### A Monolithic 3D-IC Perspective

Deepak C. Sekar Rambus Inc.

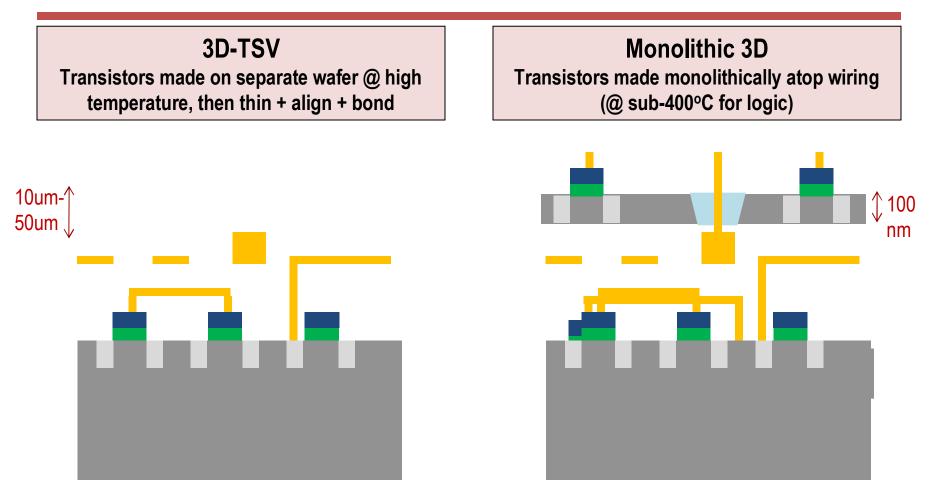

## **Two Types of 3D Technology**

TSV pitch > 1*um*\*

TSV pitch ~ 50-100*nm*

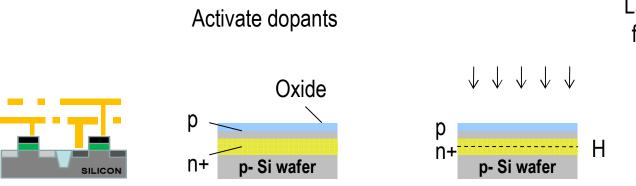

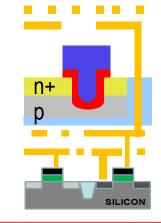

## A Process Flow for Monolithic 3D: Recessed Channel Transistors with Activation before Layer Transfer

Layer transfer un-patterned film. No alignment issues.

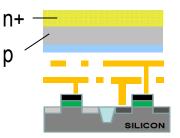

Well-aligned sub-400C RCATs Si thickness < 100nm Min. feature size TSVs since low Si thickness, no misalignment issues

n+ p siLiCON

• Steps atop Cu/low k < 400°C

• RCATs used in production

DRAM since the 90nm node

→ Adoption easier

[D. C. Sekar, Z.Or-Bach, "Monolithic 3D-ICs with Single Crystal Silicon Layers", Proc. IEEE 3DIC Conference 2011 (Invited)]

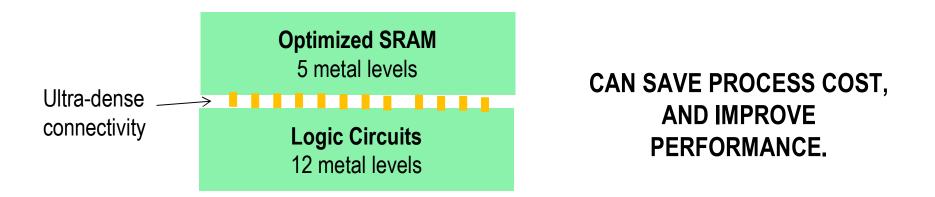

## **SRAM-Logic Stacking**

• SRAM requirements different from logic today.

Different number of metal levels, V<sub>t</sub>, L<sub>eff</sub>...

Ultra-dense vertical connectivity needed, esp. for small size SRAMs within a logic core → good fit for Monolithic 3D

#### EDA need: Tools to partition designs and stack the SRAM

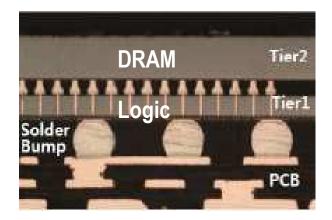

## Logic-Logic Stacking with High TSV Density

### Today "Pseudo-3D" EDA Tools

- Modify existing 2D tools slightly

- TSVs in whitespace or modify existing layout slightly for TSVs to stacked layer

- OK for today's 5um TSVs (low density)

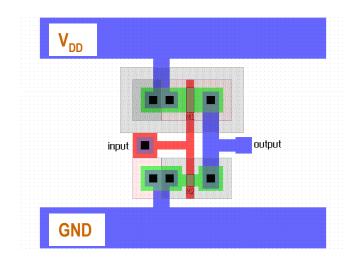

### Needed for Monolithic 3D "Native-3D" EDA Tools

•3D routing, placement, floorplanning tools that work <u>for TSVs close to min.</u> <u>feature size</u>

•Support for both block-level and gate-level partitioning

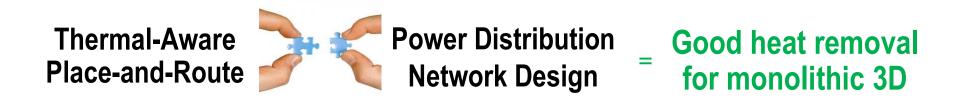

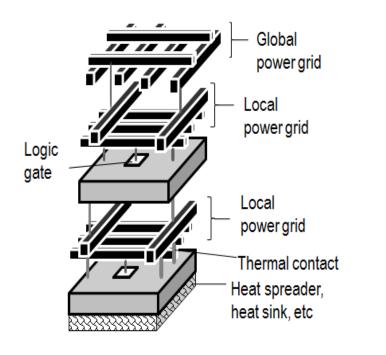

Most logic gates have V<sub>DD</sub> and GND contacts

Low (thermal) resistance power grids  $\rightarrow$  low temp. drop between heat sink and stacked logic gate

• Promising simulation results

EDA need: Integrate power distribution design with (thermal-aware) place-and-route for monolithic 3D

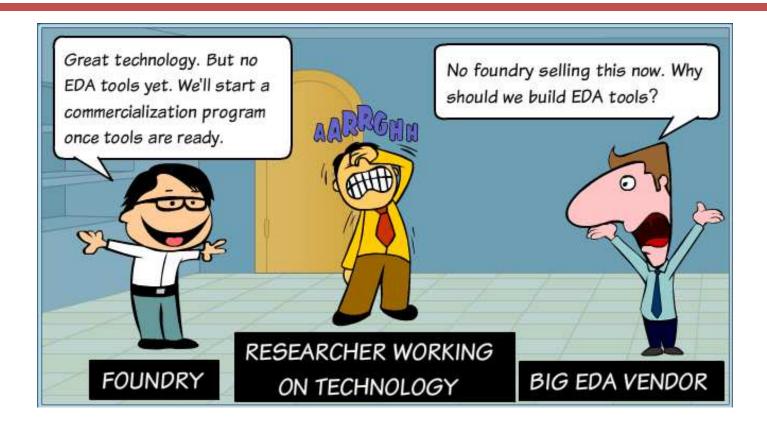

## How will monolithic 3D technology tackle this familiar problem?

Suggestion to the EDA community:

EDA tools for logic-logic stacking starting to be developed for um-scale TSVs.

Make sure your algorithms are scalable to nm-scale TSVs... they may happen sooner than you think!