### **Trends in Programmable Solutions**

SoC FPGAs for Embedded Applications and HW/SW Co-Design

**Mike Hutton** Principal Investigator Office of the CTO Misha Burich Sr. VP and Altera CTO

\*\*\*\*\*\*\*\*\*\*

#### EDPS Apr 5, 2012

### Agenda

- Market Drivers and New Enabling Technologies

- Embedded Computing with FPGAs

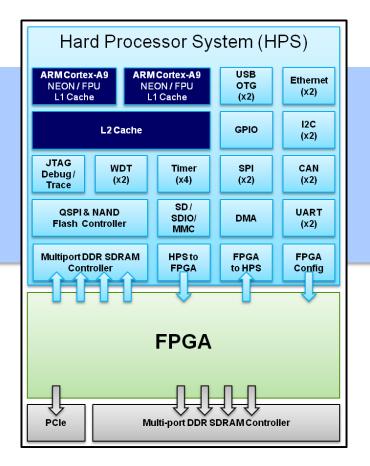

- The Emergence of SoC FPGAs

- Programmable Silicon Substrate

- Software-Programmable Hardware

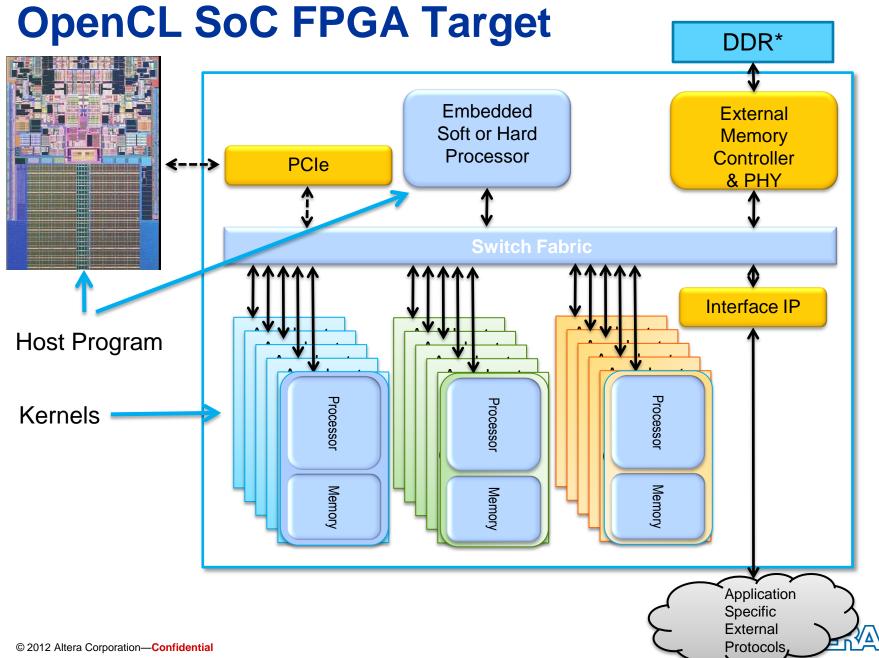

- OpenCL for Parallel Programming

- System Integration

#### Summary

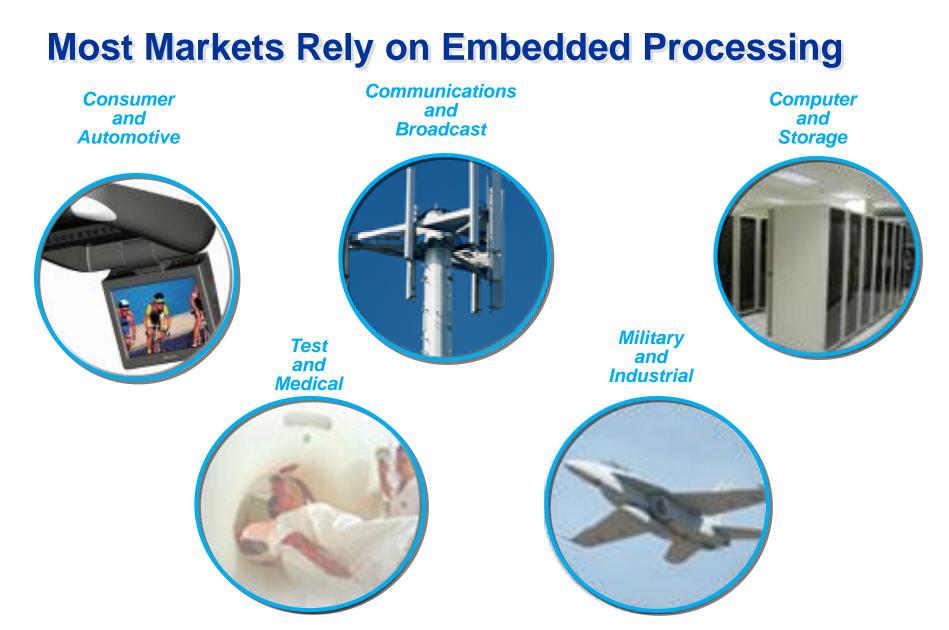

### Market Drivers and Enabling Embedded Technologies

© 2012 Altera Corporation—Confidential

### Enabling Technologies: 200X-201X

Moore's law enables high density programmable platforms

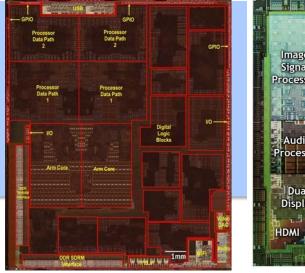

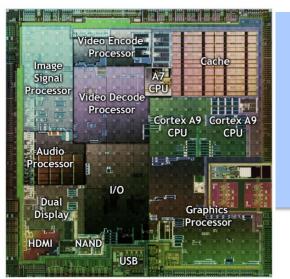

### **The Age of Systems-On-Chip**

ARM based SoCs by Apple, Nvidia, Qualcomm, TI, others

SoC FPGAs by Altera, Xilinx, others

### **More-Than-Moore**

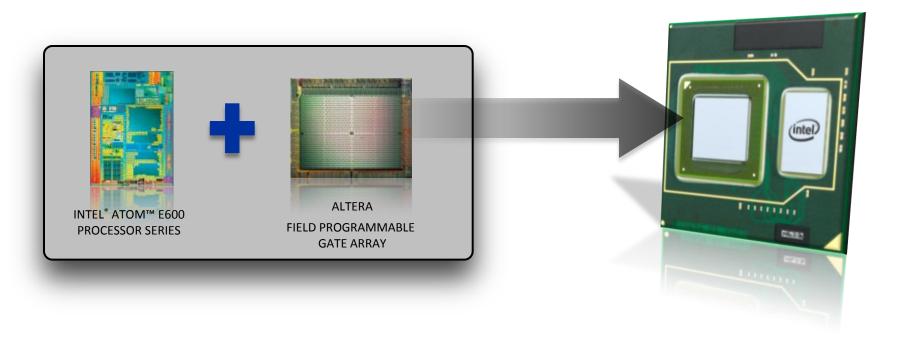

- System-in-package multi-die integration

- POP, 2.5D, 3D, micro-bumps, through-silicon-vias (TSV)

- Example: Intel's integration of Atom processor with Altera's FPGA

- E600C

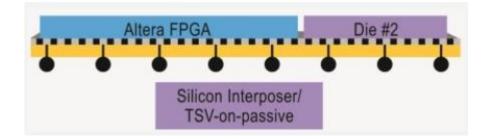

### **First Heterogeneous 3D IC**

(Announced 3/22/2012)

#### TSMC CoWoS (Chip-on-Wafer bonding)

© 2012 Altera Corporation—Confidential

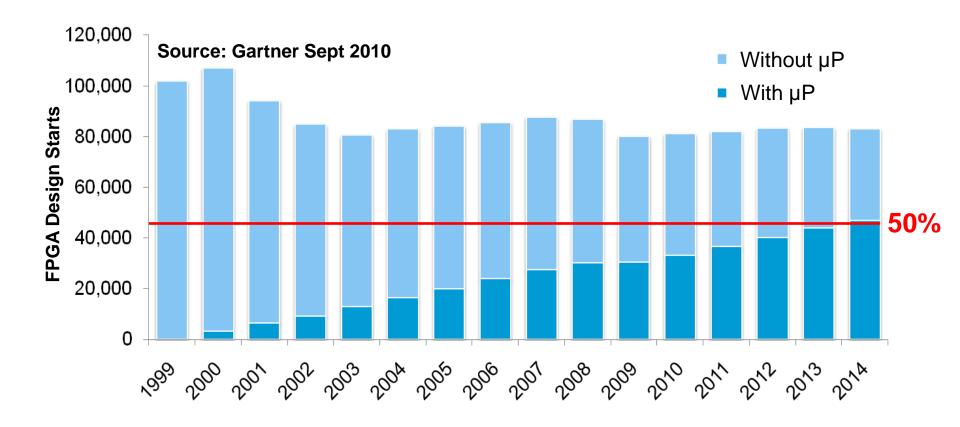

### **Embedded Computing on FPGAs**

Soon, a majority of FPGA designs will feature an embedded processor

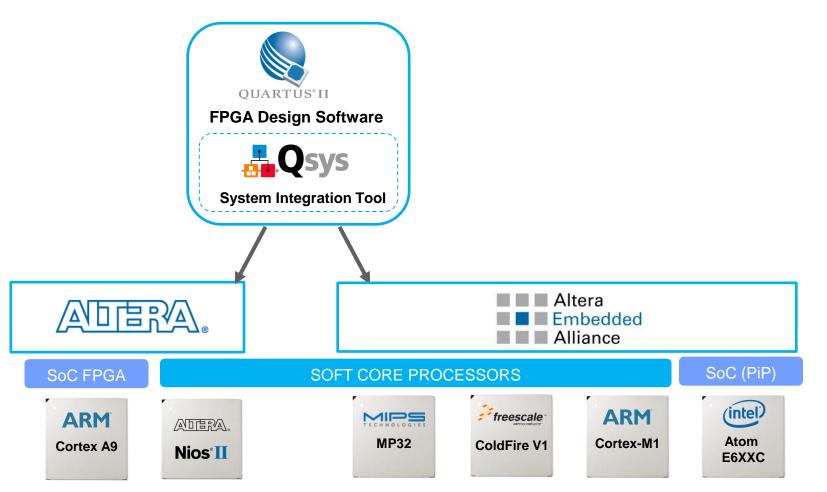

### **Altera's Embedded Initiative**

#### Single FPGA Design Flow for a Broad Array of Industry-Leading Embedded Processors

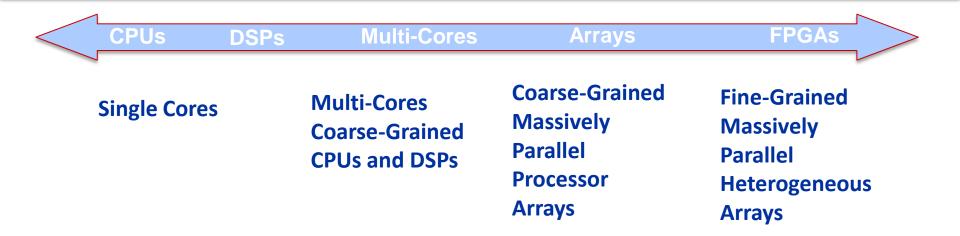

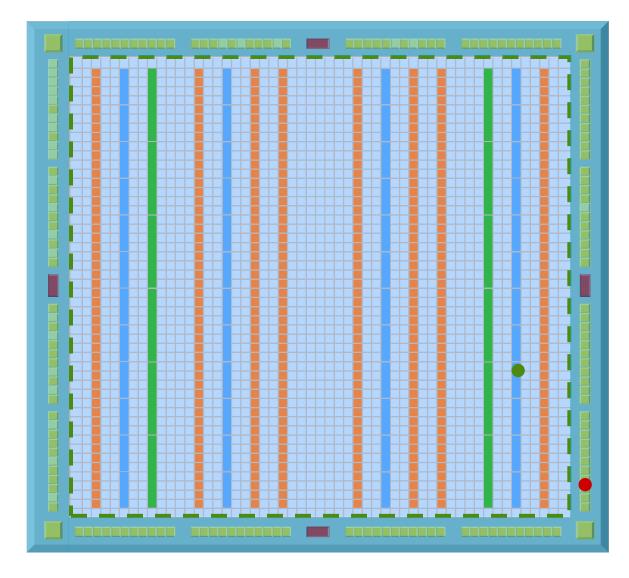

### **Modern FPGA: Massively Parallel**

- Million + Logic Elements

- Multi-billion

Transistors

- Thousands of 20-Kbit Memory Blocks

- Thousands of MAC DSP Blocks

- Many External Memory, LVDS, And Transceivers IO Blocks

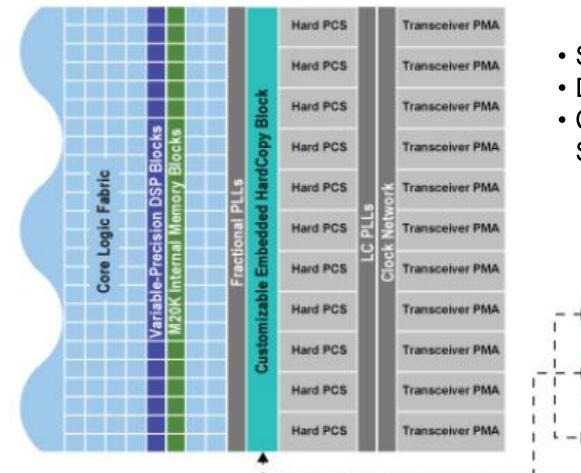

### Hardened System Protocols and IP

- Standard IP Blocks

- Differentiated IP Blocks

- Complete Programmable

System

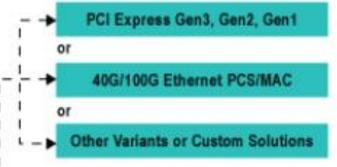

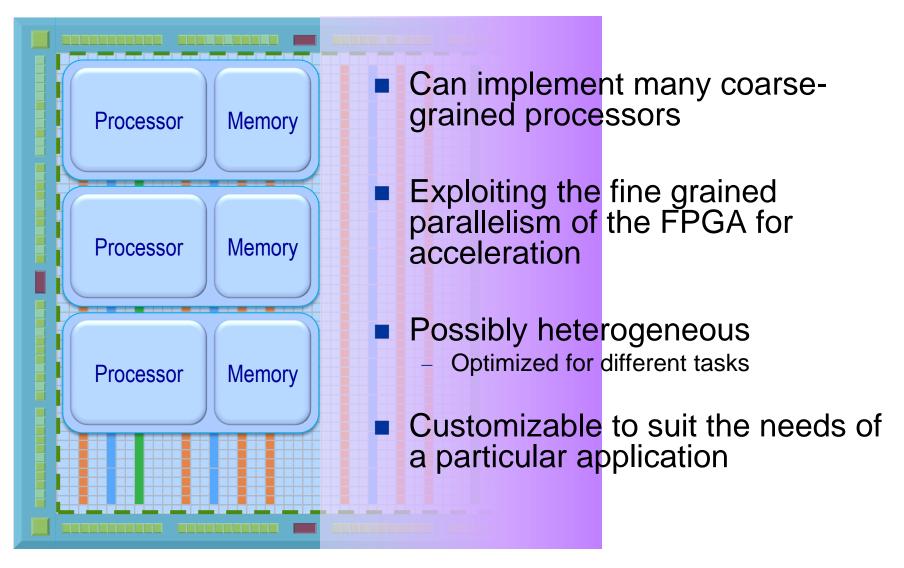

### **FPGA : Fully Configurable Multicore**

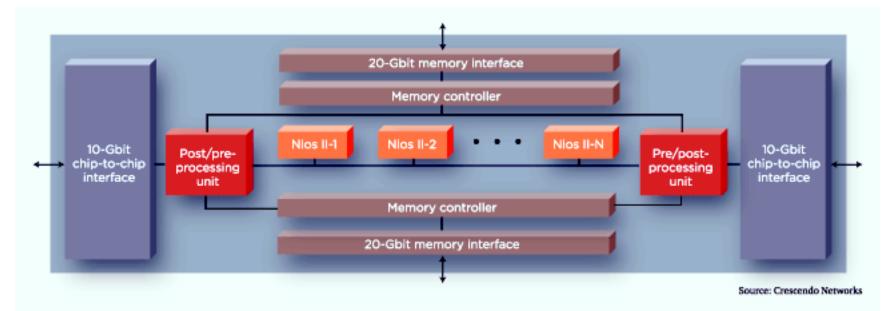

### **An Example: Crescendo Networks**

- A Programmable Eight-Processor Architecture

- Using Embedded Soft Processor Nios II

- On a Single FPGA

- For Layer 4/7 Applications

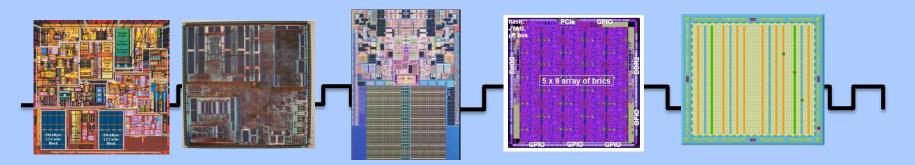

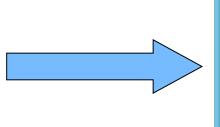

### **Following the Silicon Trajectory**

#### Convergence in hardware solutions

- Heterogeneity on-chip, interposer, 3D and SIP

- Embedded processing with dedicated programmable hardware

- Programmable substrate for full systems-on-chip

#### Enabling technologies

- HW/SW Co-design

- Ecosystem, Infrastructure and IP

- Differentiation through programmability

# Hardware-Software Co-Design for SoC FPGAs

© 2012 Altera Corporation—Confidential

### **SoC FPGA Programming Models**

- Traditional FPGA's programming model is RTL

- State machines, datapaths, arbitration, buffering, etc.

- Also need a programming model that represents an FPGA as:

- Processor with hardware accelerators

- Configurable multi-core device

### **C/C++ Compilers for FPGAs**

#### Several commercial offerings

- C/C++/System C High-Level-Synthesis to RTL

- C-to-Silicon Compiler (Cadence)

- Impulse C (Impulse Accelerated Technologies)

- Catapult C (Mentor)

- SynphonyC (Synopsys)

- AutoESL (now Xilinx)

- Cynthesizer (Forte),

- NEC

```

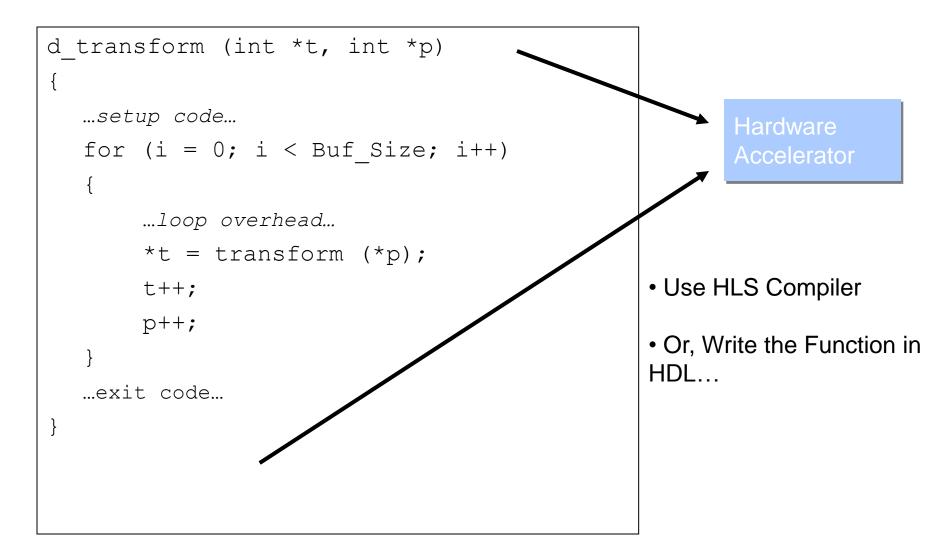

d_transform (int *t, int *p)

{

...setup code...

for (i = 0; i < Buf_Size; i++)

{

...loop overhead...

*t = transform (*p);

t++;

p++;

}

...exit code...

}</pre>

```

#### Integration of Embedded Processors and Hardware Accelerators in FPGAs: C2H

### **Identify the Software Bottleneck**

```

main ()

{ ...variable declarations...

init();

while (!error && got data())

{

do user interface();

gather statistics();

if (got new data())

d_transform(in_buf, out_buf);

check for errors();

cleanup();

}

```

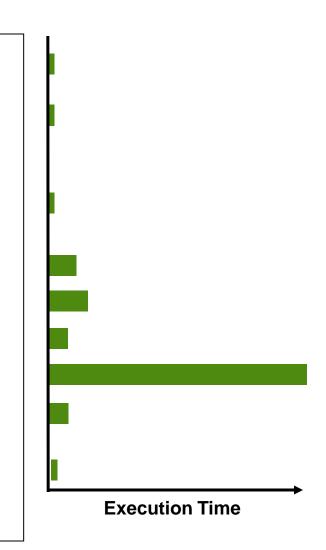

### **Compile C Function Into Hardware**

### **The Result**

```

main ()

{ ...variable declarations...

init();

while (!error && got data())

{

do user interface();

gather statistics();

if (got new data())

d_transform(in_buf, out_buf);

d transform S();

cleanup();

}

Execution Time

```

### **OpenCL Approach to SoC FPGA Programming**

\*\*\*\*\*\*\*\*\*\*\*

© 2012 Altera Corporation—Confidential

23

### What is OpenCL?

- OpenCL is a programming model developed by the Khronos group to support multi-core programming and silicon acceleration

- An industry consortium creating open API standards

- Commitment to royalty-free standards

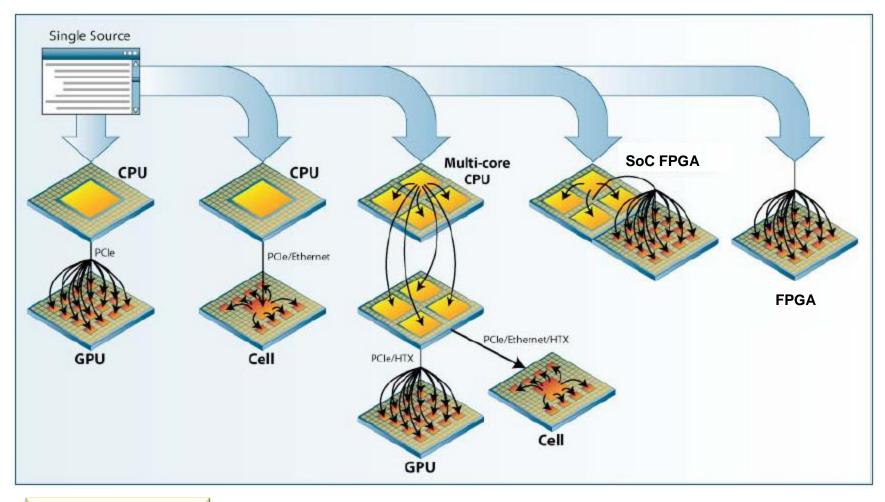

### **OpenCL Portability**

Source: RapidMind

### **OpenCL Structure**

- Natural separation between the code that runs on accelerators and the code that manages those accelerators

- The "host" code is pure software that can be executed on any sort of conventional microprocessor

- Soft processor, Embedded hard processor, external x86 processor

- The kernel code is 'C' with a minimal set of extensions that allows for the specification of parallelism and memory hierarchy

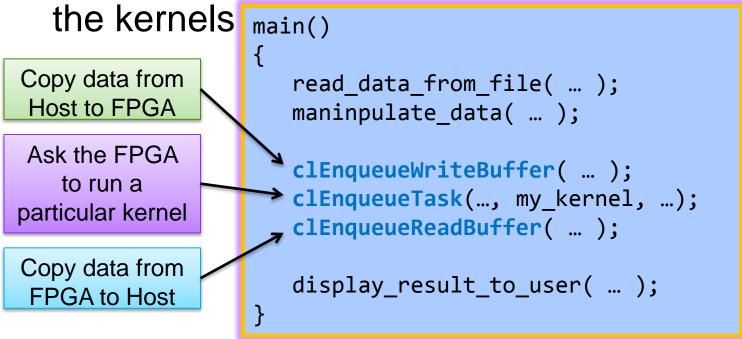

## **OpenCL Host Program**

- Pure software written in standard 'C'

- Communicates with the Accelerator Device via a set of library routines which abstract the communication between the host processor and

### **System Integration**

© 2012 Altera Corporation—Confidential

29

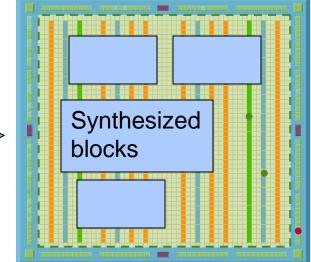

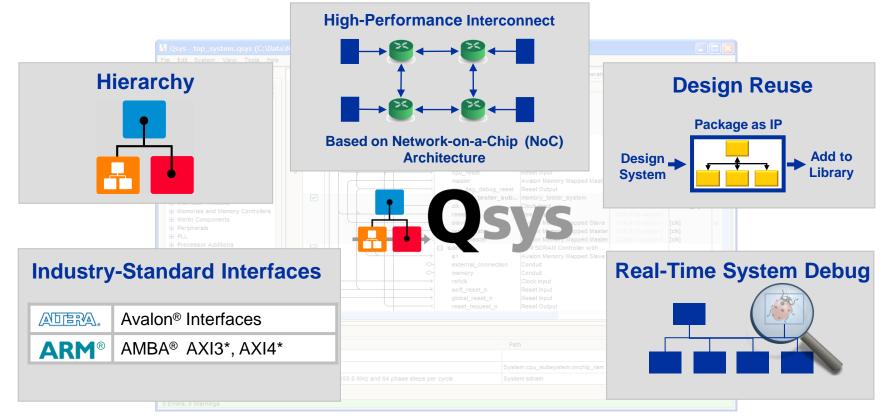

## **Qsys System Integration Platform**

- Qsys is Altera's design environment for

- Deployment of IP

- Deployment of reference designs and example designs

- Development platform for Altera custom solutions

- Design platform for customers to quickly create system designs

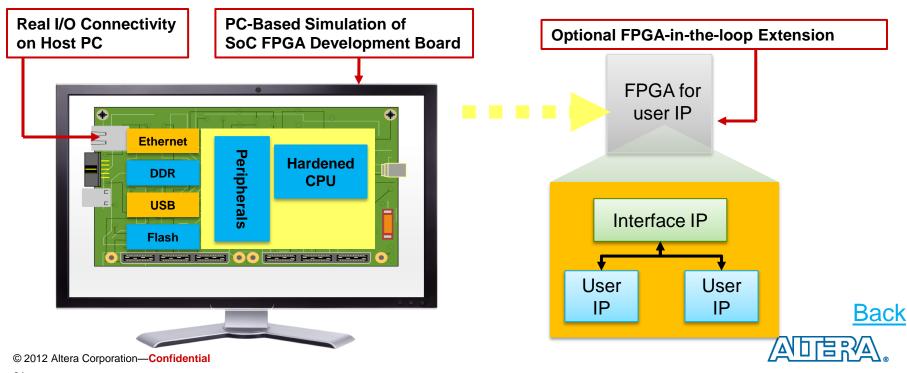

### **SoC Virtual Target**

Immediate device-specific software development

- Binary- and register-compatible

- Virtual prototyping technology

- Linux and VxWorks enabled, compatible with ARM tools

### **Summary**

### The Era of Silicon Convergence

SoC FPGAs and Programmable Substrate

### The Era of New Embedded Software

- HW/SW co-design and parallel programming

### The Era of Innovation

- Exploiting heterogeneous, customizable devices

- Massively parallel embedded programmable solutions

### **Thank You**

#### © 2012 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at <a href="http://www.altera.com/legal">www.altera.com/legal</a>.