# **3D-IC/TSV Design** *EDA Software Requirements*

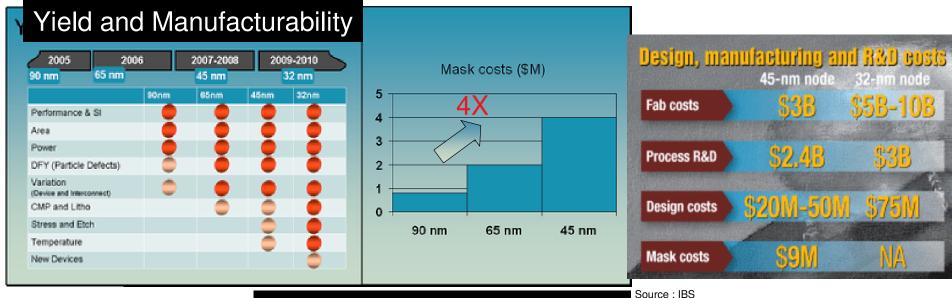

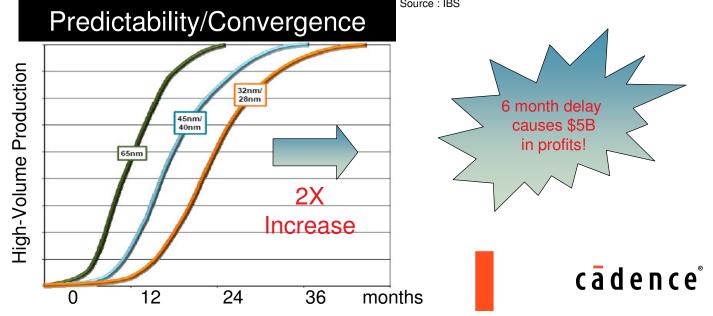

# An Inconvenient Truth "Cost is the New Driver"

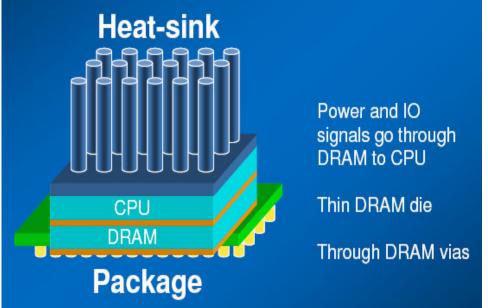

## Why 3D Stacked Dies/TSV?

Source: Inte

### 3D technology will help:

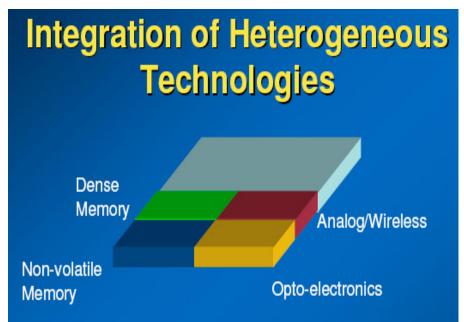

- Integration of heterogeneous technologies

- Lower interconnect power

- Lower system cost

cādence°

Do not want to end up like this!

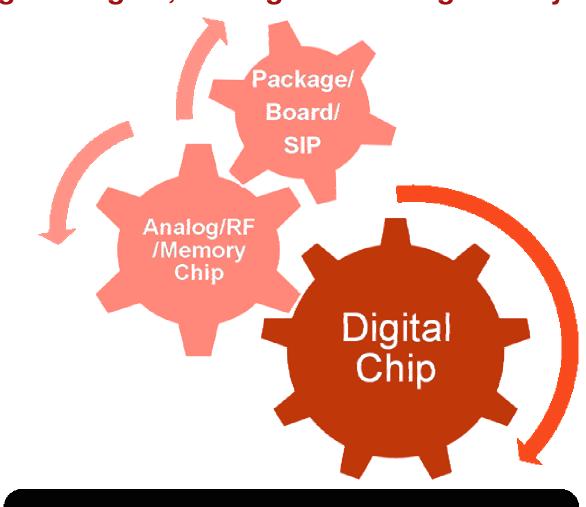

## 3DIC: It is a Heterogeneous Stack

Co-Design of Digital, Analog and Package is Key

Enabling Heterogeneous System

Closer IC Integration through OA

Co Design is Most essential

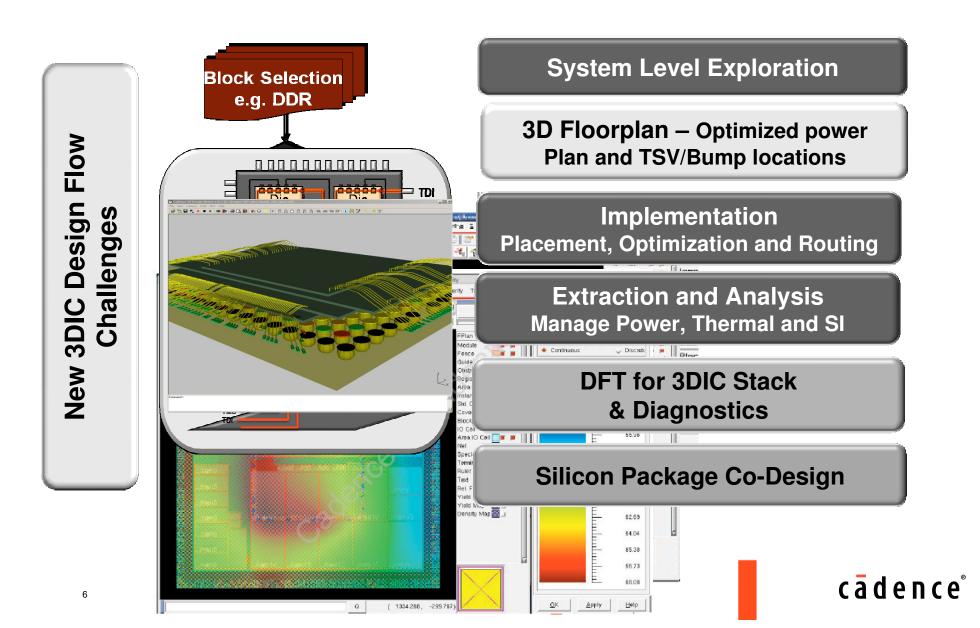

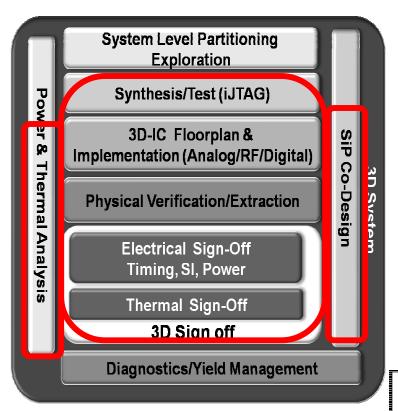

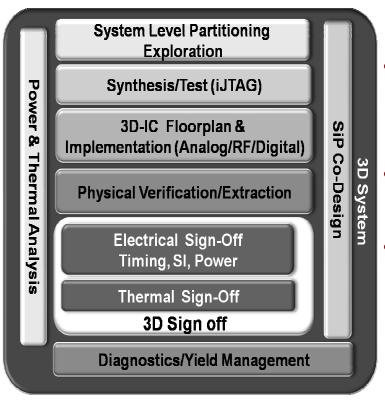

## **3DIC Design Flow Challenges**

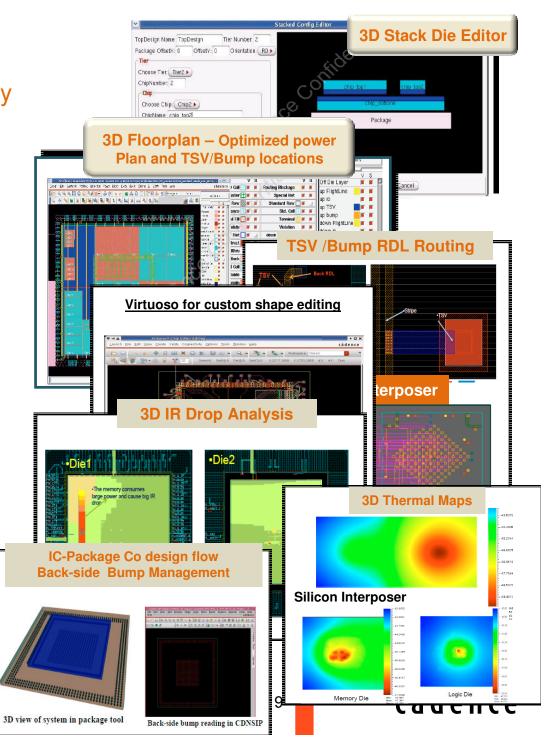

# So what changes in the EDA world? Revamped EDA requirements

New Layout Rules (e.g. alignments)

New Layout Layer (e.g. Back Side RDL)

New Layout & Electrical Feature (e.g. TSV)

New Floorplanning & Blockage Rules (TSV)

Thermal & mechanical constraints

**New Models, Rules**

## **Cadence 3DIC Silicon Realization**

#### INTENT

#### **ABSTRACTION**

#### **CONVERGENCE**

### 3D-IC EDA Design Tools

Plan->Implement->Test->Verify

**Cadence 3D IC Flow**

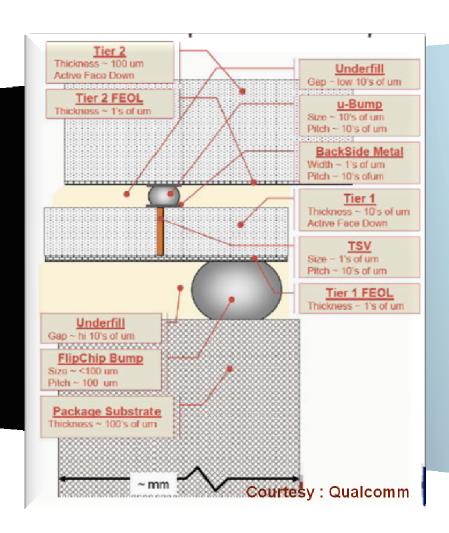

## 3D-IC: Qualcomm + Cadence

Source: RTI 3D conference 2009 proceedings

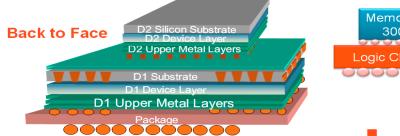

#### Thermal Design Objectives in 3D IC

- Communication chip design uses low power techniques (~ 1 Watt). Will stacking low power chip together produce thermal hot spot.

- We know that microprocessor's power consumption is at least in the 10's of Watts. Stacking with high powered devices have been reported to have thermal challenges in 3D IC.

- If the low power stack does exhibit thermal hot spots:

- Can regular thermal optimization improve hot spots.

- Example: Thermal TSV, thermal micro-bumps, better inter-chip material.

- · By how much?

- Examine other areas to improve on thermal management.

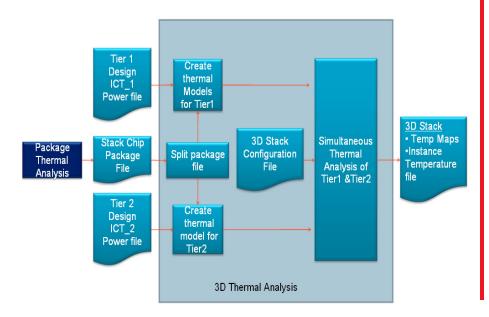

#### **Thermal Analysis Flow For Two Chip TSS**

#### Construction of a Two Chip Stack Design

- EDI (Encounter Digital Implementation) System is used to construct the following stack for thermal management experiments.

- Memory Chip (Black Box Physical Model)

- · 4 Quadrant of memory banks

- · Four quadrants of micro-bumps.

- An SOC logic chip (existing design)

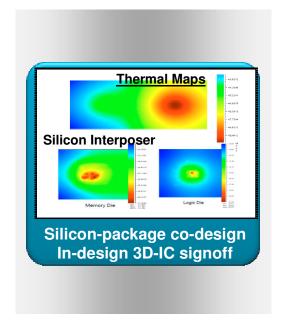

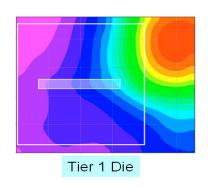

#### Thermal Gradients

- Significant Thermal Gradients seen across both die

- 5C to 20C delta across Tier 1 die depending on power scenario

- Hot spot due to high power block on Tier1 die

- T1 hot spot vs T2 hot spot temp 3C to 10C depending on power case

- Thermal coupling between die is very good

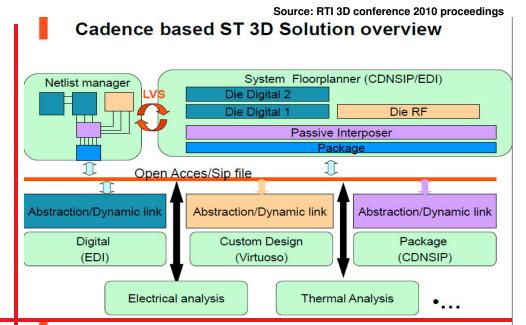

## 3D-IC: STMicroelectronics + Cadence

Analog RF

Silicon Interposer

Package Substrate

Three chips are placed faced down on top of silicon interposer.

Silicon interposer: 4-9 levels of high density Interconnect.

- No active areas.

- Passive devices like metal capacitances.

Challenges: Physical design, electrical analysis, power distribution and analysis and thermal management.

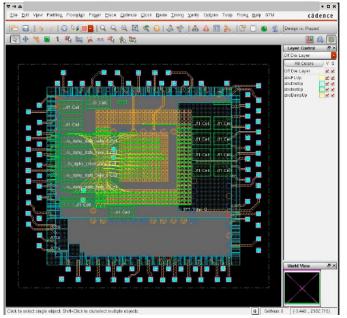

#### Top view of interposer with TOP die in ghost view

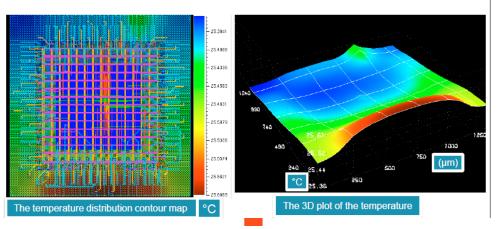

#### Thermal Analysis Results

- Thermal Analysis Provides a Rich of Thermal Data

- 2D Thermal contour can be displayed on each chip.

- 3D Thermal Map.

- Thermal values per layer and per x,y coordinates.

- The example below has small power consumption → thermal gradient is small

## Cadence Silicon-Proven 3D-IC Solution

## **Enabling 3D-IC Silicon Realization**

- Complete, integrated 3D-IC solution

- Tools: Plan->Implement->Test->Verify

- 1st to market 'wide I/O memory controller'

- Developed in close partner-collaboration

- Leading foundries and customers

- Multiple 3D-IC tapeouts

- Memory over logic (28 nm), logic over analog, logic over Logic, 3-stack dies

- Production design mid-2011 tape-out