cādence°

# EDA360 - Is End-to-End Design a Riddle, a Rebus, or a Reality?

April 7, 2011

### cādence°

### cādence°

cādence°

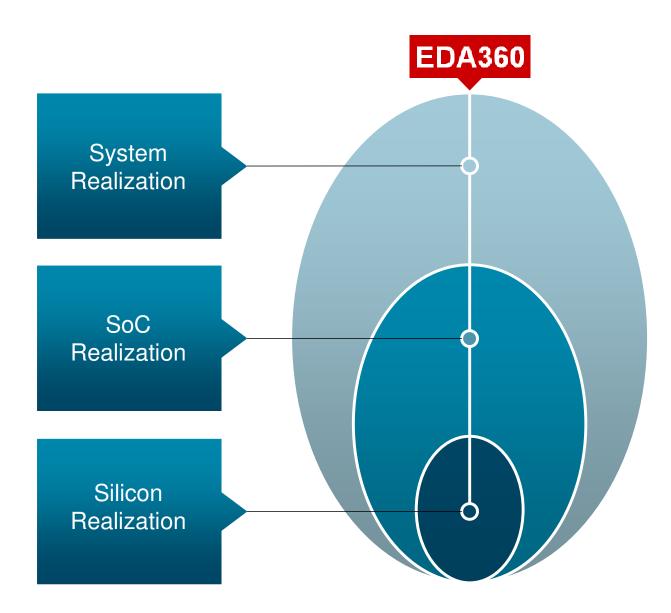

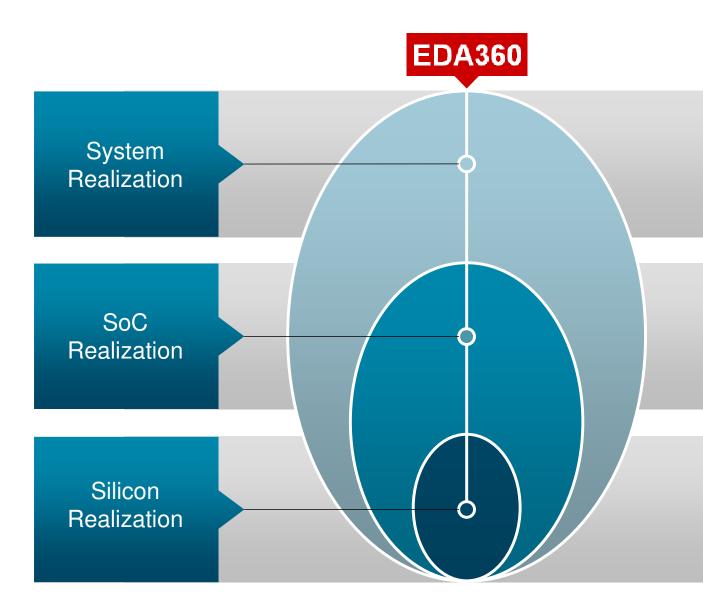

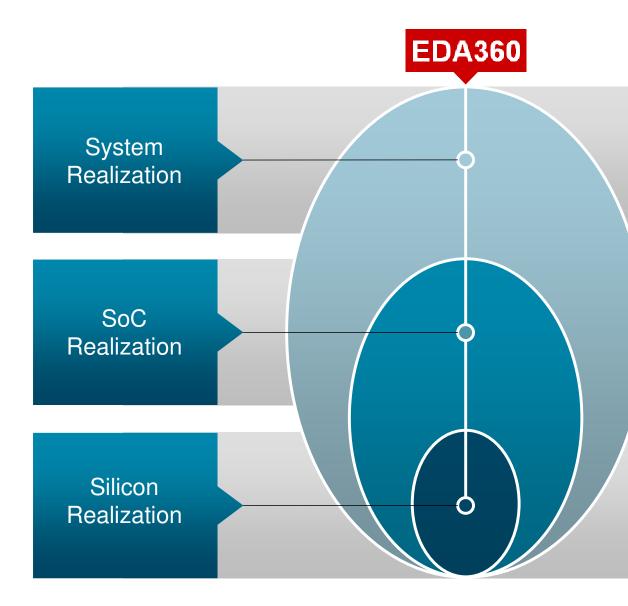

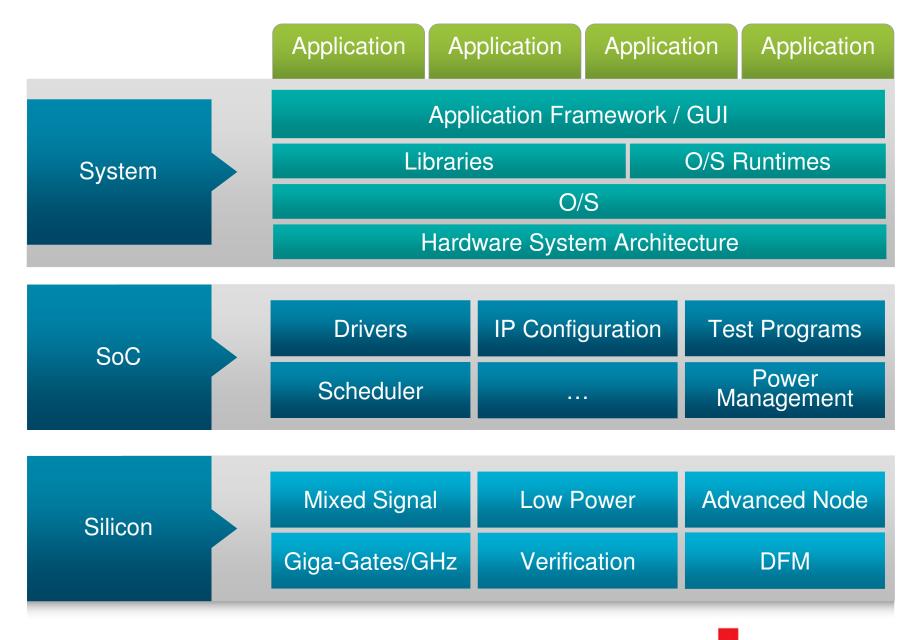

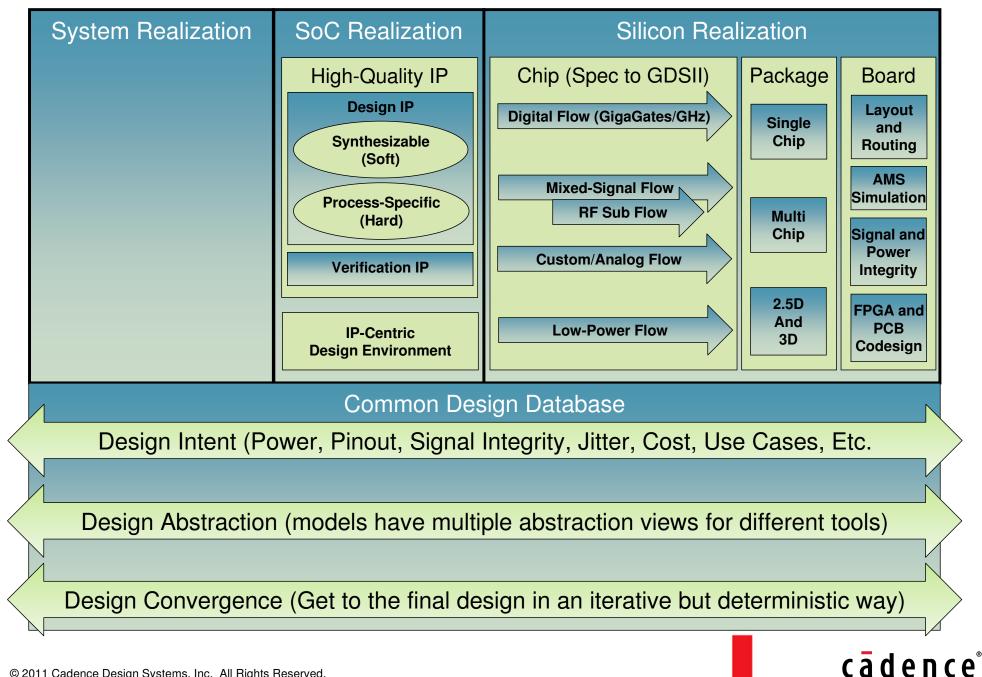

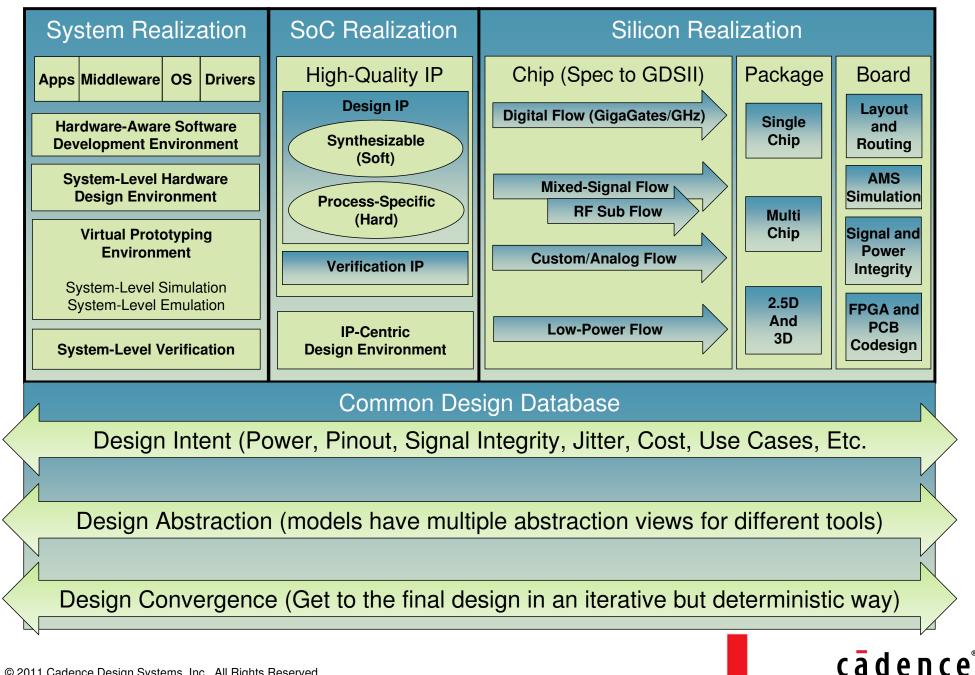

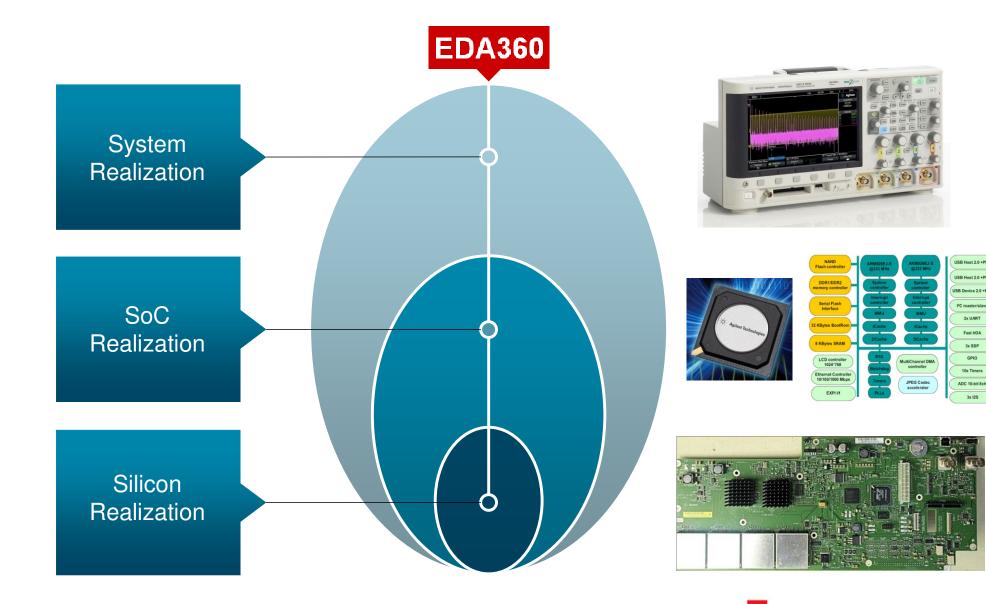

Software content (IP), tools, and services that enable hardware-aware system development and verification

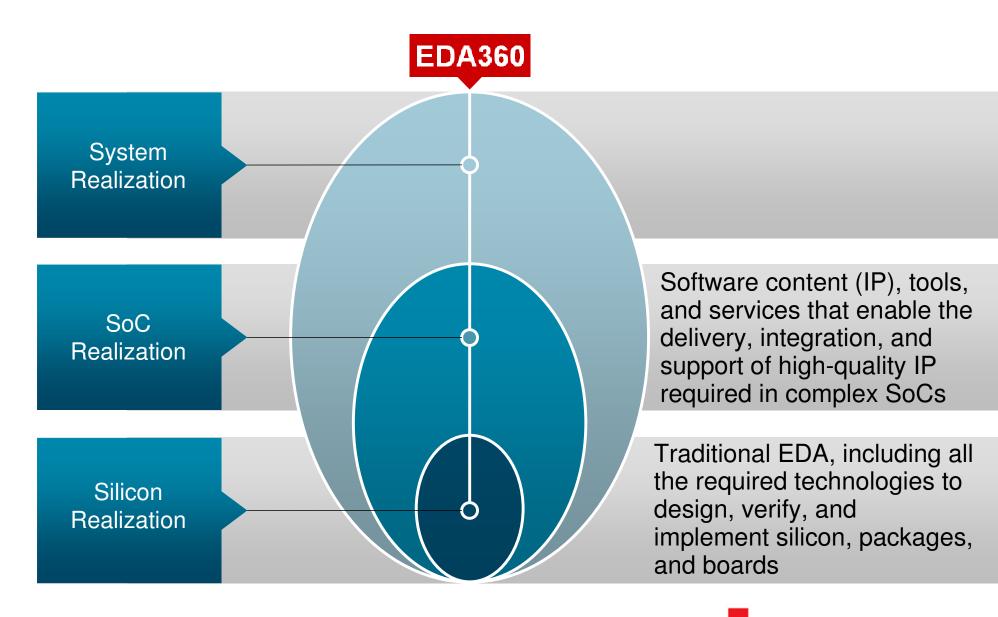

Software content (IP), tools, and services that enable the delivery, integration, and support of high-quality IP required in complex SoCs

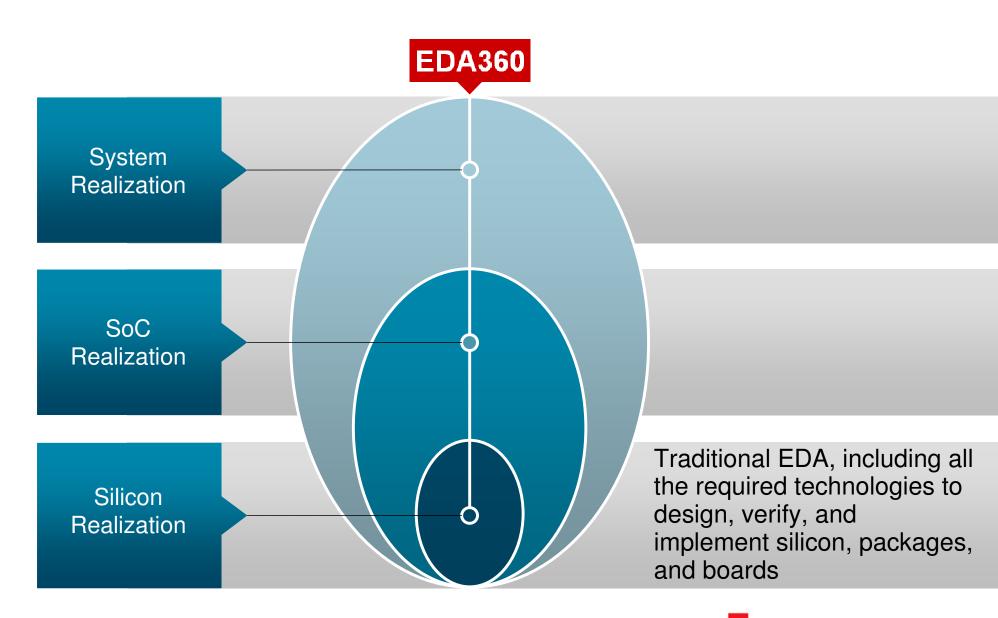

Traditional EDA, including all the required technologies to design, verify, and implement silicon, packages, and boards

### cādence°

## Silicon Realization – Customer Challenges

- Time to market

- Disaggregated, global design chain limits visibility and predictability for complex designs – causing schedule delays and respins

- Lack of true holistic and integrated silicon-package-board flows causes productivity gap

- Reuse

- Profitability

- Design failure catastrophic

- Functionality, performance, and power improvements contribute to higher margins

- Manufacturability

cādence

## **System Realization – Customer Challenges**

- Software development trails hardware development, impacting time-to-market

- Hardware-software integration complexity impeding product shipments, quality

- Effective and predictable system and sub-system verification

cādence

8

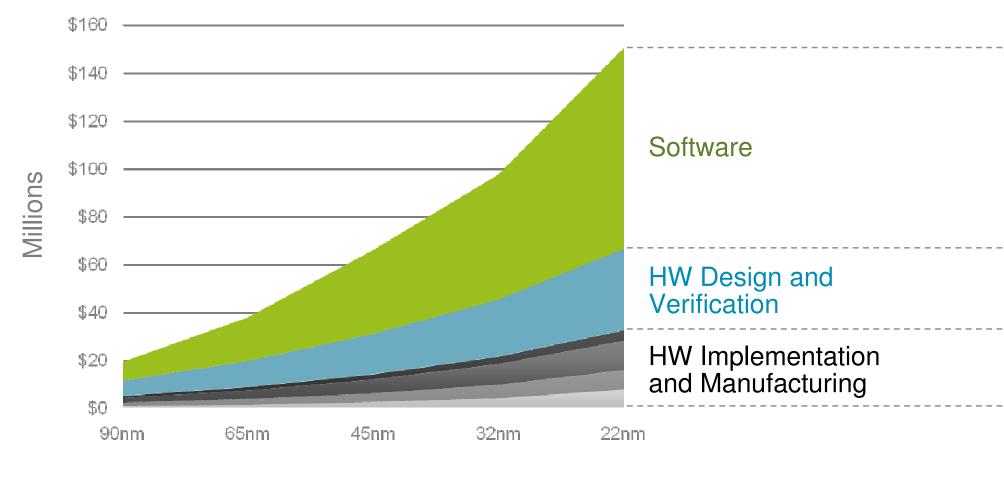

### System Realization – Market Landscape Development costs rising

cādence

Source: IBS 2009

### System Realization – Market Landscape Market window shrinking; growing penalties for delay

12 months Product Delay 9 months East Market Medium Market 6 months Slow Market 3 months 0% 20% 40% 60% Source: IBS Percent Revenue Loss

cādence

IC Revenue Loss Due to Product Delay

## Sample Challenges at Each Realization Layer

### cādence<sup>®</sup>

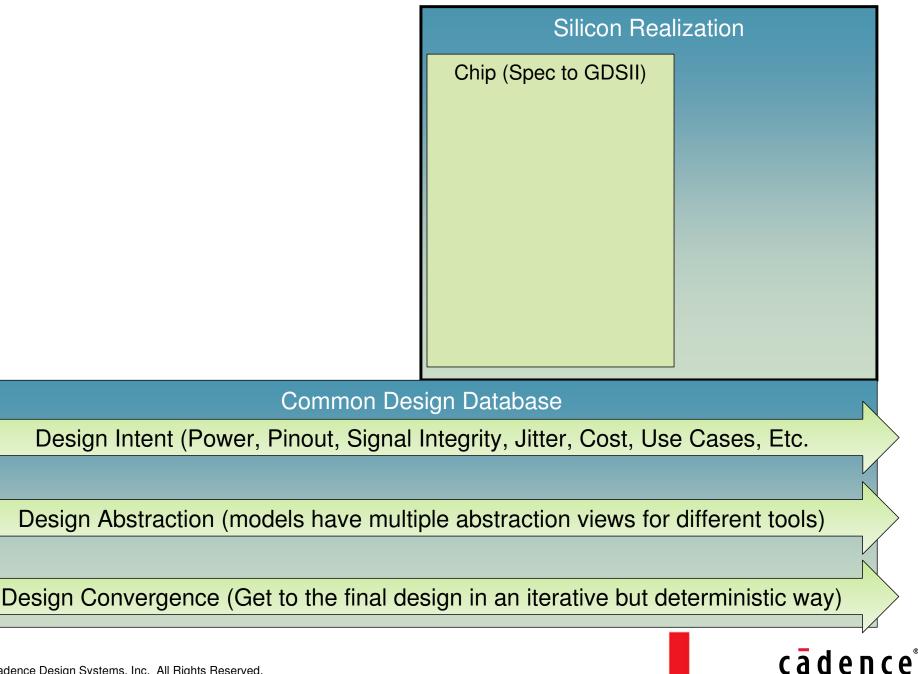

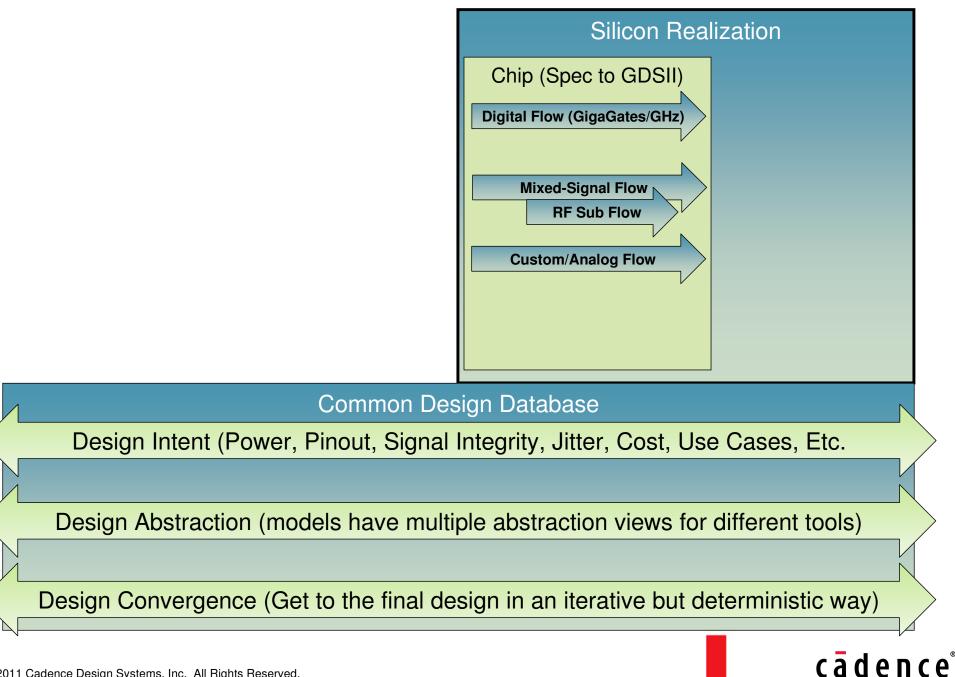

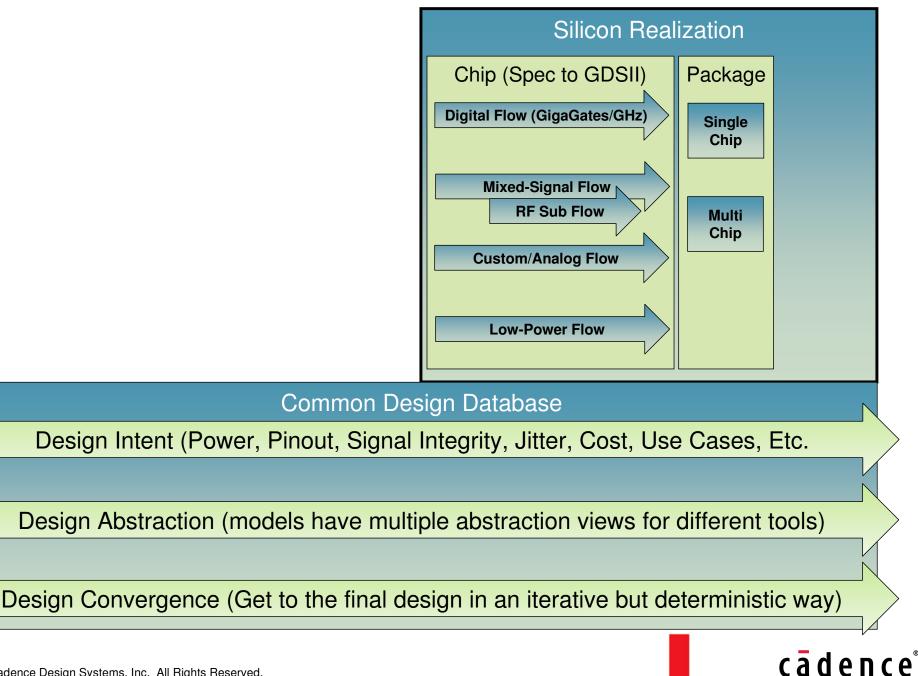

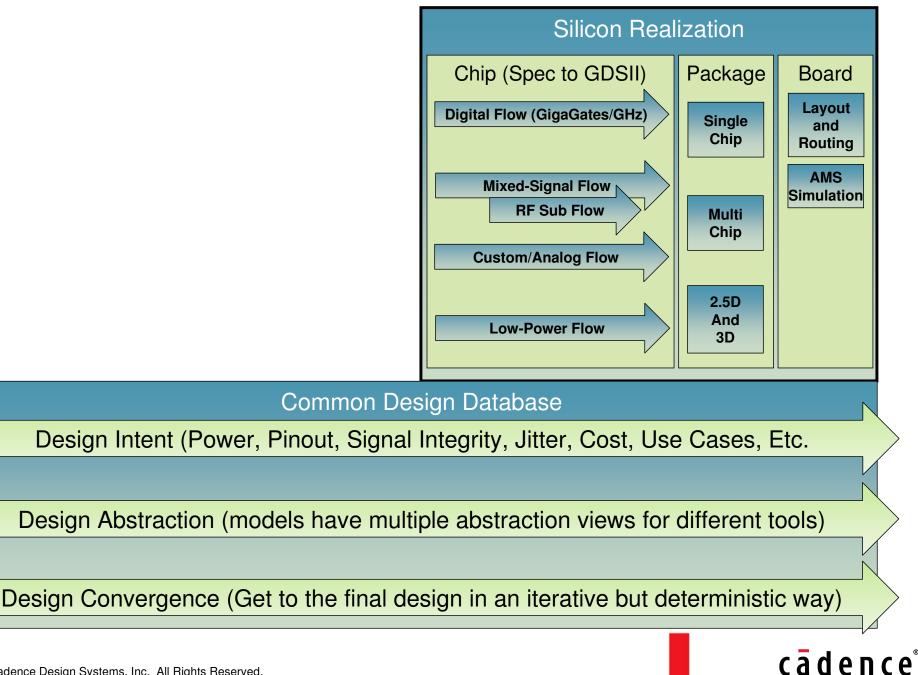

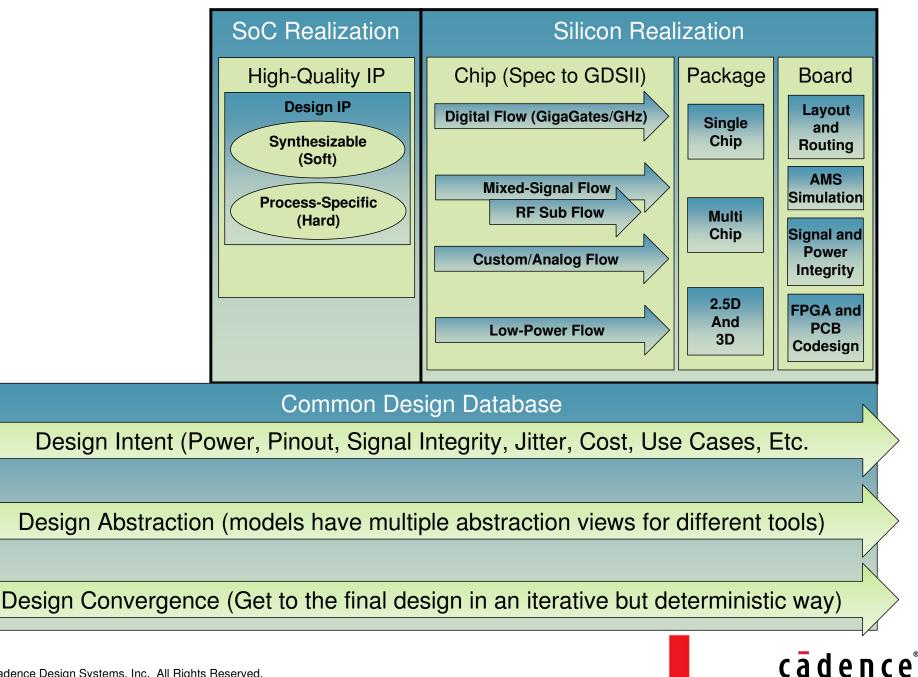

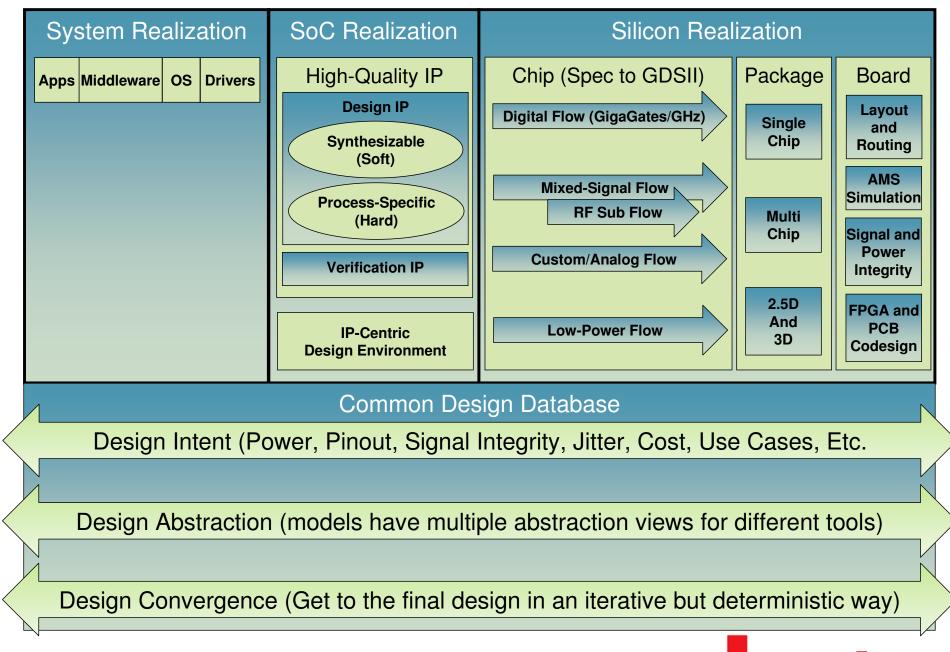

Common Design Database

12 © 2011 Cadence Design Systems, Inc. All Rights Reserved.

### cādence°

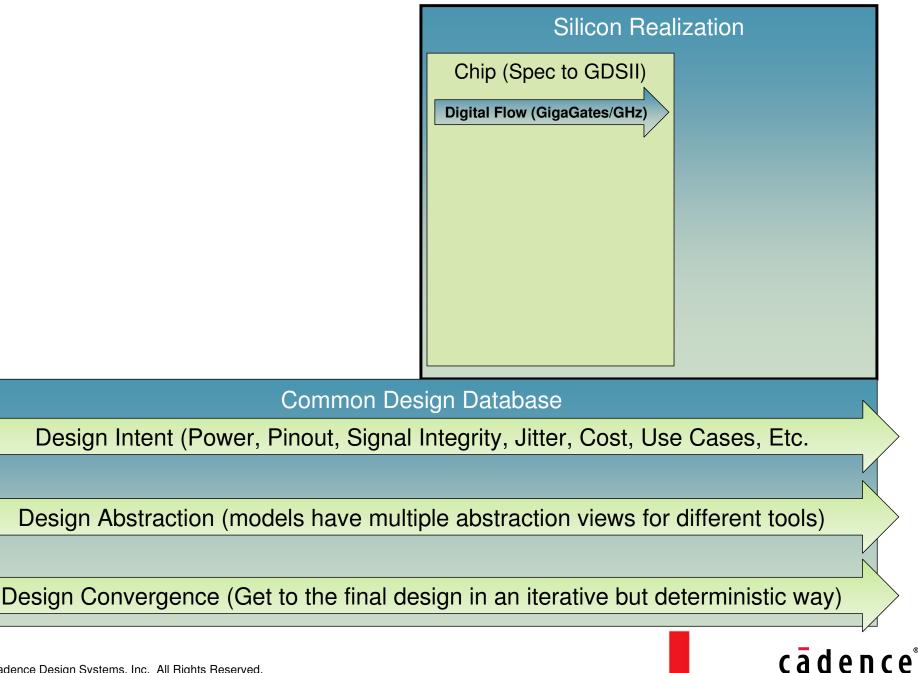

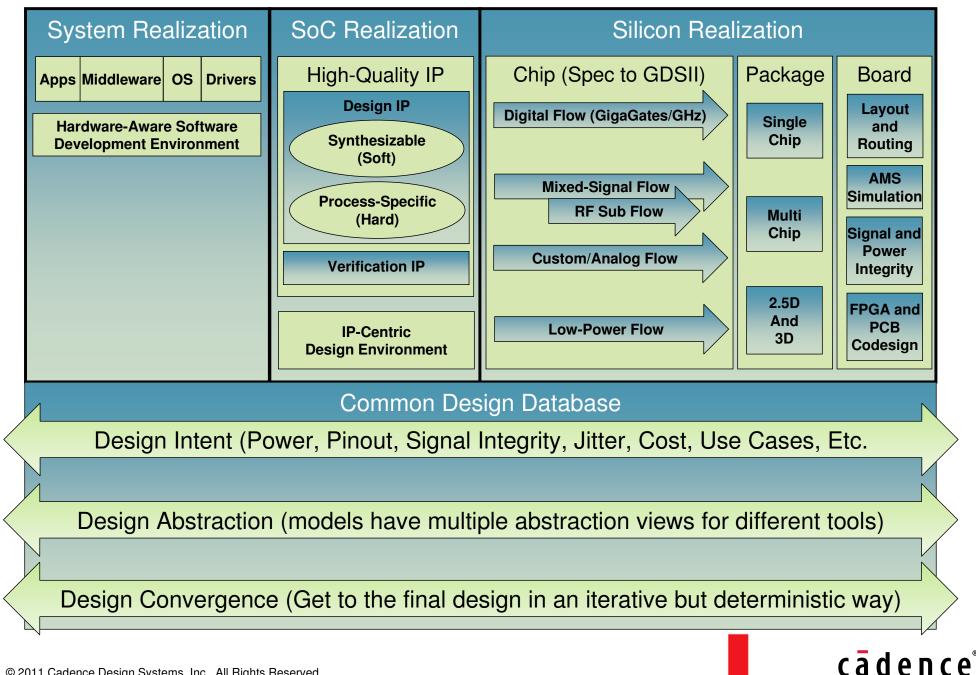

Common Design Database

Design Intent (Power, Pinout, Signal Integrity, Jitter, Cost, Use Cases, Etc.

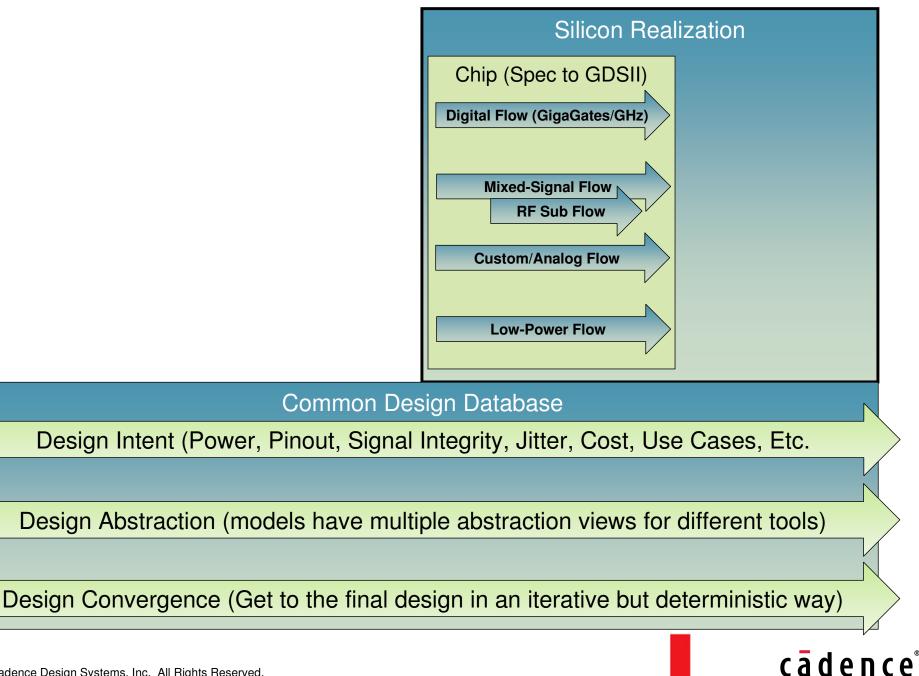

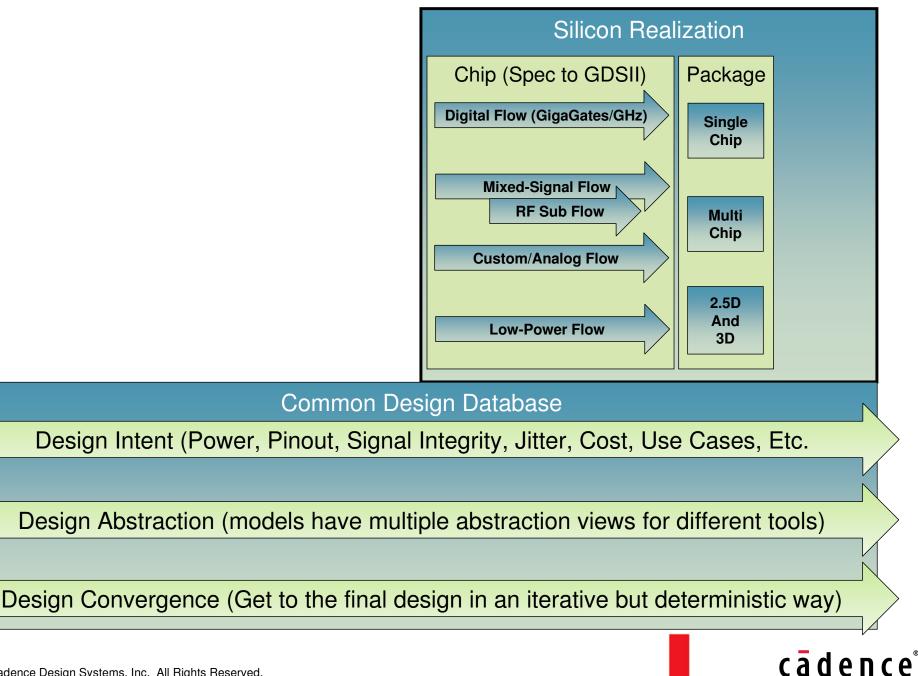

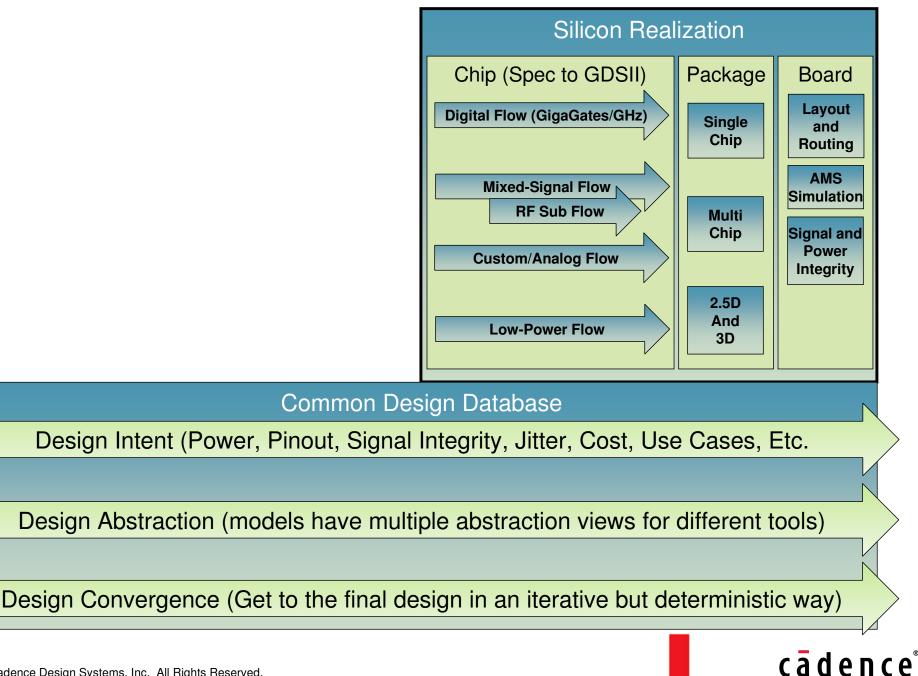

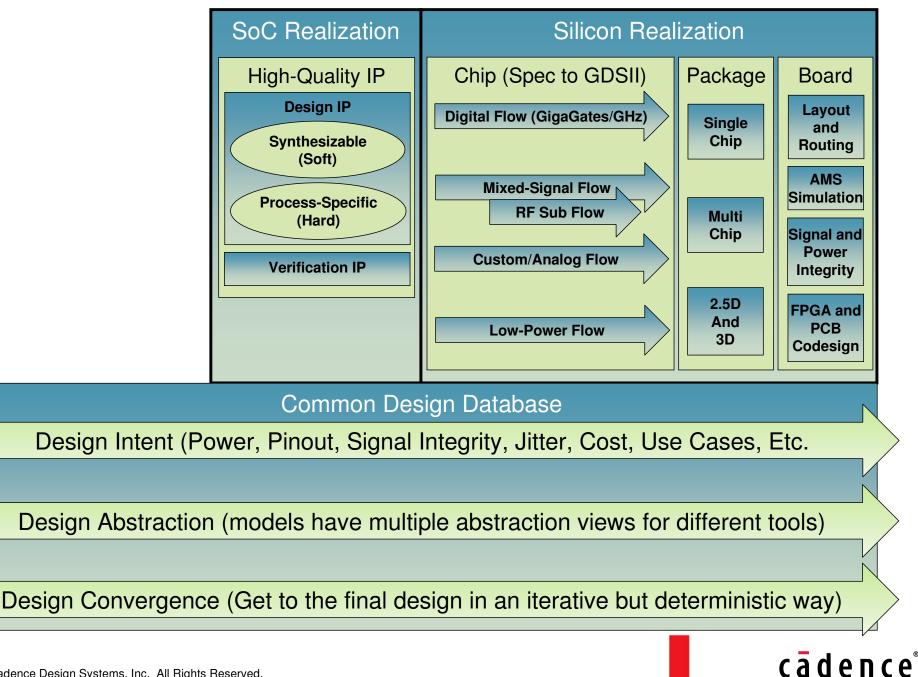

### cādence<sup>®</sup>

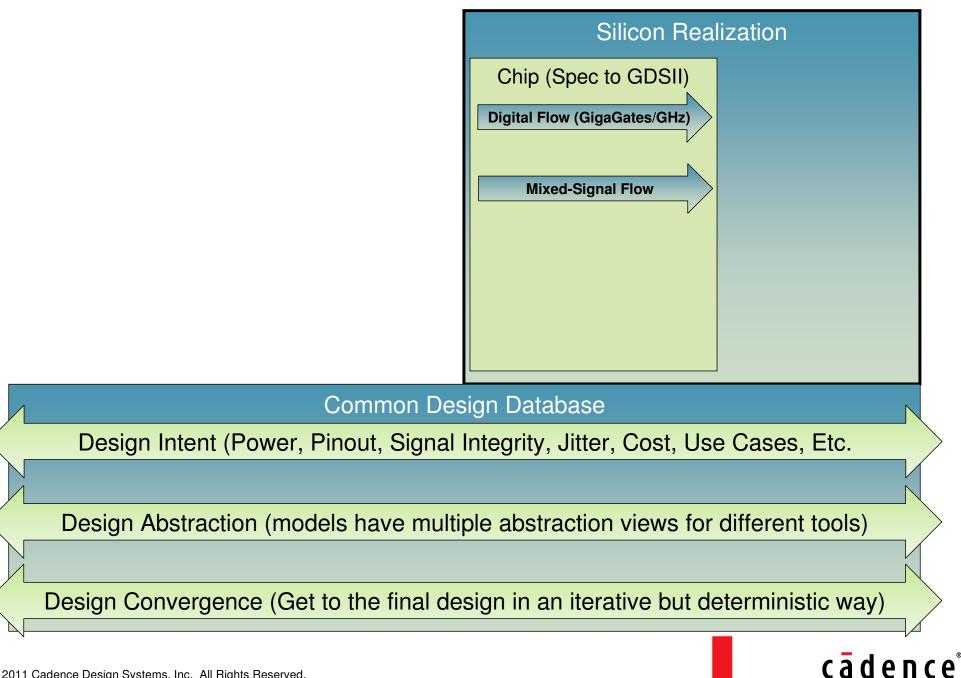

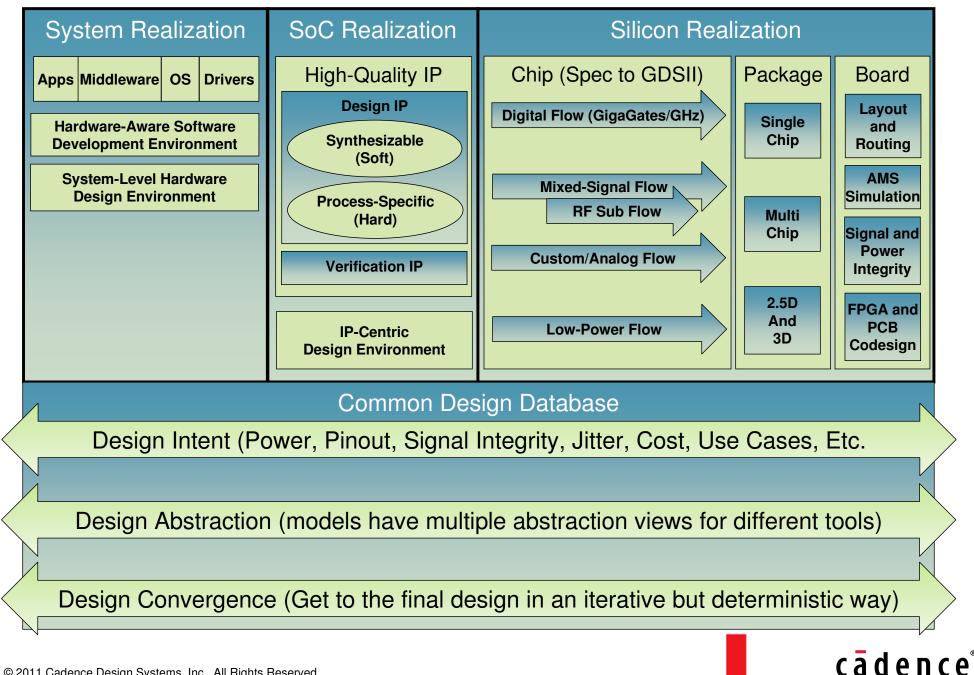

Common Design Database

Design Intent (Power, Pinout, Signal Integrity, Jitter, Cost, Use Cases, Etc.

Design Abstraction (models have multiple abstraction views for different tools)

### 14 © 2011 Cadence Design Systems, Inc. All Rights Reserved.

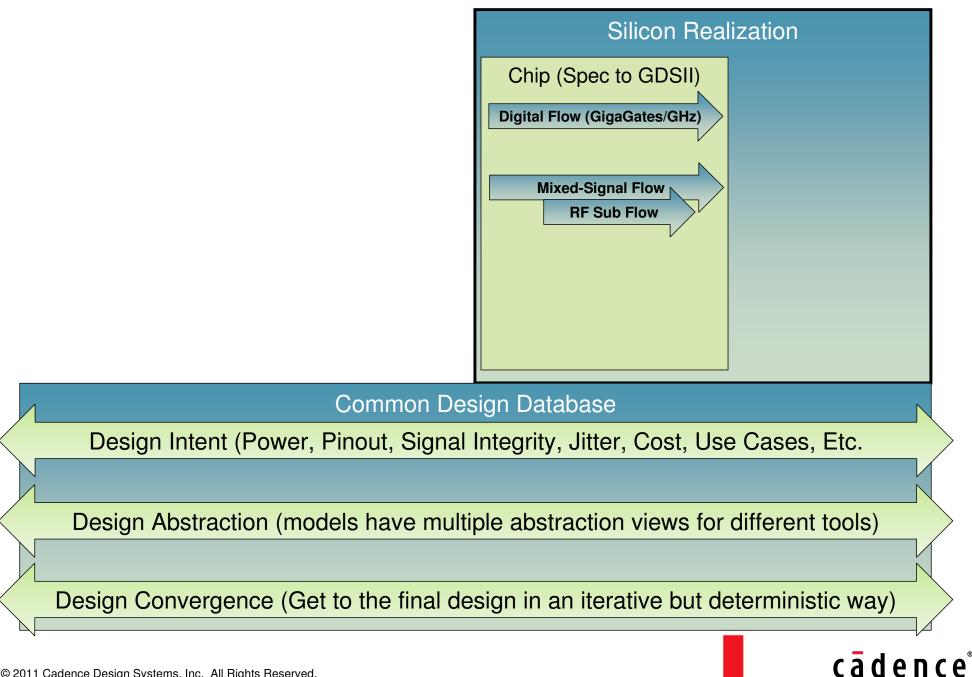

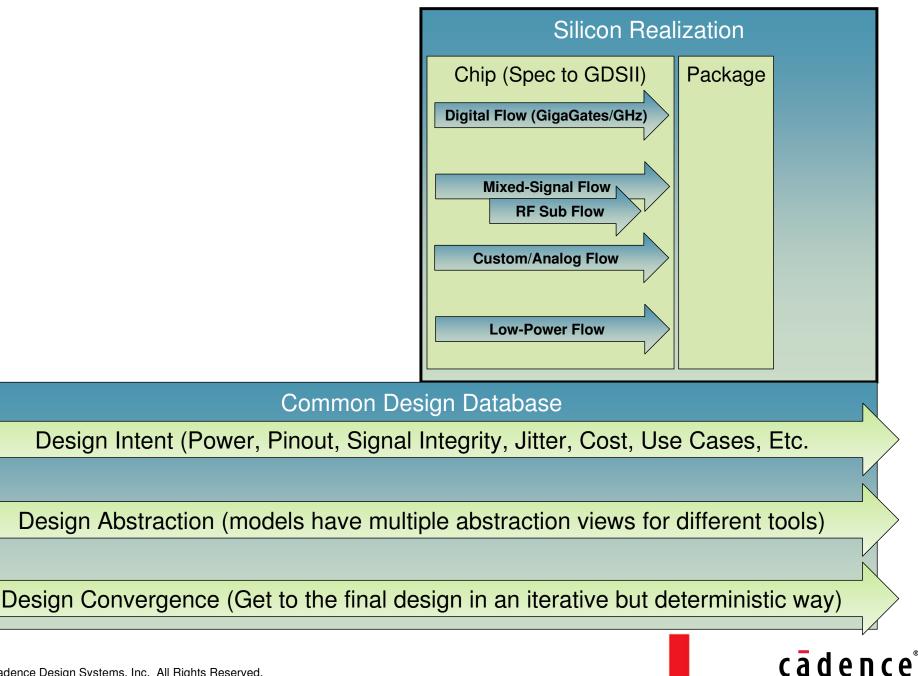

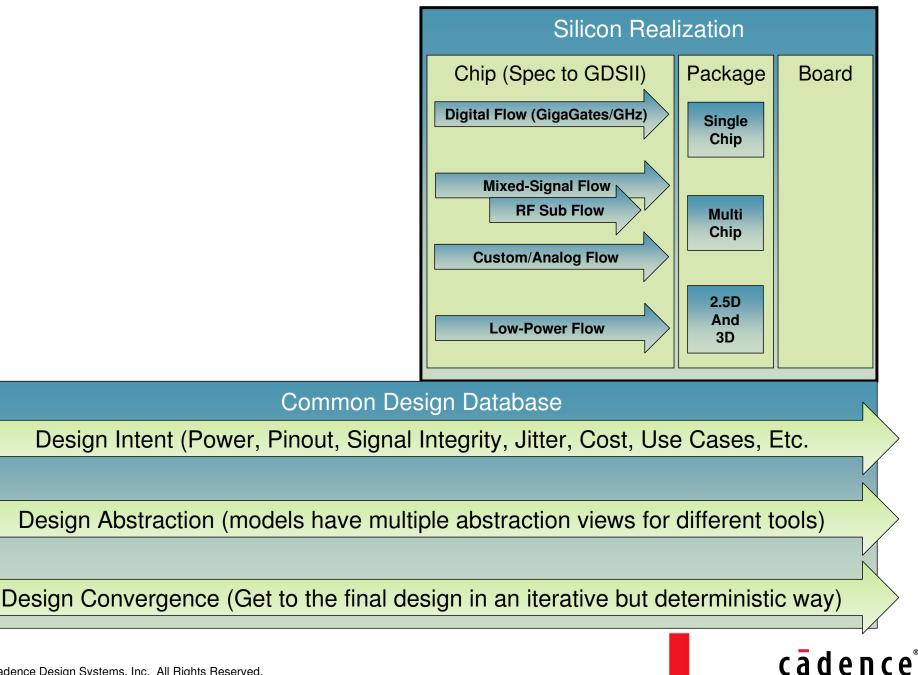

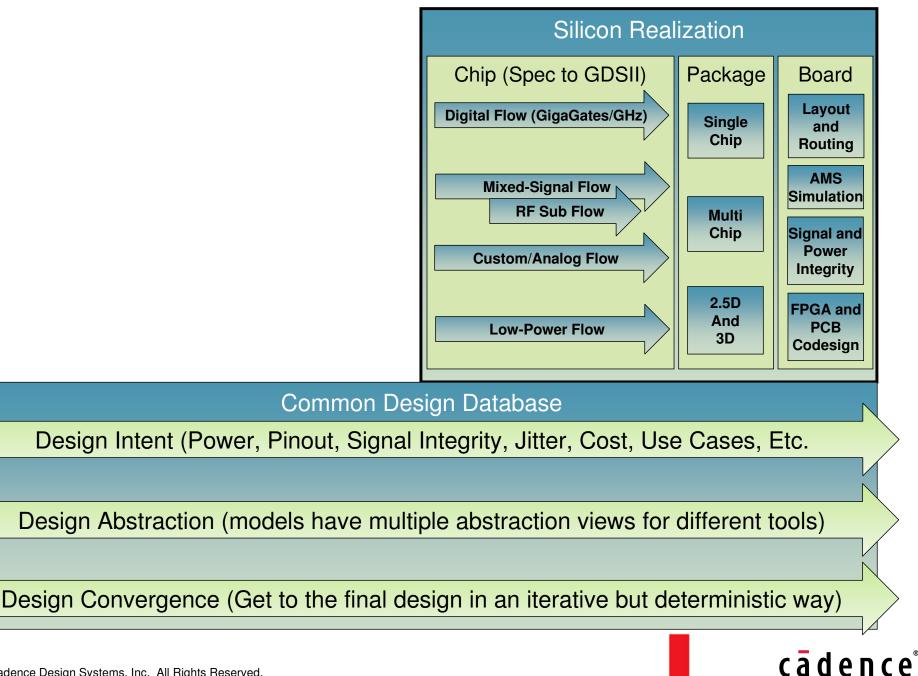

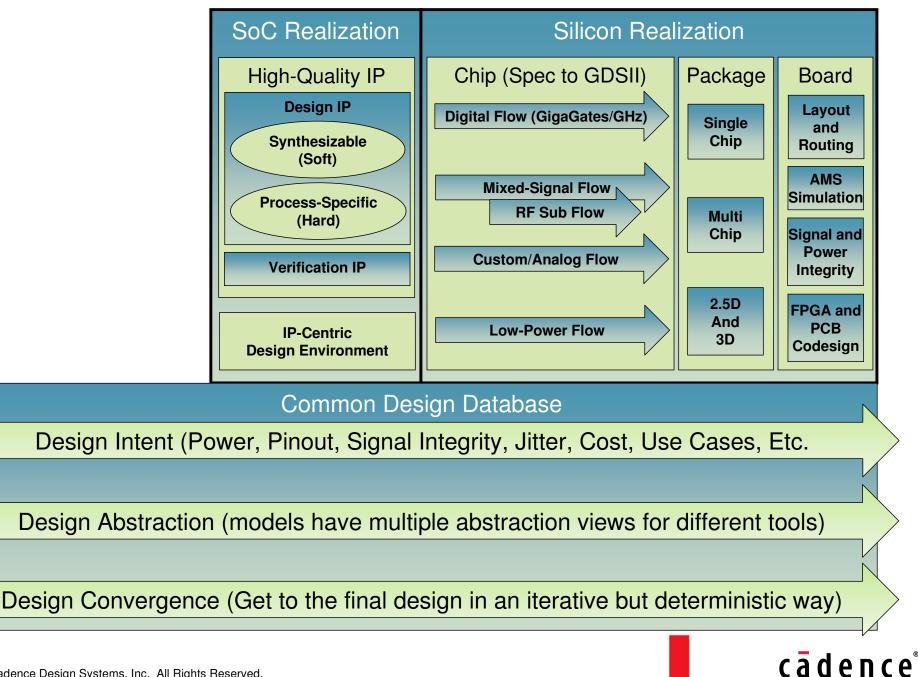

### cādence°

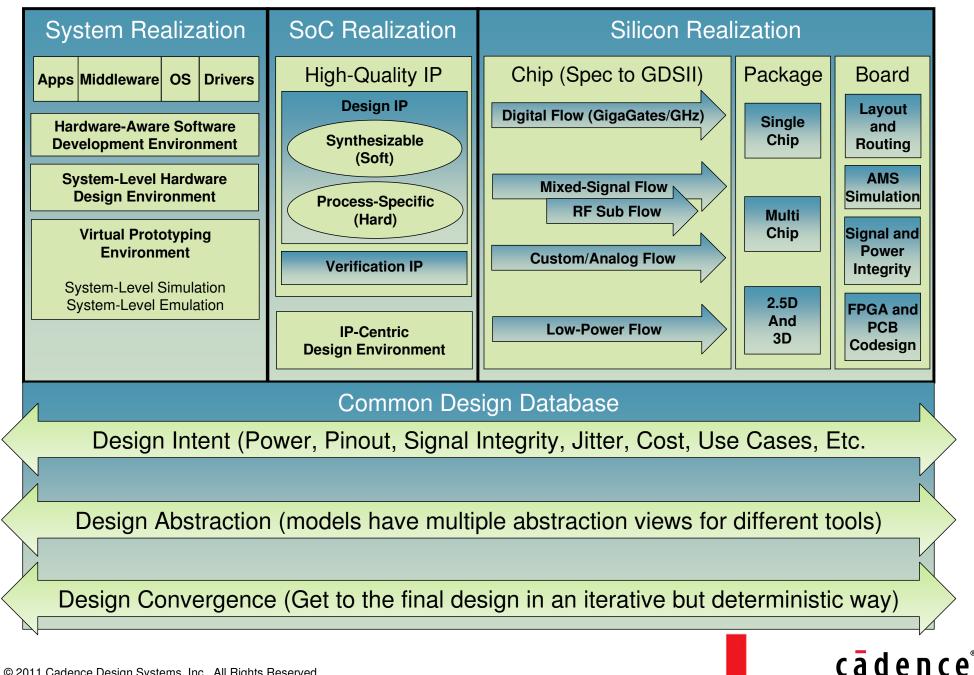

Common Design Database

Design Intent (Power, Pinout, Signal Integrity, Jitter, Cost, Use Cases, Etc.

Design Abstraction (models have multiple abstraction views for different tools)

Design Convergence (Get to the final design in an iterative but deterministic way)

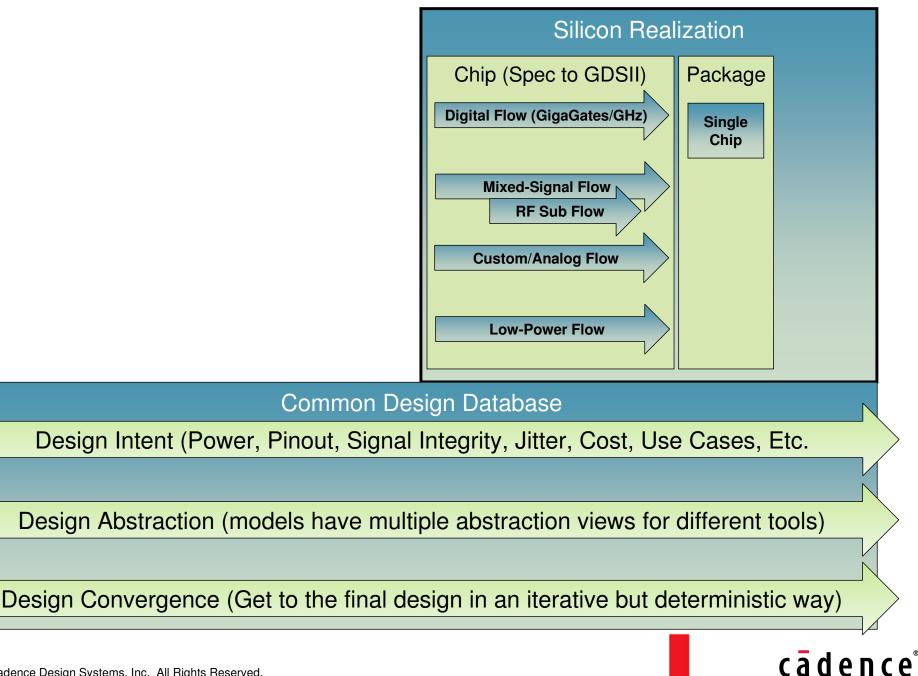

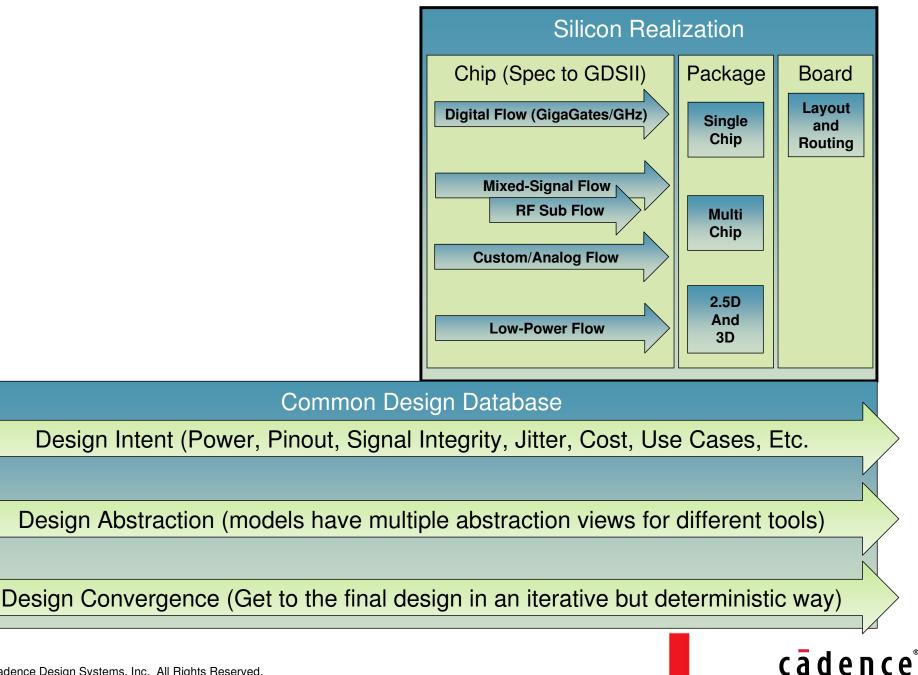

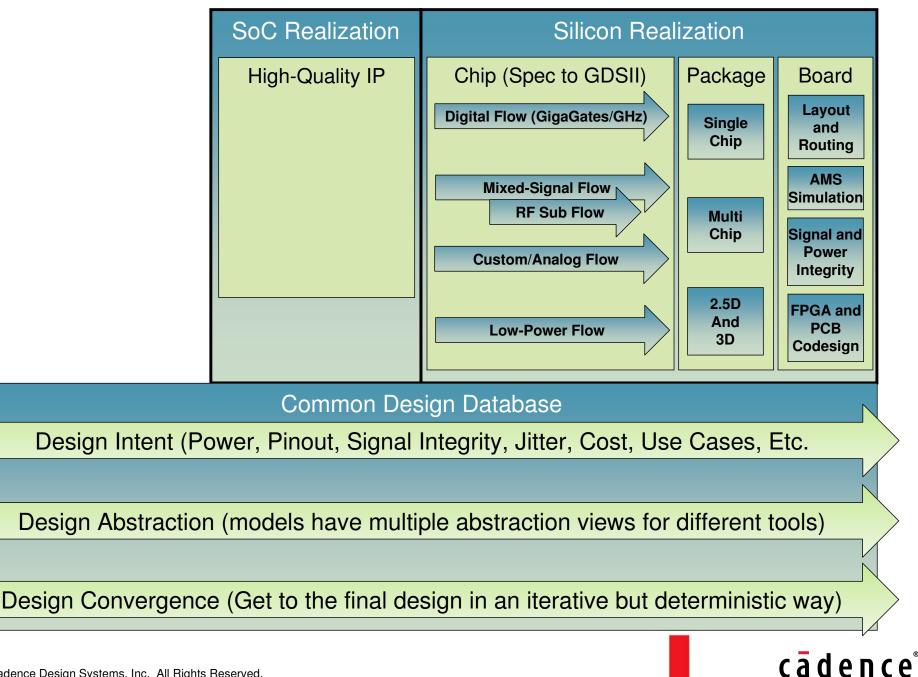

cādence

Silicon Realization

Design Intent (Power, Pinout, Signal Integrity, Jitter, Cost, Use Cases, Etc.

Design Abstraction (models have multiple abstraction views for different tools)

Design Convergence (Get to the final design in an iterative but deterministic way)

### 16 © 2011 Cadence Design Systems, Inc. All Rights Reserved.

cādence®

## **EDA360 Case Study:** Agilent InfiniiVision Digital/Mixed-Signal Sampling Oscilloscope

Reproduced with Permission, Courtesy of Agilent Technologies, Inc.

Note: This case study is based on public, published data and <u>nothing</u> is implied about the EDA tools used to develop this product.

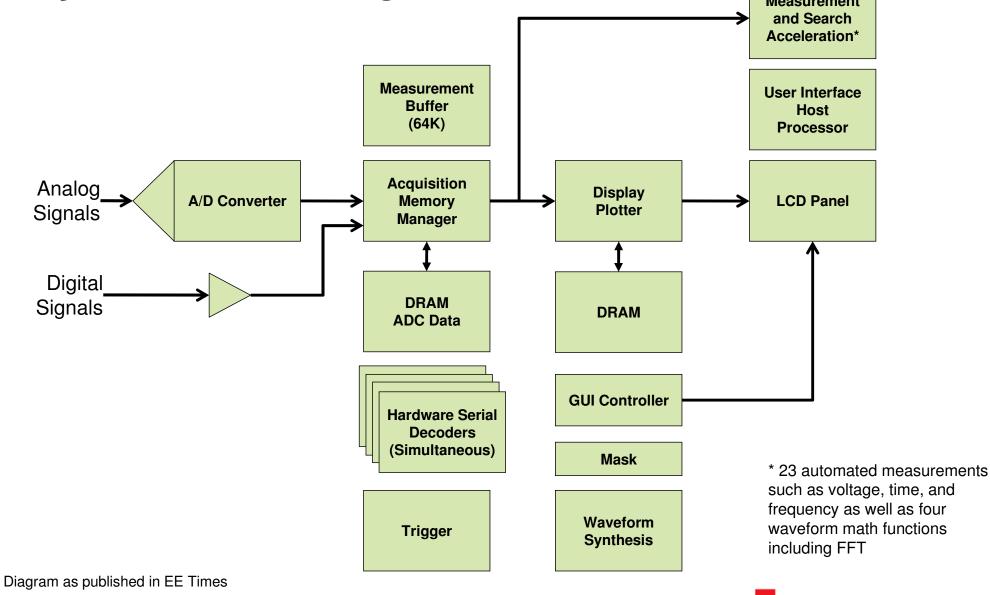

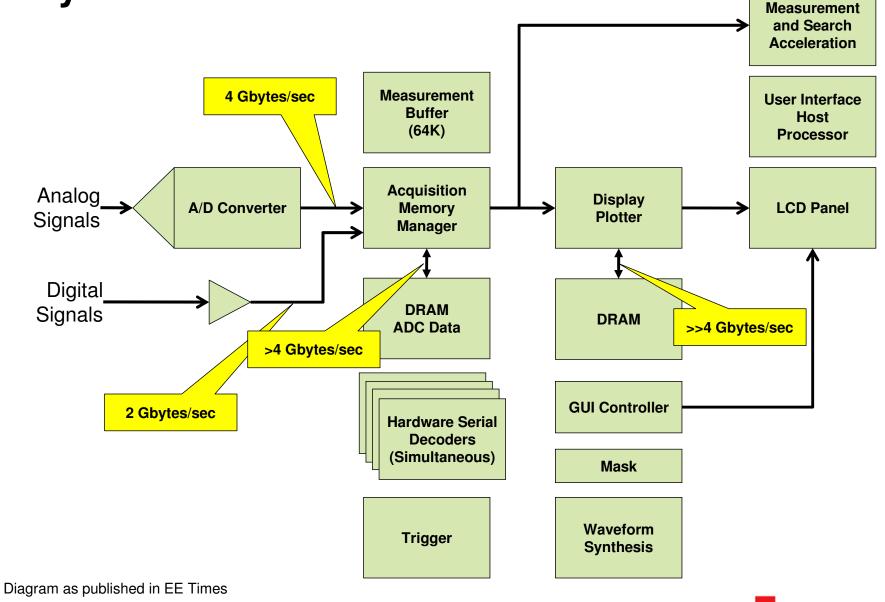

## Agilent InfiniiVision 2000/3000 DSO/MSO System Block Diagram

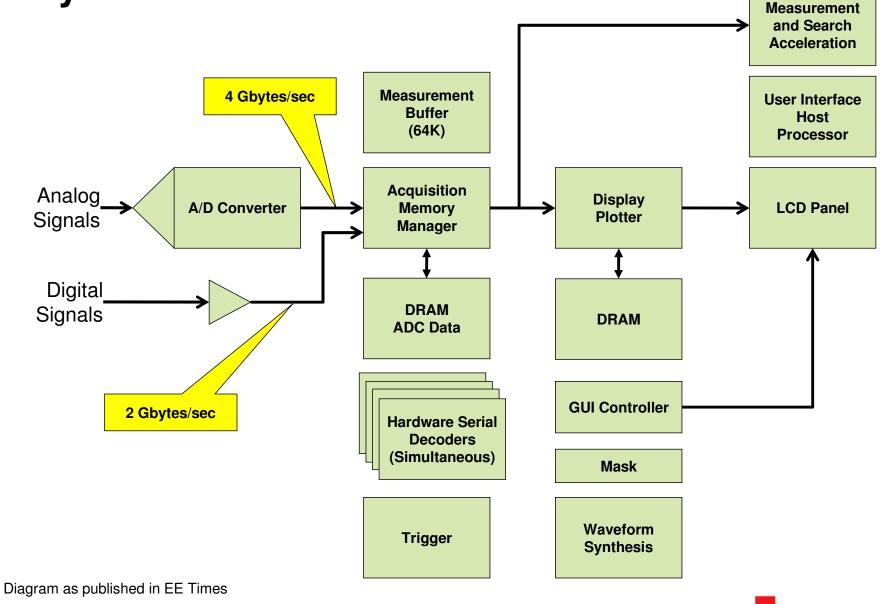

## Agilent InfiniiVision 2000/3000 DSO/MSO System Intent

## Agilent InfiniiVision 2000/3000 DSO/MSO System Intent

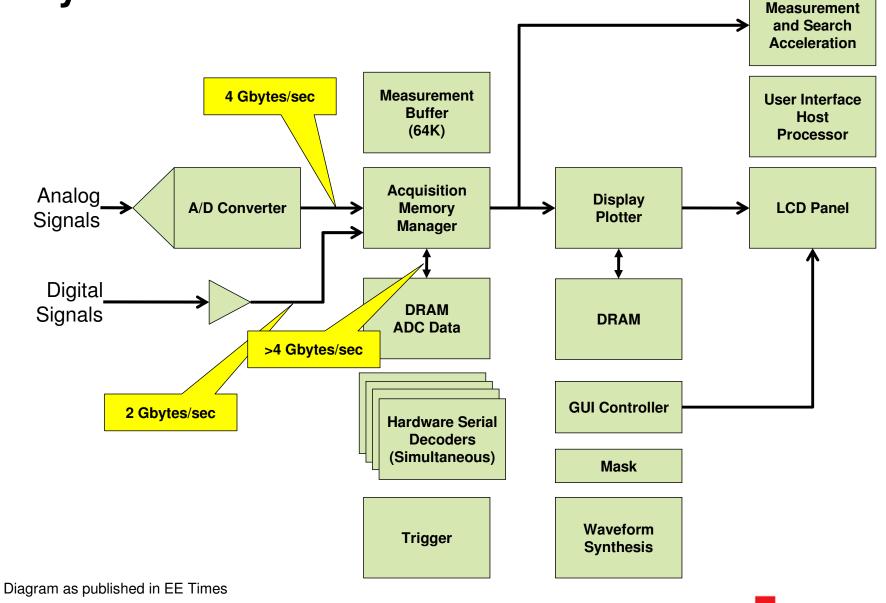

## Agilent InfiniiVision 2000/3000 DSO/MSO System Intent

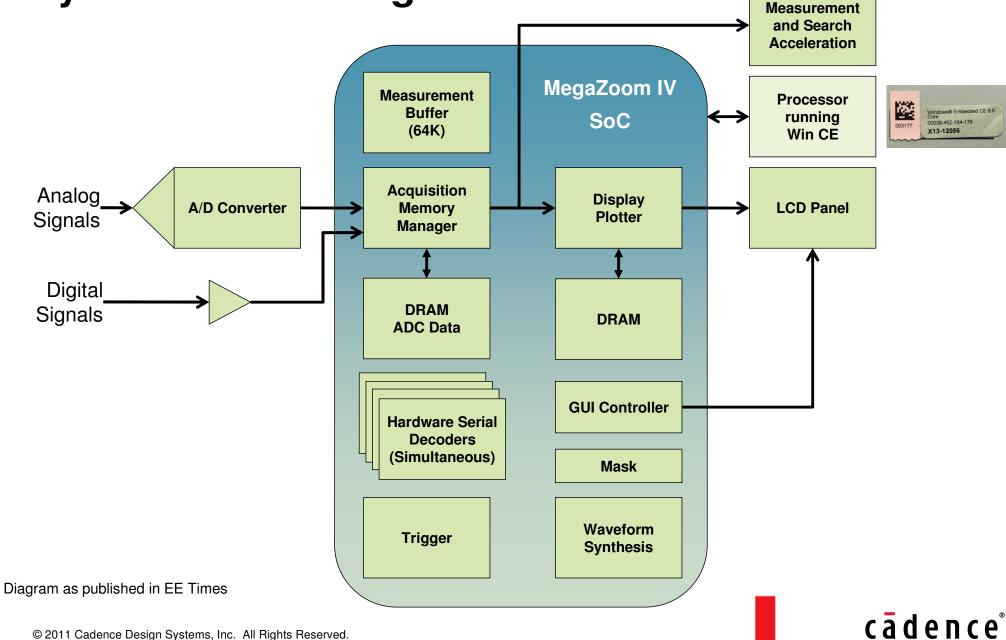

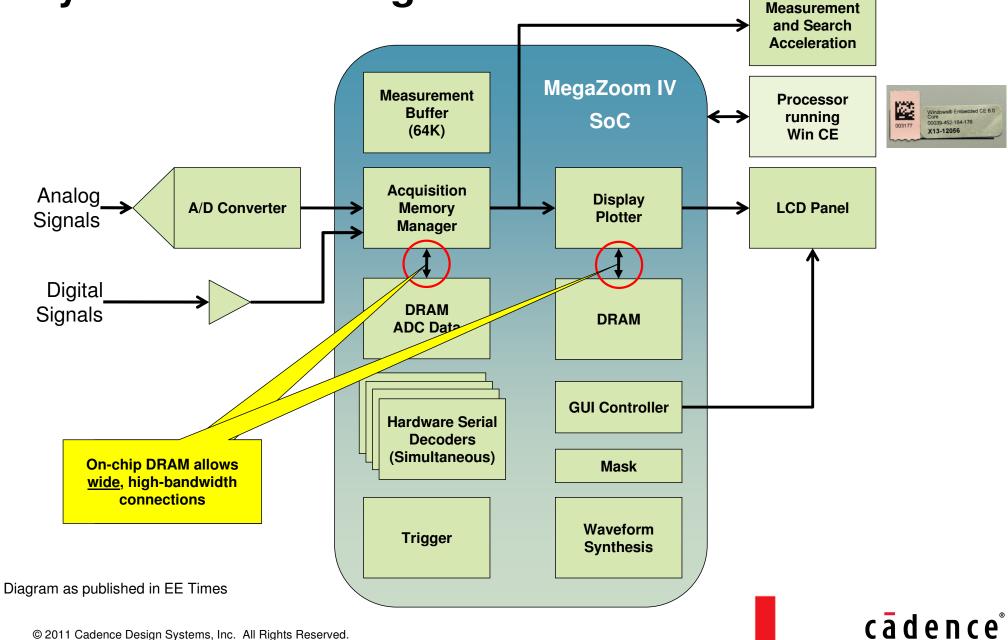

## Agilent InfiniiVision 2000/3000 DSO/MSO **System Partitioning**

## Agilent InfiniiVision 2000/3000 DSO/MSO System Partitioning

48

## Agilent MegaZoom IV SoC

Reproduced with Permission, Courtesy of Agilent Technologies, Inc.

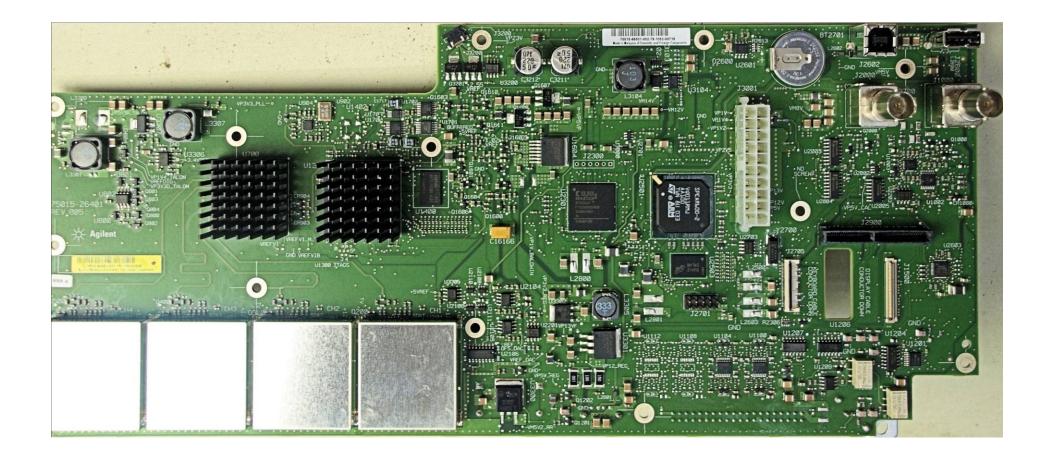

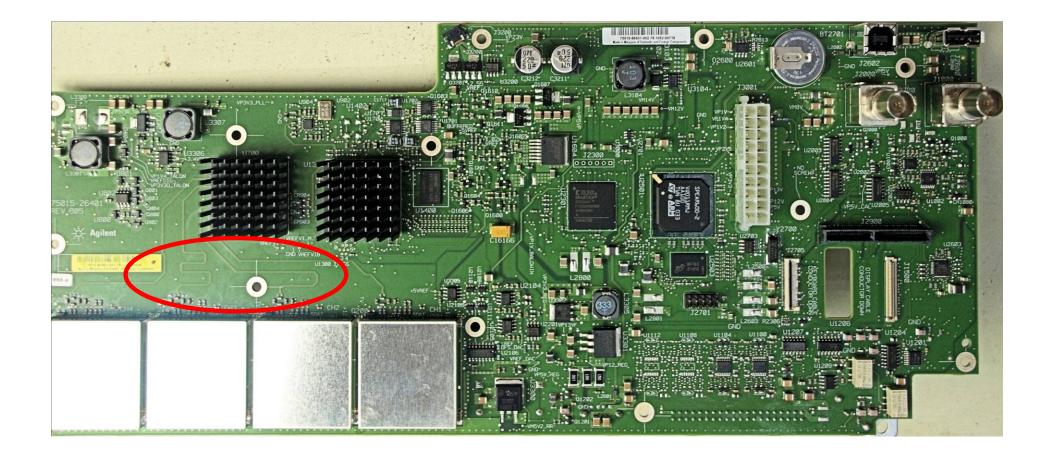

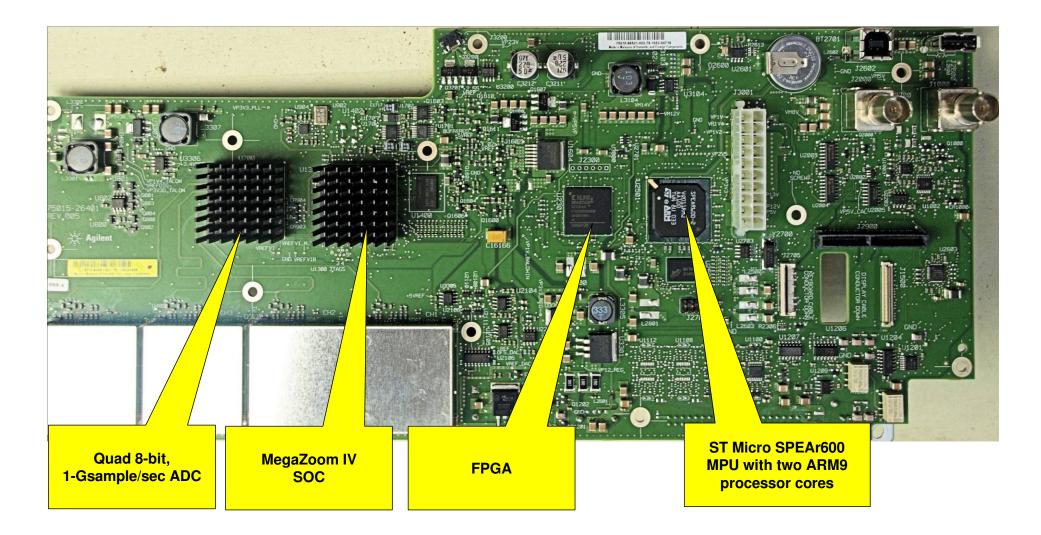

## Agilent InfiniiVision 2000 X-Series DSO Circuit Board

Image courtesy of David Jones, www.eevblog.com

## Agilent InfiniiVision 2000 X-Series DSO Circuit Board

Image courtesy of David Jones, www.eevblog.com

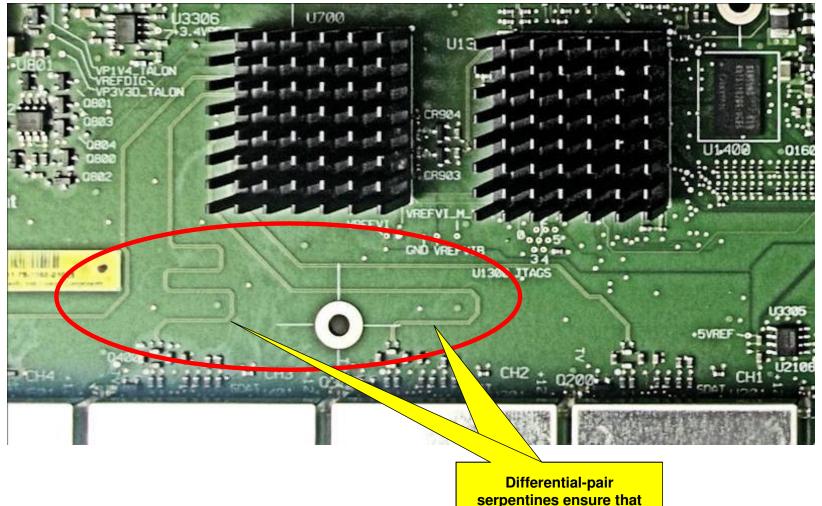

## **Detail: Board-Level Design Intent**

Image courtesy of David Jones, www.eevblog.com

Differential-pair serpentines ensure that all analog inputs reach the ADC simultaneously

#### 52 © 2011 Cadence Design Systems, Inc. All Rights Reserved.

# Agilent InfiniiVision 2000 X-Series DSO Circuit Board

Image courtesy of David Jones, www.eevblog.com

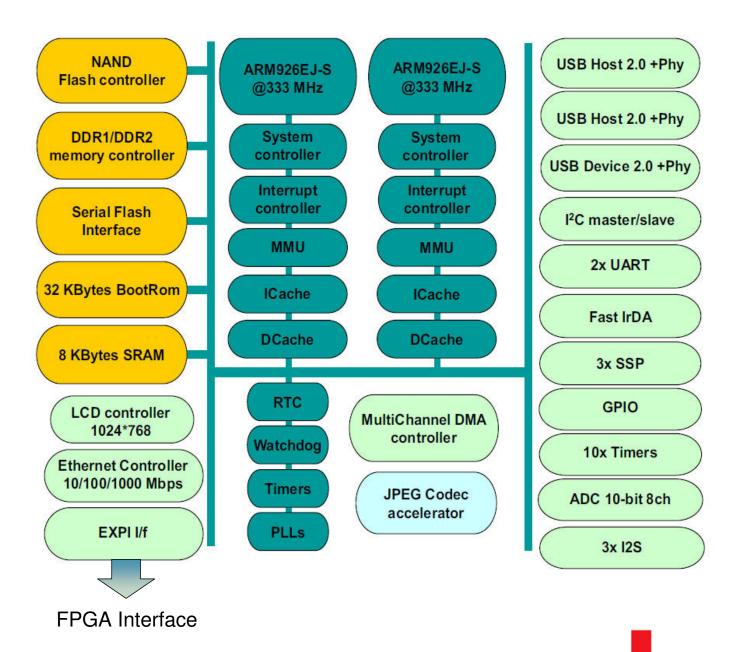

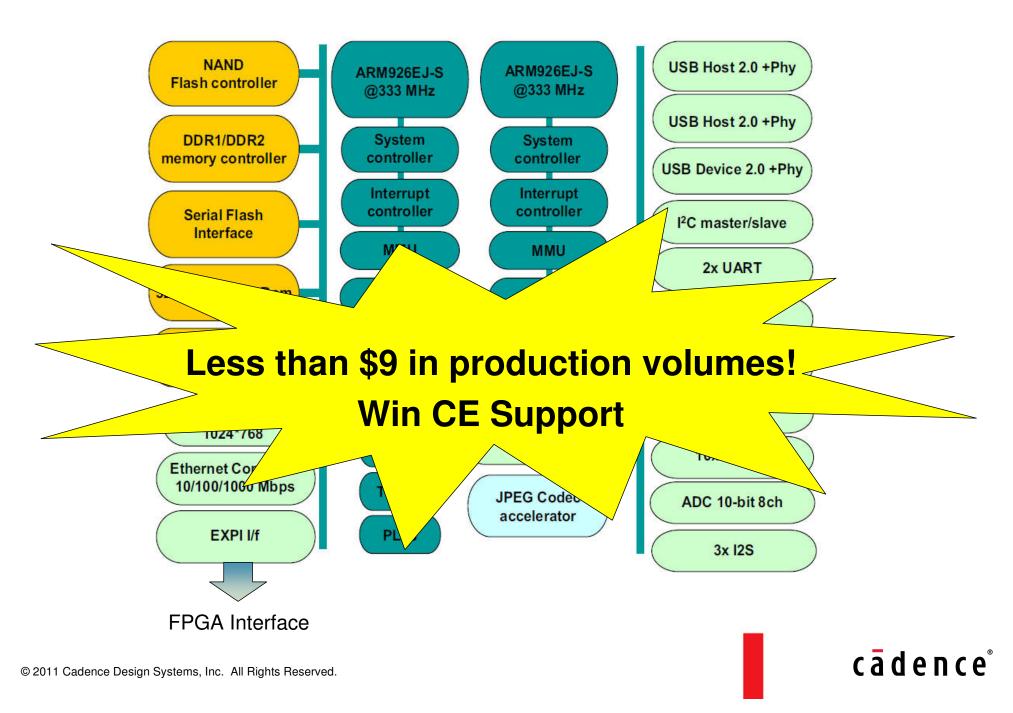

## ST Microelectronics SPEAr600 Block Diagram

54 © 2011 Cadence Design Systems, Inc. All Rights Reserved.

## Why use an ST Micro SPEAr600?

55

## **Three Key Pillars of EDA360**

cādence°

3x SSP GPIO

3x 12S

### **Questions and Answers**