# **MEMS and RF**

#### CAVENDISH KINETICS

### **Cong Khieu**

March 30<sup>th</sup>, 2010

, \_

**CONFIDENTIAL EDA paper**

Copyright © 2010 Cavendish Kinetics

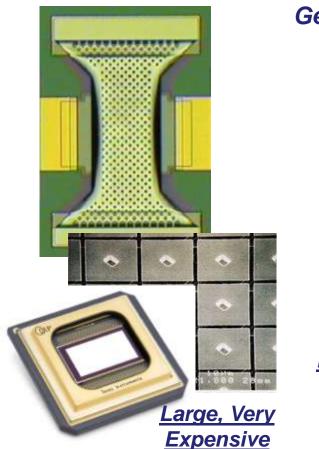

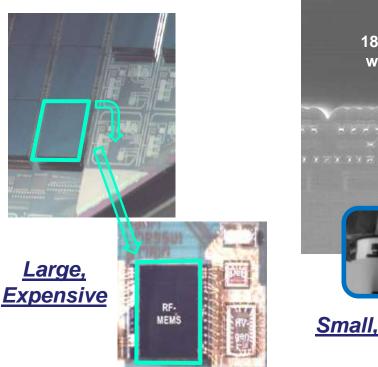

**MEMS Technology Trend**

#### Gen1: Build / Assemble

Gen2: Package in Package

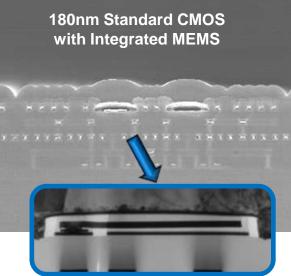

#### Gen3: Fully Integrated Cavendish 3<sup>rd</sup> Gen MEMS

<u>Small, Integrated, Low Cost</u> <u>No specialized</u> <u>tools/processes/materials</u>

#### **Cavendish MEMS encapsulation provides superior cost & reliability**

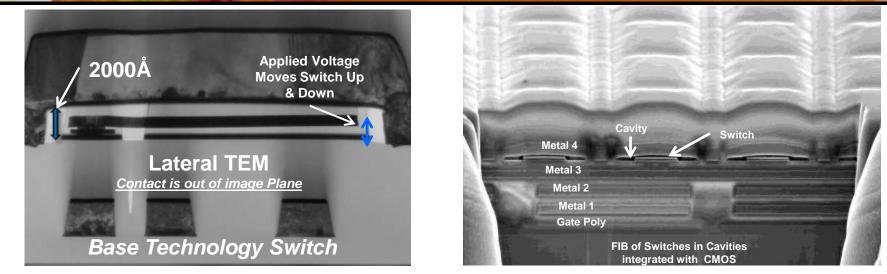

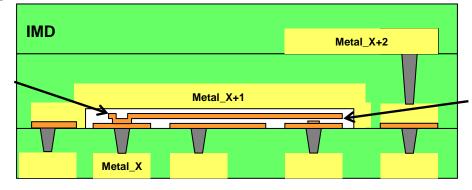

# **Core Technology: 3rd Gen MEMS**

### **MEMS Technology**

- Metal Based MEMS

- <u>Cantilevers</u>

- Metal Logic

- <u>NV memory</u>

- <u>Sensors</u>

- Digital Variable Capacitor

- <u>Robust MEMS Design</u>

- <u>Compact Routing</u>

- <u>Small Die Size</u>

### <u>Cavity</u>

- Package Free MEMS

- Non Contaminating

- <u>CMOS Processes</u>

- Planarized Interconnect

- Controlled Release Design

- Electrically Active Roof

- Roof: Metal or Dielectric

- Via Electrical Connections

Integrates into Standard Flow

#### CMOS Compatible Package Free MEMS, Using Standard Interconnect Technology

### **Cavendish Kinetics** Building MEMS Electronics

Mission: Enable our Customer to Deliver Breakthrough Products

- How: Enable integration of devices and sensors never before possible

- *Results:* Lower cost, lower power and smaller size

- *Means:* Standard semiconductor processing technology

- NanoMech<sup>™</sup> Technology Platform 3<sup>rd</sup> Generation MEMS

- Fully integrated into the process flow

- No unique equipment or materials or packaging

- Capability of Delivering Multiple Applications on the same IC

Enable our Customers to Deliver Enhanced Value Products with MEMS Technology

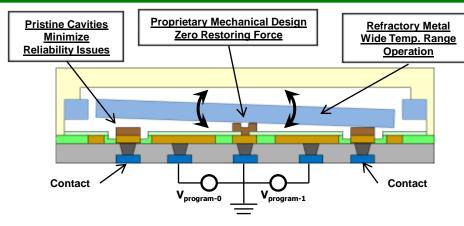

# **Cavendish Core Design Technology**

#### **Design Schematic**

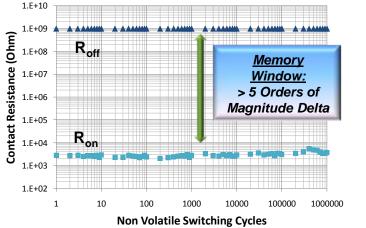

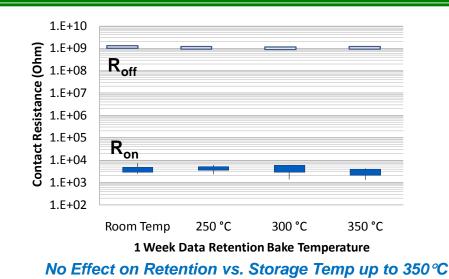

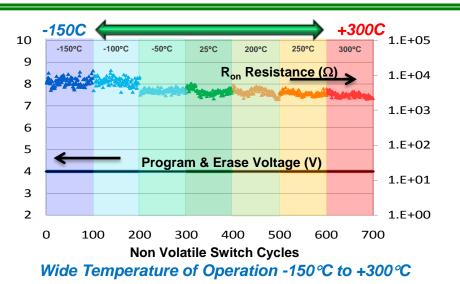

**NV Switch Performance Demonstrates Robustness of Technology**

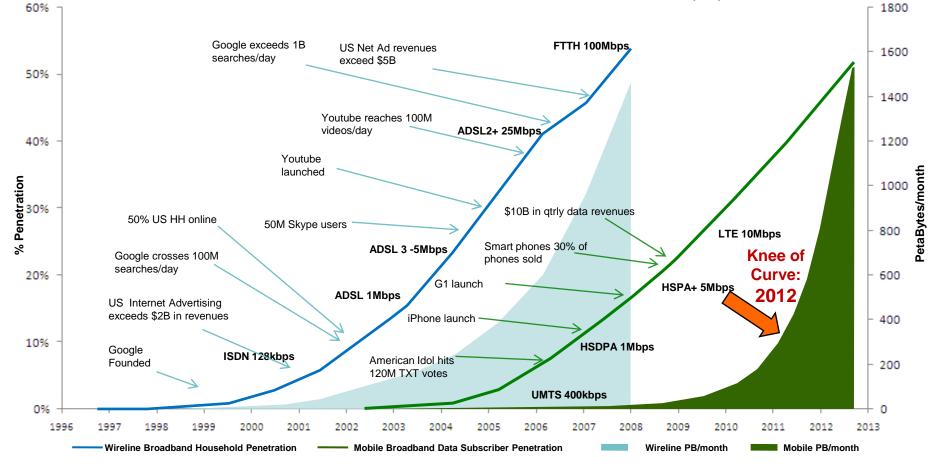

# Data Volume Forecast: Wireless Operators Have a Problem

#### Broadband Penetration and Traffic for Wireline and Mobile (US)

#### Source: Chetan Sharma Consulting

Wireless devices will need better performance = Opportunity

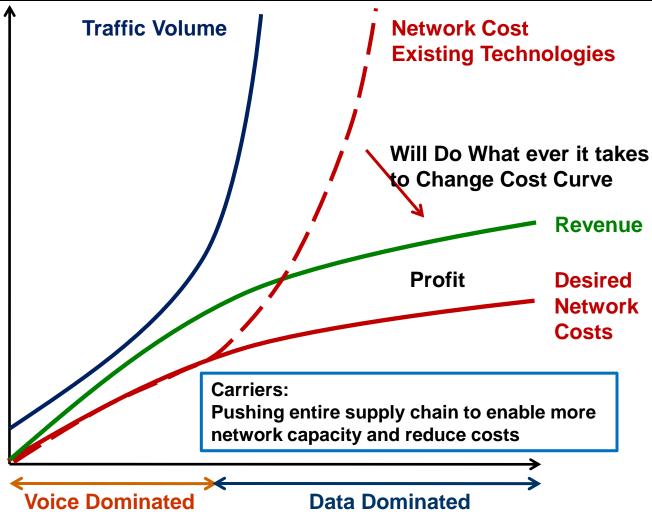

## **Carrier Economics Dilemma...**

Source: Nokia-Siemens and AT&T

### Adding Bands, Adding Complexity, Adding Requirements

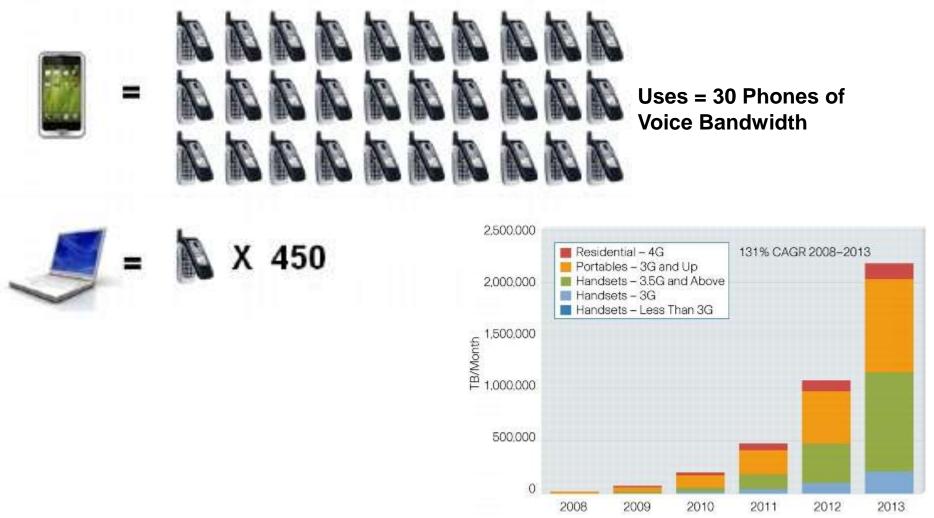

# What is the Reason and Breakdown...

#### Data Source: Cisco Systems White Paper Feb 2009

#### Data is swamping the networks as smart devices are adopted...

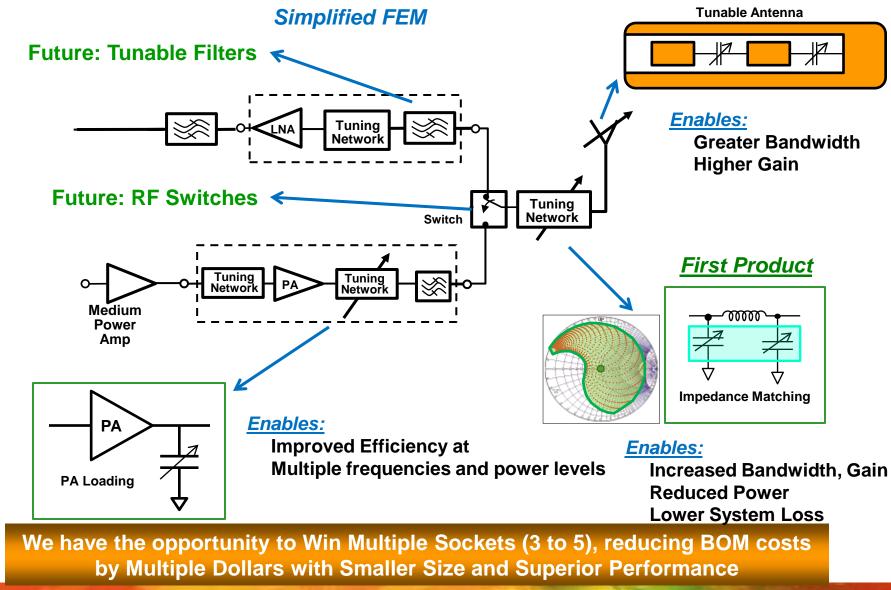

# **Areas for Applications in FEM**

**Impedance Matching & Capacitance Loading**

**CONFIDENTIAL EDA paper**

Copyright © 2010 Cavendish Kinetics

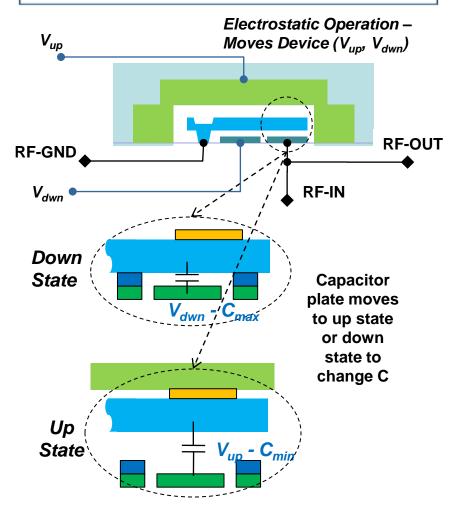

# Nanomech™ Based Variable Capacitor Device

### **CROSS-SECTION VIEW – Unit Cell**

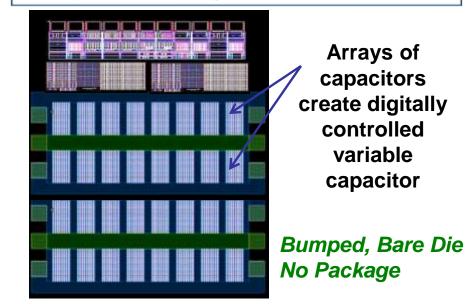

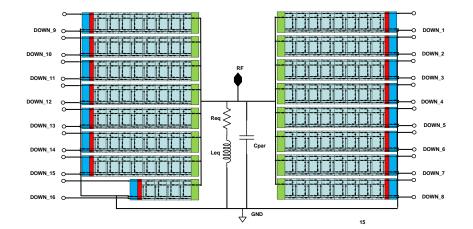

#### Array of Cells – Digital Variable Capacitor

#### Variable Capacitor:

- Total capacitance is the sum of all the caps

- Each Capacitor unit individually controlled to be either Up or Down

- Result: High resolution with linear response

#### Array of Capacitance Switches operated as one Variable Capacitor

## **Cavendish Kinetics**

### **Measured Data**

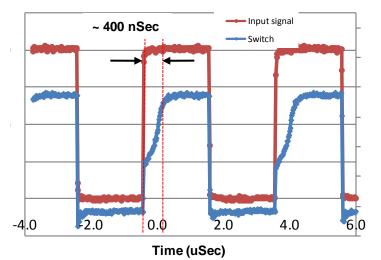

#### **Capacitor Array Switching Speed**

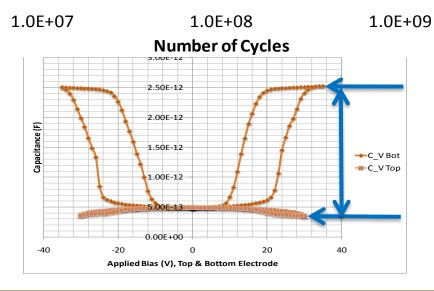

C<sub>max</sub> & C<sub>MIN</sub> Cycling to 1 Billion Cycles

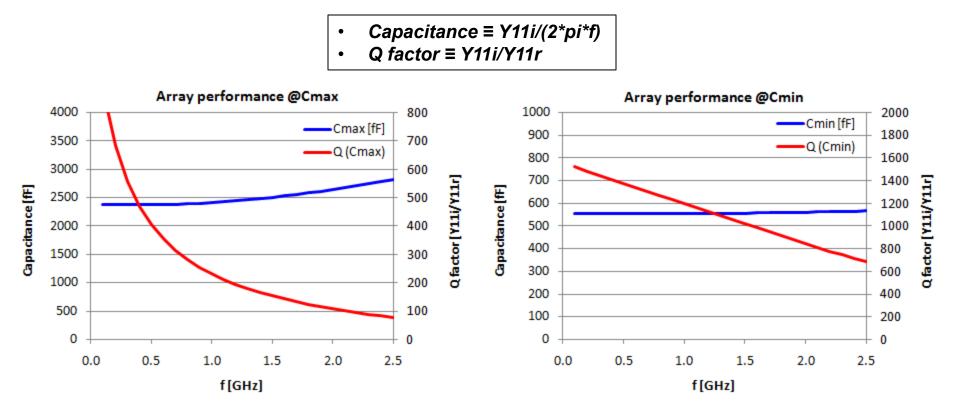

### Array of "Small Switches" Enables Reliable Fast Variable Capacitor Array

- <u>Design example targets</u>:

- 5:1 high hot-switch MEMS design (45Vrms)

- Q = 100 at 2GHz

- Performance estimate includes effect of bumps and copper traces on RF board (total series inductance ~ 130pH including copper trace on RF board)

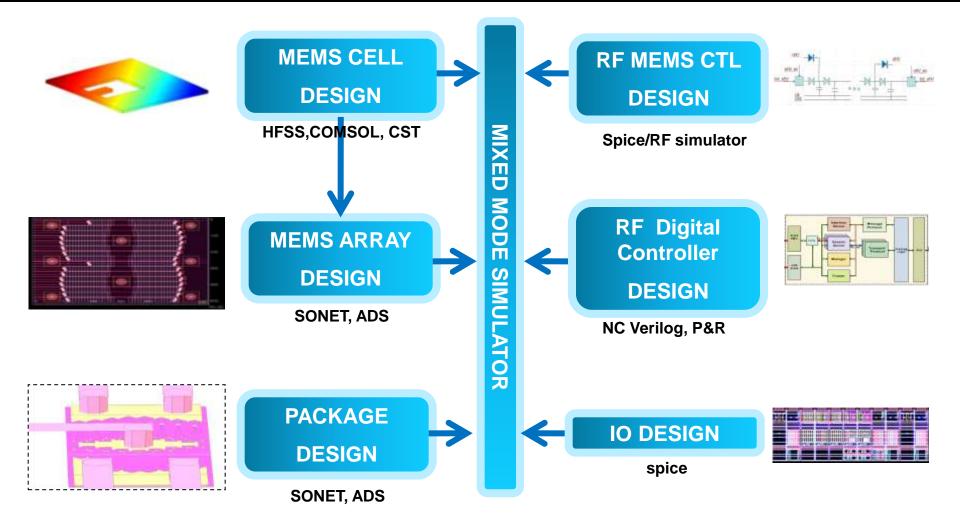

# **DVC CAD DESIGN FLOW**

#### Many different tools have to work together

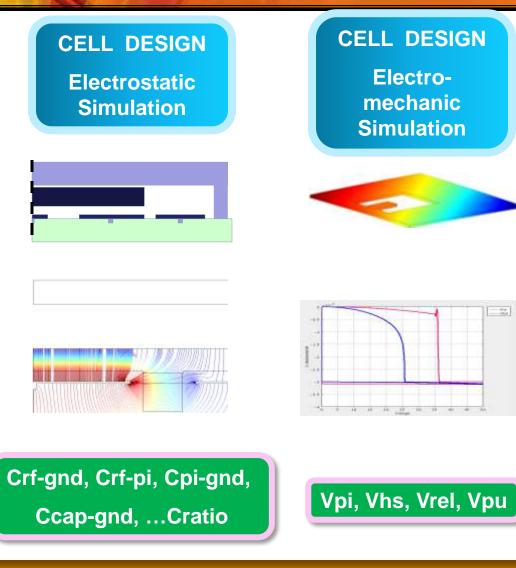

# **DVC CAD Tool at Cell Level**

### **Cell design requires different simulators**

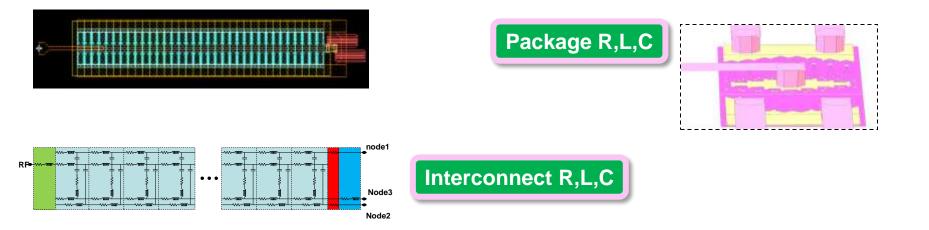

## **DVC CAD Tool at Array/Chip/Package levels**

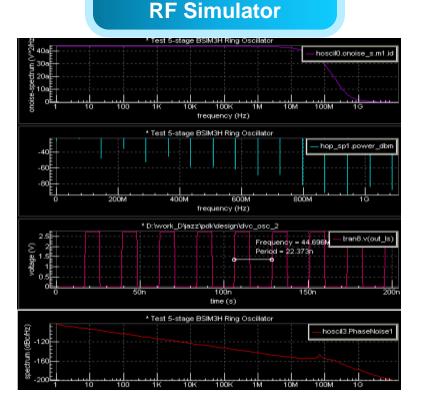

# **DVC Circuit/RF simulators**

### Charge Pump DESIGN

#### Pnoise, onoise, harmonics

### Charge Pump DESIGN

#### **Circuit Simulator**

### posHV, negHV Power, timing, S-paramaters

### Summary

- RF front end limits the cell phone scalability to many bands

- MEMS provide solutions for:

- Antenna tunable matching network, or band select

- High power handling, Very linear, no harmonics, low cost

## MEMS + CMOS CAD Flow requires:

- Many different CAD tools and sometimes manual edits are required

- There are room for CAD Design Flow Improvement