## Low Power & Impact On Verification

Prapanna Tiwari

#### **Low Power Techniques**

#### Traditional Techniques

20110h2A2

Predictable Success

#### Advanced Techniques

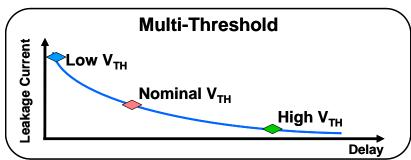

| Voltage Control Is Key                |                                      |                 |                                                                            |                    |

|---------------------------------------|--------------------------------------|-----------------|----------------------------------------------------------------------------|--------------------|

| Design Techniques Impact Verification |                                      |                 |                                                                            |                    |

| MTCMOS power<br>gating (shut down)    | Power gating with<br>State Retention | Low-VDD Standby | Dynamic or Adaptive<br>Voltage Frequency Scaling<br>(DVS, DVFS, AVS, AVFS) | Multi-Voltage (MV) |

|                                       |                                      |                 |                                                                            |                    |

## Verification Impact

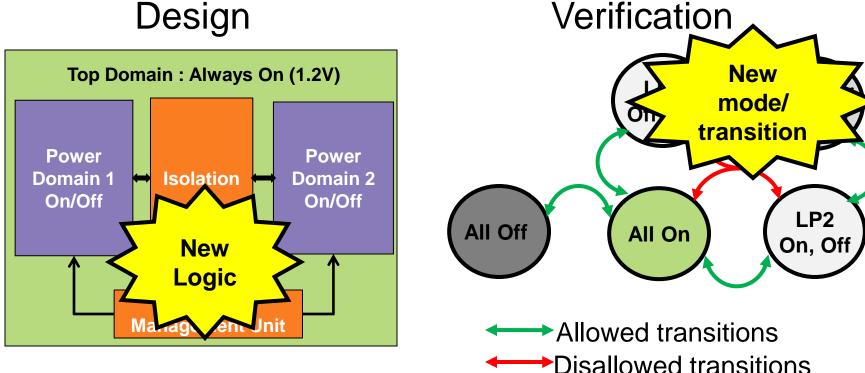

#### Design

#### New logic and semantic to be checked and simulated without being present in RTL!!!

## Low Power Introduces New Logic

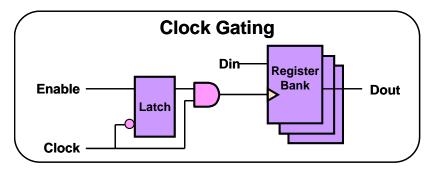

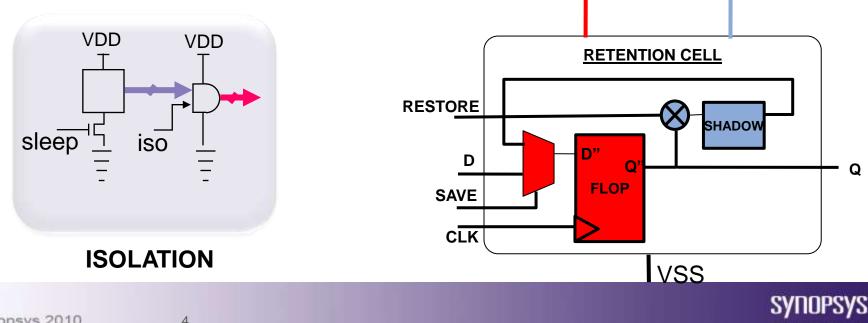

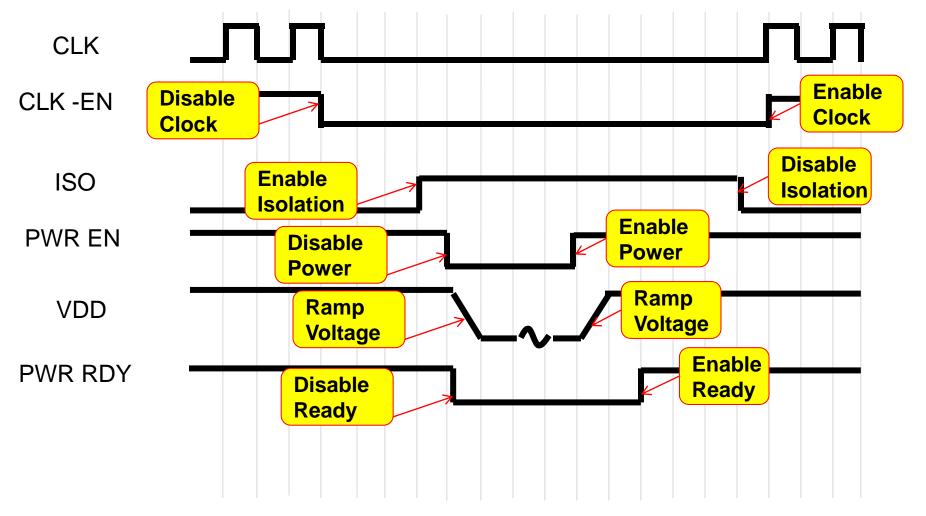

- Power management introduces logic for Isolation, Retention

and Level-shifter (defined in UPF)

- This is behavioral code that doesn't exist in RTL

- It must account for secondary effects in addition to the primary role.

- E.g. Isolation is dependent on iso-enable and it's driving rail

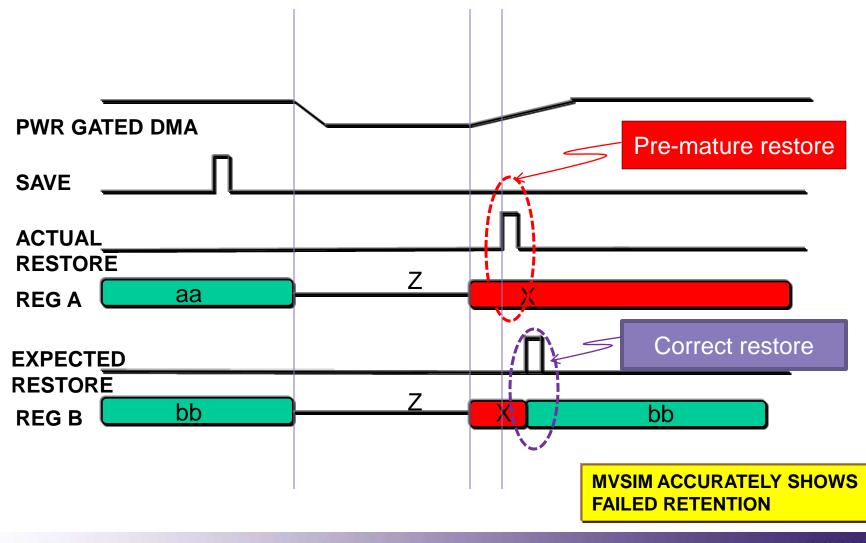

- E.g. Retention is dependent on save/restore/ret-rail/assertvalues/voltage-ramp time

VDD

VRET

Predictable Success

# Low Power Introduces New Events/Protocol

## Accuracy Of Simulation A key concern for LP verification

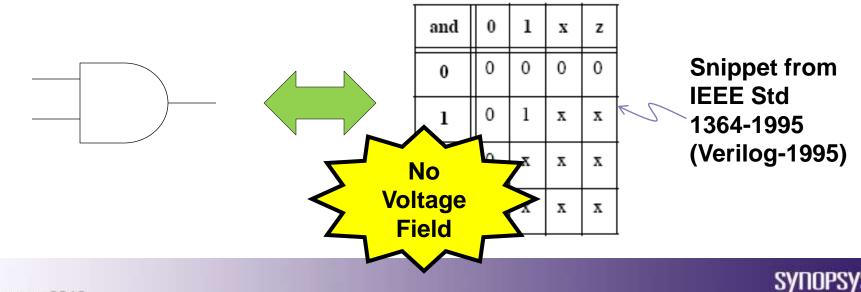

- Non-LP behavior of logic is defined in HDL (verilog, VHDL, SV) manuals

- You do not loose sleep over whether simulator is simulating the AND gate accurately!!

- HDL LRM only defines association between logic pins

- Does NOT consider voltage effects

Predictable Success

## Accuracy Of Simulation A key concern for LP verification

- Voltage variation NOT part of LRM

- Accuracy of LP simulations is now a concern

#### **Power Management Verification –**

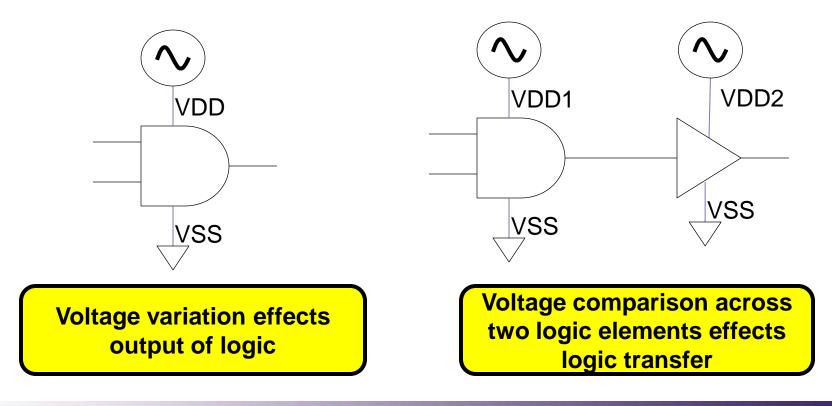

Accurate Interpretation of Voltages

#### nature of voltage

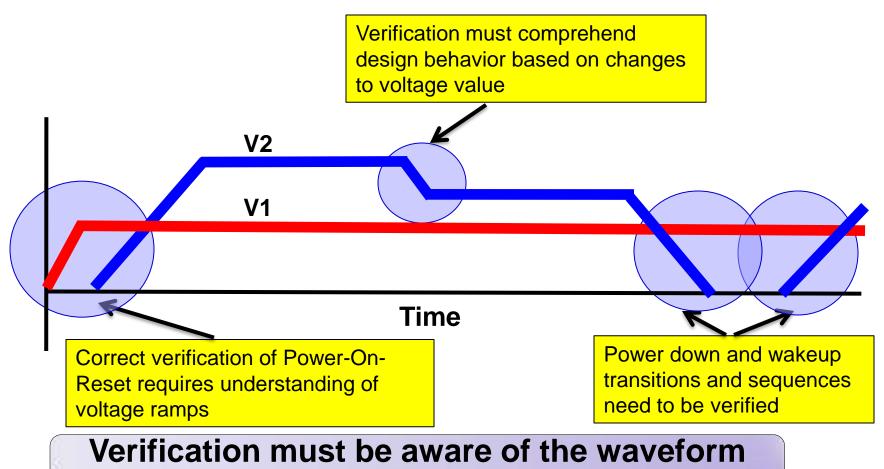

#### **Voltage Ramps Catch Corner Cases**

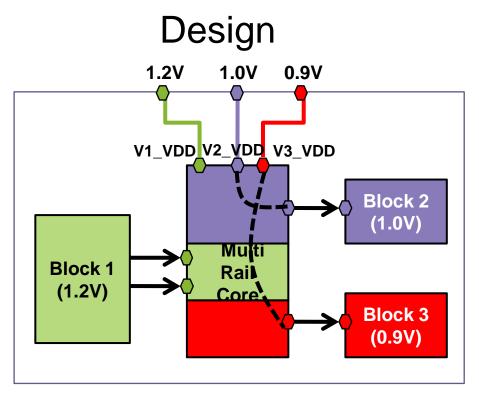

#### **To Make Matters Worse** *Multi-Rail Cores*

#### Verification

- •Multi-rail cores are connected to different supply voltages

- Logic pins connect to other domains at different voltages

## Verification must associate logic pins and internal power partitions to with supply rails

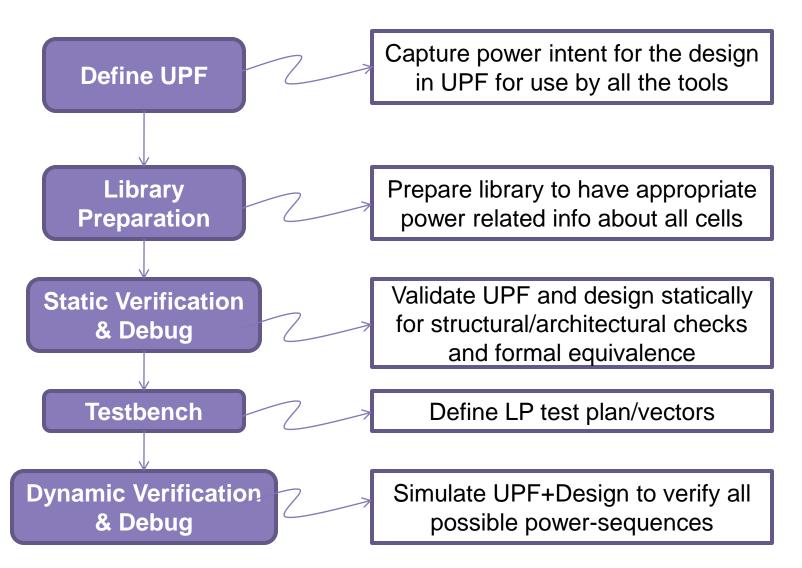

## **Stages In Verification**

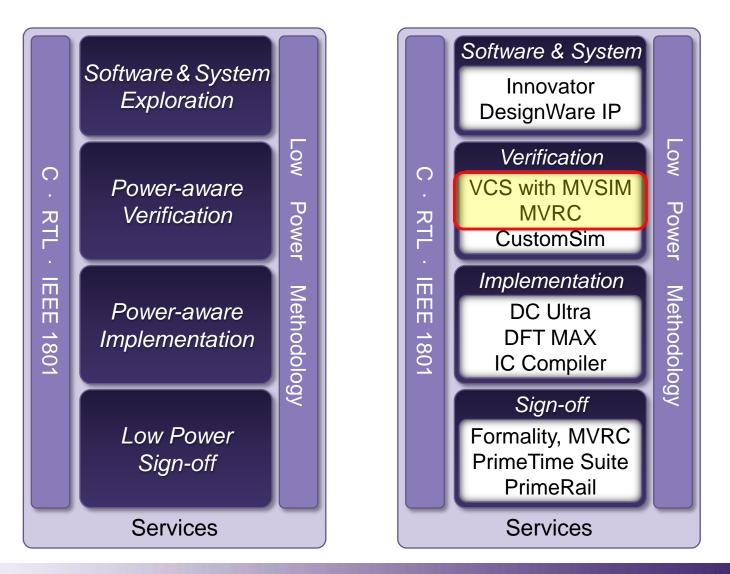

## **Eclypse Low Power Solution**

## Summary

- A combination of static and dynamic checks is required for complete low-power verification

- Accuracy is a key concern for low-power verification

- Verification engineers MUST focus on accuracy when defining a solution

- A complete & scalable low-power verification methodology is necessary to ensure success