### EDA = Electronic Design Automation Are you kidding?

EDP 2010

Andreas Kuehlmann

R E S E A R C H L A B O R A T O R I E S

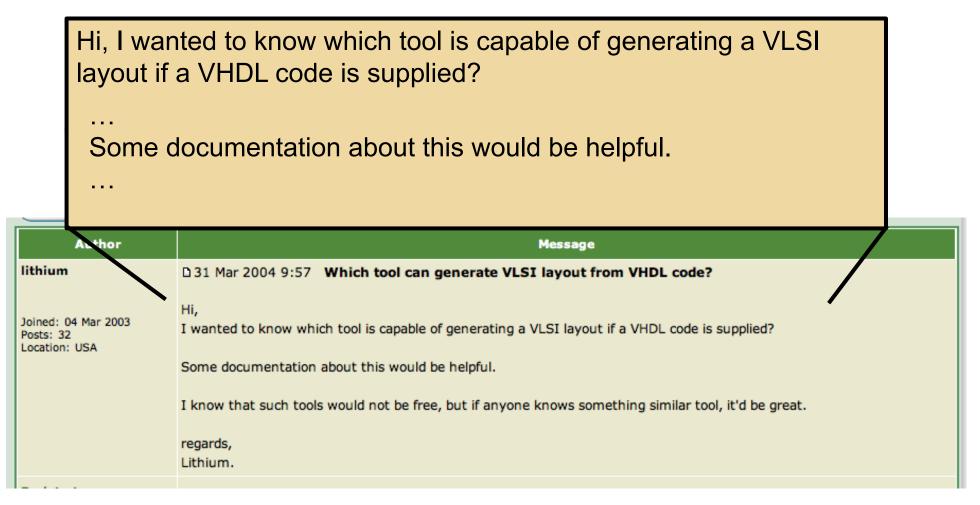

#### EDA is now more than 30 years old....

#### ... a response came within a few hours

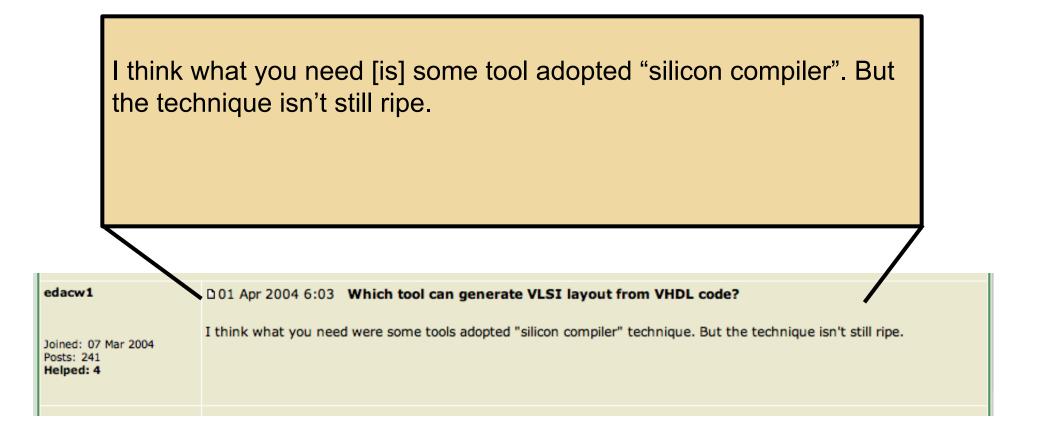

#### ... so, what happened to the "Silicon Compiler"?

Carver A. Mead and George Lewicki, "Electronics" magazine 1982:

"Silicon compilers and foundries will usher in user-designed VLSI"

| Anatomy of a<br>Silicon Compile            |

|--------------------------------------------|

| <sup>dited by</sup><br>Robert W. Brodersen |

|                                            |

|                                            |

| /* | Read instruction                 | */                                                                        |

|----|----------------------------------|---------------------------------------------------------------------------|

|    |                                  |                                                                           |

| /* | Execute instruction              | •/                                                                        |

|    | String at bit 0,<br>length 6 bit | */                                                                        |

|    | Simple opcodes                   | */<br>*/                                                                  |

|    |                                  |                                                                           |

|    |                                  |                                                                           |

|    |                                  |                                                                           |

| /* | Undefined opcodes                | */                                                                        |

|    |                                  | */<br>*/                                                                  |

|    |                                  |                                                                           |

|    |                                  |                                                                           |

|    |                                  |                                                                           |

|    | /*<br>/*<br>/*<br>/*             | <pre>/* Read instruction /* Execute instruction /* String at bit 0,</pre> |

#### References

1.

- R.K. Brayton, N.L. Brenner, C.L. Chen, G. DeMicheli, C.T. McMullen and R.H.J.M. Otten. The YORKTOWN Silicon Compiler. *1985 ISCAS Proceedings*, pages 391-394, Kyoto, June 1985.

- R.K. Brayton, R. Camposano, G. DeMicheli, R.H.J.M. Otten and J.T.J. van Eijndhoven. The Yorktown Silicon Compiler System. in D. Gajski (Editor), editor, Silicon Compilation, Addison-Wesley, 1988. (also IBM Research Report RC 12500, Mathematics, Yorktown Heights, December 1986).

#### ... another prediction of the "Silicon Compiler"?

John Gray, Irene Buchanan, Peter Robertson, DAC 1982:

"...It allows the engineer to design for performance, wirability and testability by manipulating a textual description of a design. The principle features of this are a high-level language for design description, completely automatic layout, and an integrated simulator. The total package can be referred to as a silicon compiler..."

#### ... another prediction of the "Silicon Compiler"?

John Gray, Irene Buchanan, Peter Robertson, DAC 1982:

"...It allows the engineer to design for performance, wirability and testability by manipulating *a textual description* of a design. The principle features of this are *a high-level language* for design description, completely automatic layout, and an integrated simulator. The total package can be referred to as a silicon compiler..."

#### They got it almost right...

... except that

### "a high-level language"

should have meant

### "a pile of files with many languages"

VHDL, Verilog, Spice, Systemverilog, C, C++, SystemC, BlueSpec, UML, ...

#### and then the other "beauties" such as

tcl, grep, awk, sed, perl, sh, csh, ksh, bash, ...

#### What do I want, as a designer?

### Tools that...

- ... produce "optimal" results for me.

- ... results that are predictable and repeatable.

- ... results that are incremental.

- ... know what results I will like and takes it into account.

- ... I can micromanage when needed because I am an Engineer!

#### What do we give them?

#### Many Tools that...

- ... utilize instable algorithms

- ... have many variations and thousands of options

- ... and are buggy

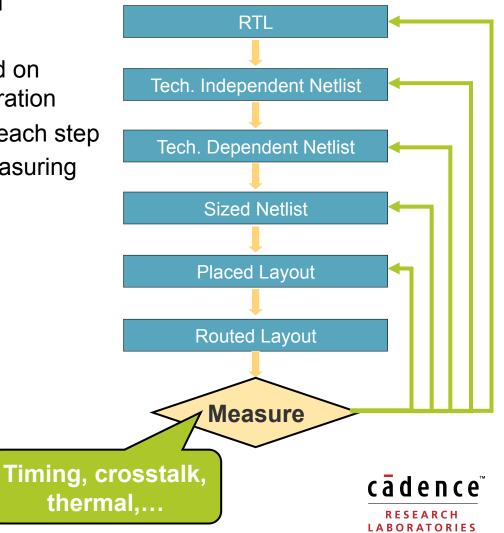

#### **Today's Design Flows are Split into many Steps**

- There is **no** monolithic optimization approach to the RTL-to-GDSII synthesis problem

- Traditional approaches based on horizontal flow slicing and iteration

- Simplified models applied at each step

- Optimization achieved by measuring and readjusting weights

- There is **no** guarantee of convergence!

- There is **no** guarantee of incrementality

- Result:

- Extremely instable flows

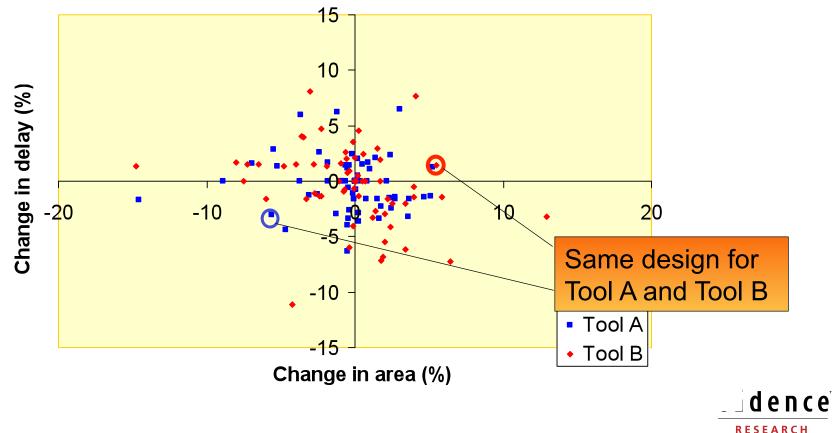

## Example: Instability of Logic Synthesis

- Logic synthesis experiment with public benchmarks (IWLS 2005)

- Original RTL synthesized versus identical RTL with names mangled

RESEARCH LABORATORIES

## Why is it like this – three reasons?

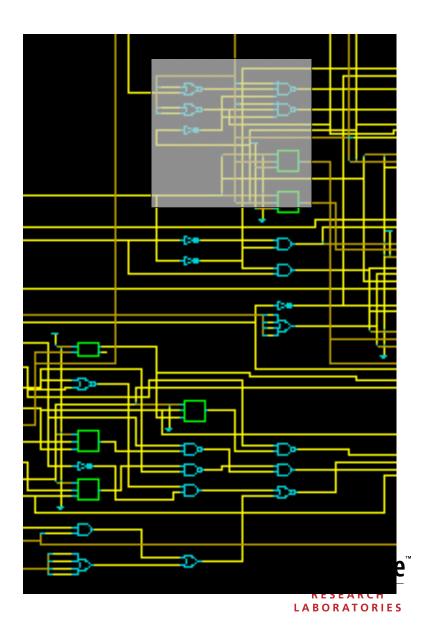

- Reason # 1: Windowing

- Many synthesis algorithms don't scale and need to be applied to a small window. The window is being shifted over the design which make the results order dependent which can dramatically change with a small change of the design.

## Why is it like this – three reasons?

- Reason # 2: Decision Threshold

- The complexity of many synthesis algorithm is controlled by resource thresholds after which a transformation attempt is aborted. A small change of the design can cause a jump over the threshold spawning completely different results.

```

int search(unsigned max_backtracks)

{

for(i = 0; i < max_backtracks; i++) {

success = try_something(i);

if(success) return 1;

}

return 0;

}</pre>

```

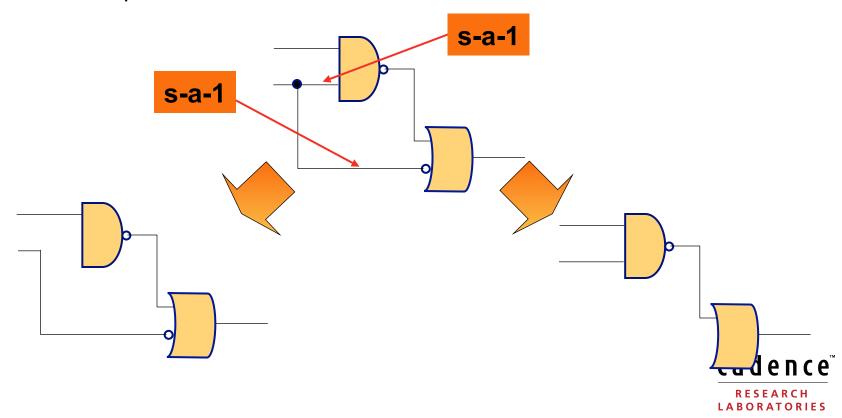

## Why is it like this – three reasons?

- Reason # 3: Order of transformations

- Certain transformation on single nets are mutually exclusive.

Depending on the order in which they are applied a different outcome can be produced.

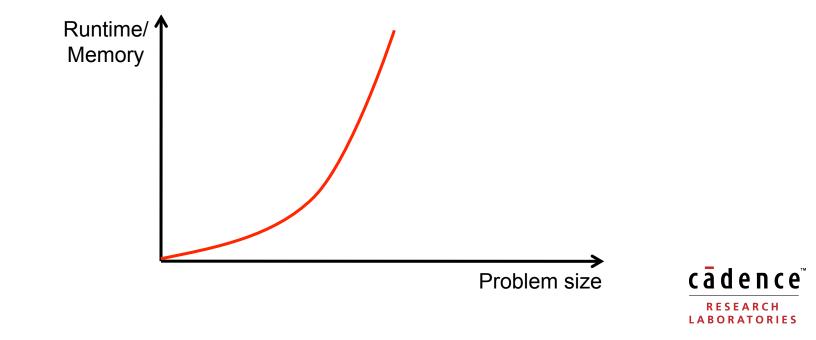

## Most algorithms are computationally hard: NP-hard or worse

Logic optimization, technology mapping, placement, routing, verification, ...

#### How do we solve the problem?

#### Ingredient #1: Let's add another option to the tool!

... setRouteMode -routemagictrick 34876 ...

- Can solve any problem such as

- "I know a better route"

- Number of options:

O(n\*m\*k)

- n number of designs

- m number designers

- k number of features to be controlled

#### How do we solve the problem?

```

Ingredient #2:

If you don't like what the tool does ...

```

... why don't you program it yourself!

```

...

Source my_magic_script.tcl

...

```

Very clever!

- Outsources programming from the tool provider to its customer

- Gives the illusion of freedom

- Makes tool sticky

#### How do we solve the problem?

Ingredient #3: We ship a neural network with the tool that helps you navigate through the maze

Also called:

## **Application Engineer**

All together it makes...

## SiliconCompiler 2.0

# Thank you!