# Data Management Challenges of CPU Design

Kiron Pai Intel Corporation

Feb 25, 2010 EDP 2010

#### Agenda

- Introduction

- Problem Scope

- Silicon Stepping Methodology

- Requirements

- Reduce, Reuse and Recycle

- Workflows

- Conclusion

- What did we accomplish?

- Q&A

# Introduction

#### **Problem Scope**

- Multiple silicon steppings and incremental improvements

- Design Cost and Performance

- Multiple product configurations and design reuse

- Time to Market for multiple customer segments

- Concurrent development of different product configurations

- Design Productivity

- Flexibility: adapt to changing requirements

- Market needs move during design and production cycle

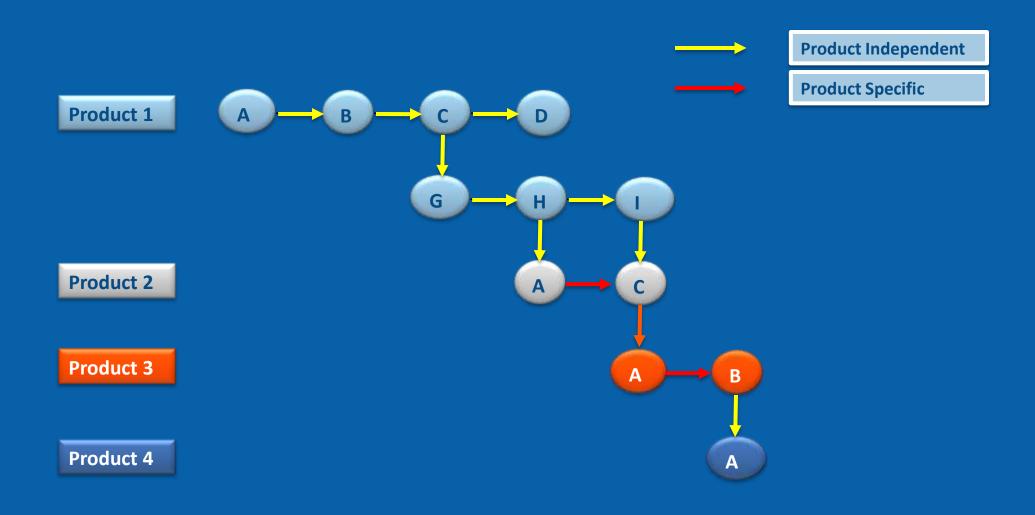

### Past Project – A look back

Started as a 1 product configuration

By the end, there were 4 different product configurations for 3 different market segments

- Challenges included

- Efficient design reuse across

- Product configurations

- Steppings

- Multi-geo development sites: a fact of life now...

Need to understand and prevent Chaos

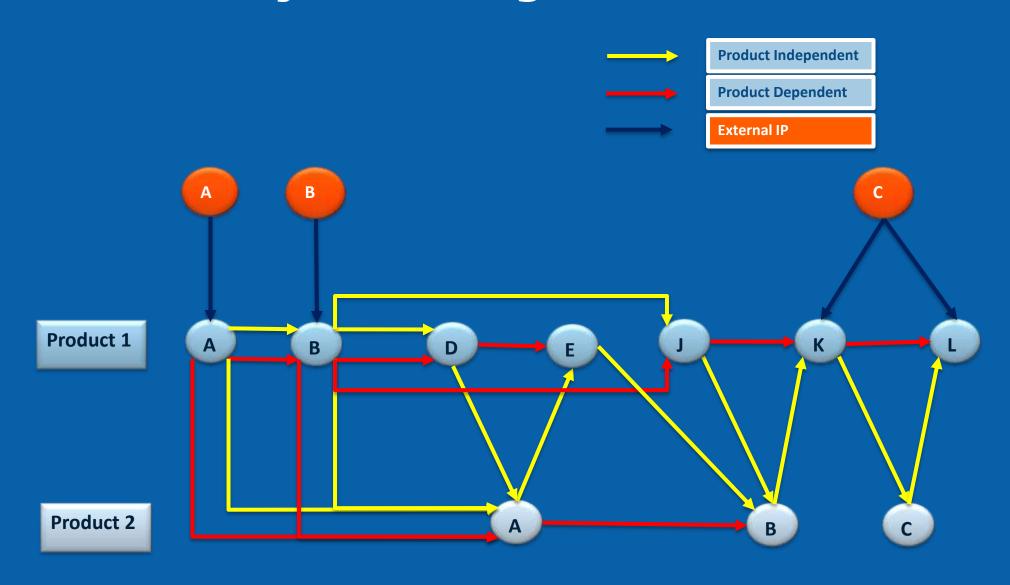

# Past Project - Design Inheritance

#### Past Project - Stepping Methodology

Data inheritance from reference steppings

- Product independent v/s product specific inheritance

- Inheritance maintained using links

- Edits enabled by making copies

Reused design data that didn't change across steppings and product configurations

Multiple sites maintained using edit access controls and nightly synch ups

Reigned in Chaos to bring Stability

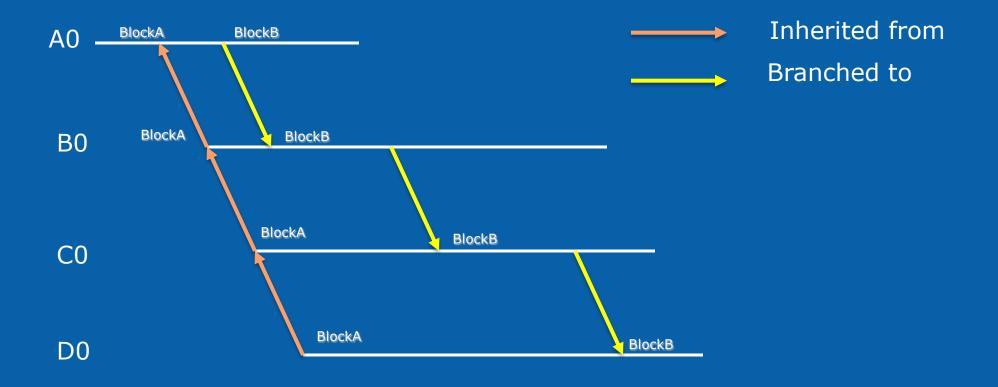

#### **Current Project - Requirements**

#### Support for

- Concurrent development

- Reuse of data across steppings

- Multi sites, multi steppings, multi products

- Reuse at the smallest manageable granularity

### **Current Project - The Philosophy**

Leverage reference project as long as possible

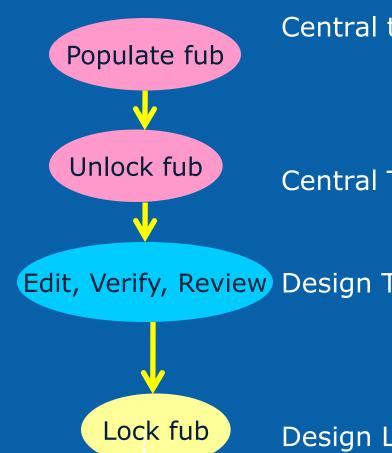

#### **A0 Workflow**

Central team: Populate data into A0 libs

Central Team: Unlock libs for edit

Edit, Verify, Review Design Team: Enabled to checkout, checkin

Design Leads: Lock fub down in preparation of closure leading to lockdown

FUB = Functional Unit Block, anywhere from 10K to 500K devices

#### Minor edits Stepping Workflow

Integration team: Unlock fub for edits

Design Team: Enabled to checkout, checkin

Integration Team: Lock down fub

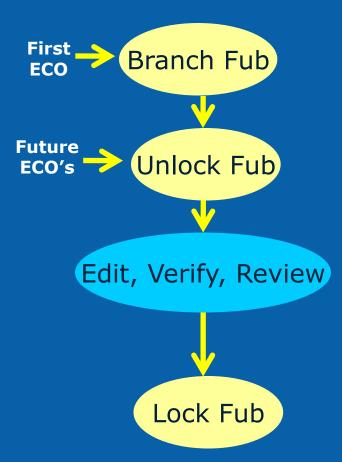

#### **New Stepping Workflow**

Design Leads: For first ECO in new stepping, branch databases and unlock for edits

Design Leads: Unlock block for future edits for blocks that have been previously branched, edited and locked.

Design Team: Enabled to checkout, checkin

Design Leads: Lock blocks down in preparation of closure leading to lockdown

# Conclusion

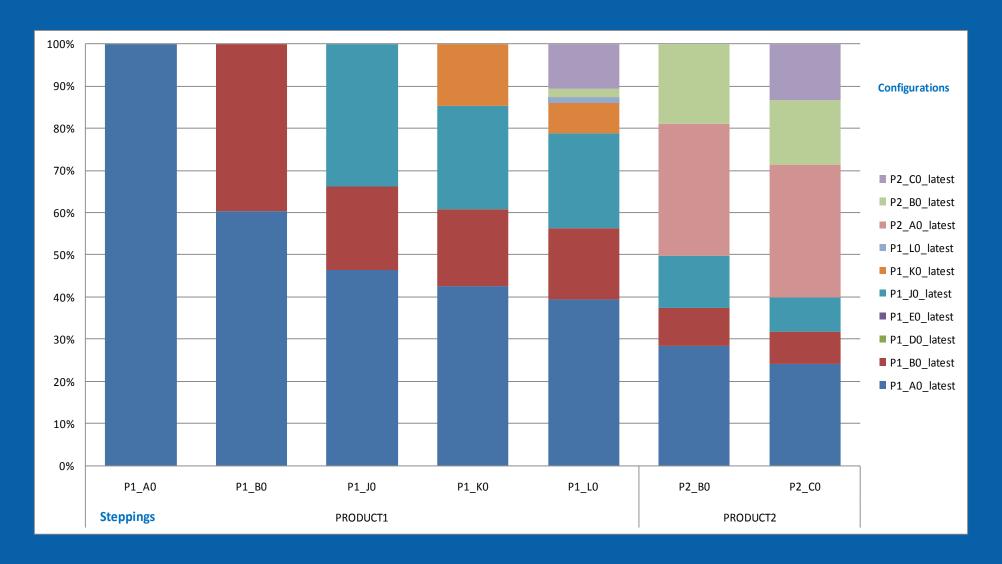

# **Recent Project - Design Inheritance**

#### Recent Project - Reuse across steppings

# Q&A