# Electronic Processes Workshop Presentation

April 9, 2009, Monterey, California

Arteris Confidential — April 9, 2009

# Why is it Time to Get off The Bus? (at the top level)

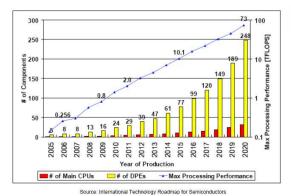

- SoC Complexity Increasing

- More software applications on a single device

- Number of IP blocks on Chip increasing

- Heterogeneous IP communication standards

- Creating SoC Delivery Bottlenecks

- Access to data (Memory bandwidth)

- IP block interconnect

- SoC design verification

- Software development of final application

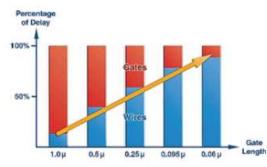

- Too many physical wires in the design

- Impacting Time to Market (and Money)

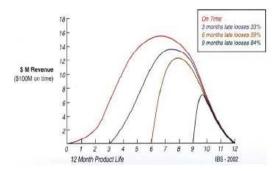

- Missing a market window causes profit losses

- Being quicker to market applies to all SoCs

#### Who is Hitting These Problems First? The Mobility Eco-System

- Leading SC, device, portal and wireless companies will design and deploy 1,000,000,000 complex SoCs to enhance capabilities and differentiation

- A race to built a true and connected personal computer

3 Arteris Confidential April 9, 2009

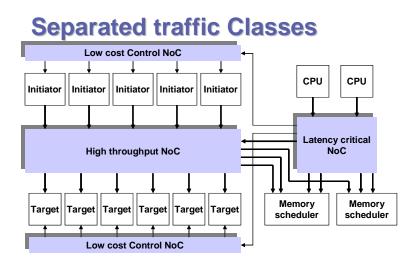

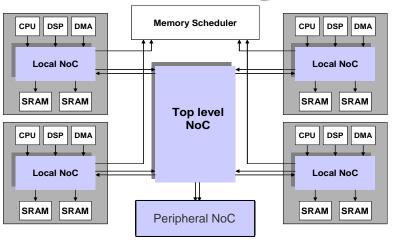

### What is the Answer? A Unified NoC Architecture

#### **Clustered design**

- Top level interconnect:

- Block level interconnect:

- Multiple Dies in SIP:

- Peripheral interconnect:

Scalability, Power, Performance Latency, IP Flexibility, Fast Cycles Speed, Latency, Simple Software Wire conservation, area

Arteris Confidential April 9, 2009

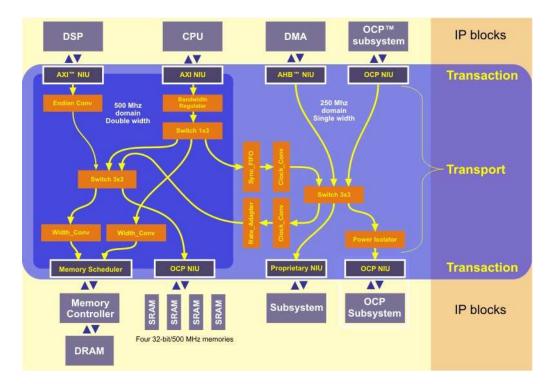

# **NoC Technology Keeps Pace with SoC Innovation**

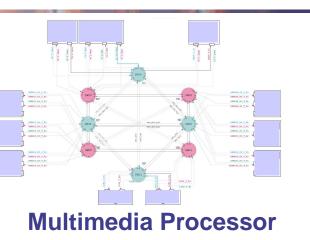

A NoC Instance consists of parameterizable NoC IP elements, Enhances SoC Scalability, low power and high performance

- Network interface units

- Switches

- Rate adaptors

- Width adaptors

- Arbitration blocks

- Sync./Async. FIFOs

- Endianness converters

- Statistical counters

- Clock/reset units

. . . . .

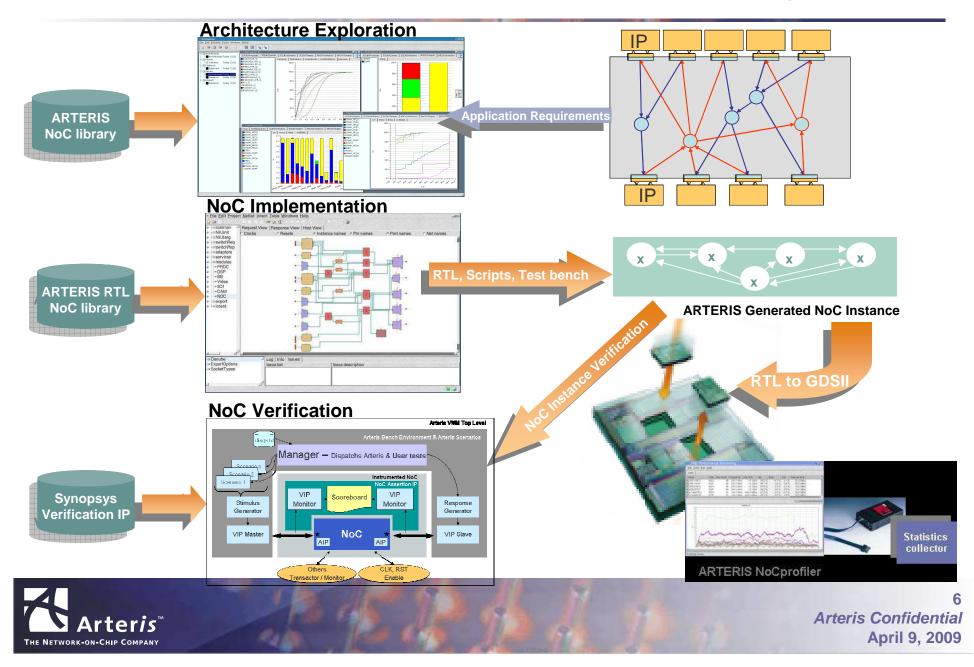

## **NoC Tools Accelerate SoC Delivery**

#### **Power/voltage** isolation NIU NIU **Clusters** NIU NIU NIU $\Sigma\Sigma$ NIU NIU NIU NIU NIU **GALS** link Globally Asynchronous **Reused subsystem** Locally Synchronous CPU AHB AXI DMA Switch AHB AHB AHB BY 'N AB 17 N. ARI 97 VA. **A**11811 HI7 %, AB NIU NIU NIU NIU NIU $\sum \sum$ AHB bus Network NIU NIU NIU NIU AHB AHB AHB 10 N. A 7 N. A 17 W. AN Interface OCP AHB SRAM DRAM Units

### **GALS: Divide and Conquer, Without Redoing Everything**

Synchronous Link

- Low power <1mW idle power for 500K gate NoC IP at 65nm LP</p>

- High speed up to 750Mhz using 65nm TSMC Library

- High bandwidth NoC links scalable from 16 to 256 bits

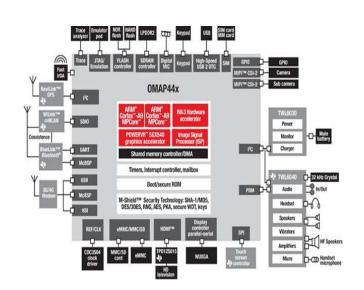

### Are NoCs a Commercial Reality? Yes They Are!

**Wireless Application Processor**

**NEC** pixelworks

Arter*is*'

THE NETWORK-ON-CHIP COMPANY

#### land Flas 8/16bit GPIOs 4x8bit 12S 1/0 DBOP SD/MM I2C SSF JTAG & ICE RAM UART 320kB ROM 128kB ARM922 20-266 MHz CGU lock Ge PLLs RTC Externa 32kHz Osc Ultra IDE Memory **USB 2.0** Memory Stick Pro HS/FS/OT Host PHY

**Automotive Infotainment**

imec

THALES

Nokia Siemens Networks

🐺 Texas Instruments

8 Arteris Confidential April 9, 2009

S