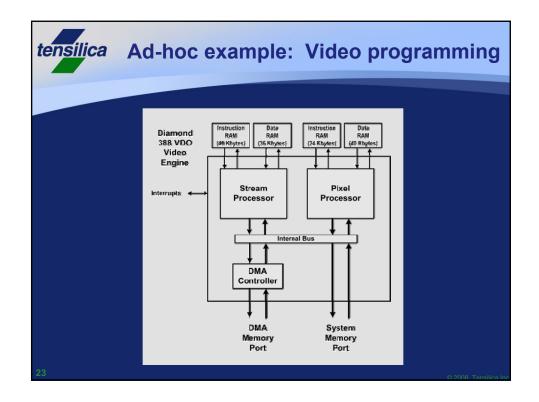

## tensilica An ad-hoc Video programming model

## Start with a new video codec

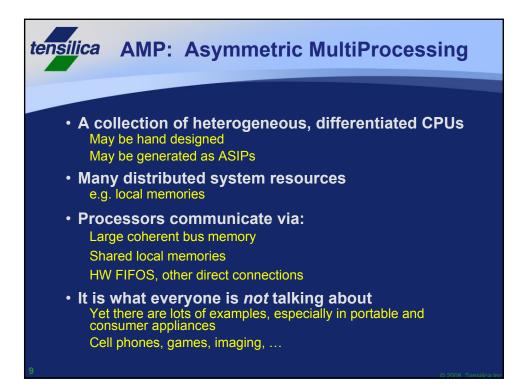

Start with a Single Core model of a 2-core heterogeneous AMP Video Core:

The Single Core model incorporates all the instruction extensions of both cores

- Port/design reference application code on the single core model

- Profile application to find hot-spots on cycle-accurate ISS model

- Speed up hot-spots with relevant using instruction extensions Be careful that 'chunks' of processing use only extensions from one core Simple methodologies to check this

- Split application into 2 sets of files, one per core, emulating DMA data transfer with memcpy

- Port application to multiple cores on ESL model of multicore system, and program DMA

- Performance data on RTL/Emulation model of multicore system

Proven on several Video codecs

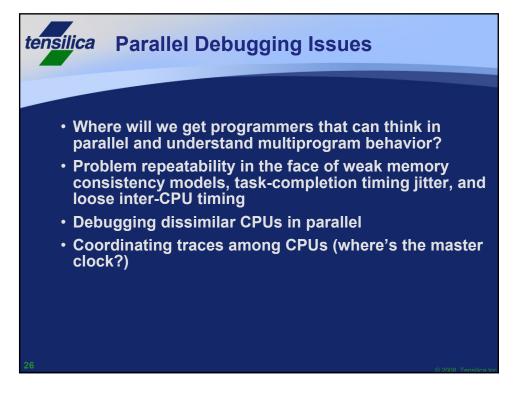

## New Programming Problems Caused by Old Single-CPU Assumptions Latent concurrency issues Explicitly re-entrant code Priorities no longer assure mutex Masking one CPU's interrupts no longer locks New possibilities for race conditions Inter-processor deadlocks Single-CPU crashes can hang entire system Silent parallelization issues through parallel APIs Bad timing assumptions on task completion

Weak memory consistency among CPUs