## **Academic Research**

- Key algorithmic inventions are coming from academic research: Logic synthesis, placement, ...

- · Implementation still mostly based on point-tool view:

- Dedicated data structures and file formats representing only one or few aspects of the design (for example placement problem as boxes and connections)

- Lack of serious "vertical" benchmarks for complete flow.

- Difficult industry adaptation:

- Hard to evaluate true value of new algorithm

- Most likely need to reimplement from scratch to find out whether it really works and gives good results.

3

Electronic Design Processes Workshop - April 13, 2006

<section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

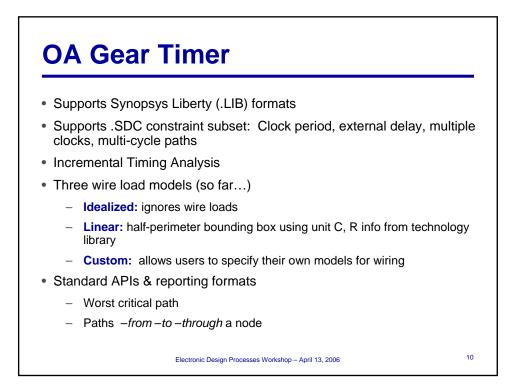

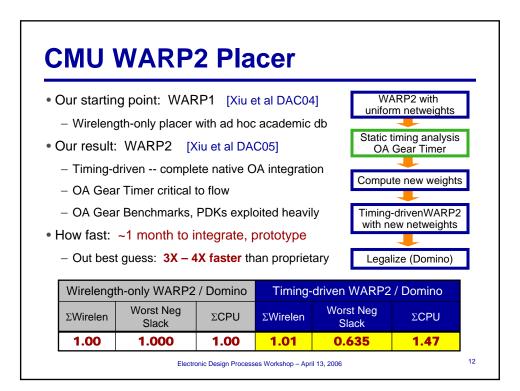

- Timing is often ignored in academic research

- Difficult/expensive to integrate commercial timing engines

- Significant task to write own timer

- Significant calibration/fidelity issues

- Solution: OA Gear Timer

- Common timing infrastructure

- Integrated, rich feature set

- Accurate slew propagation for rise and fall

- Results validate to ~1% against Cadences RTL Compiler tool

- Upside

- Helps ensure results from different researchers can be compared directly

Electronic Design Processes Workshop - April 13, 2006

9

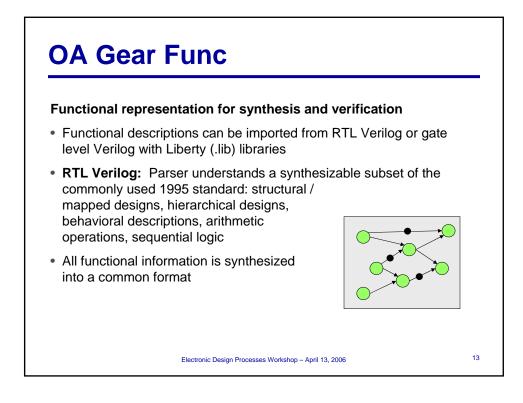

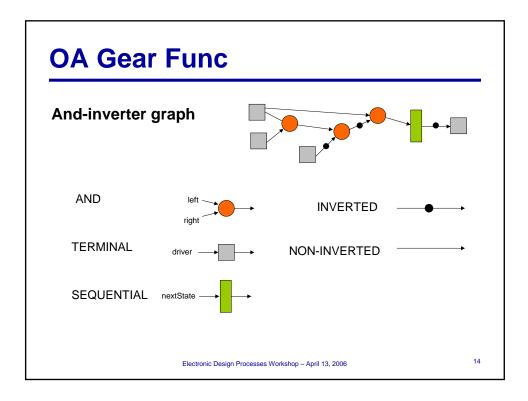

## OA Gear Func

- · Efficient memory management

- Paged allocation, garbage collection, hashing by structural isomorphism

- · Toolbox of useful algorithms

- Transitive fan-in and fan-out

- K-way cut enumeration

- Equivalent node marking and substitution

- · Directly incorporated into OpenAccess database

- Automatically serialized and unserialized

- No data conversion, import/export, etc.

- Tools

- simpleMap a simple mapper (3 different cells: AND, INV, sequential cell)

- equivCheck an equivalence Checker using CU BDD package.

Electronic Design Processes Workshop - April 13, 2006

15

<section-header><section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

## **OA Gear Team**

| Zhong Xiu           | Carnegie Mellon University    | Timer, Warp          |

|---------------------|-------------------------------|----------------------|

| David Papa          | Univ. of Michigan             | Bazaar, Capo Wrapper |

| Afshin Abdollahi    | Univ. of Southern California  | Timer                |

| Aaron Hurst         | Univ. of California, Berkeley | Functional Layer     |

| Haifeng Qian        | Univ. of Minnesota            | Extractor            |

| Luis Guerra e Silva | INESC, University of Lisbon   | Statistical Timing   |

| Philip Chong        | Cadence Berkeley Labs         | OA Gear              |

| Christoph Albrecht  | Cadence Berkeley Labs         | OA Gear              |

| Andreas Kuehlmann   | Cadence Berkeley Labs         | OA Gear              |

| Joel Phillips       | Cadence Berkeley Labs         | OA Gear              |

| Rob Rutenbar        | Carnegie Mellon University    | Warp                 |

| Igor Markov         | Univ. of Michigan             | Саро                 |

Electronic Design Processes Workshop – April 13, 2006

19