# A New Methodology for AMS SoC Design that Enables AMS Design Reuse and Achieves Full-Custom Performance

Kazuhiro ODA<sup>1</sup>, Louis A. Prado<sup>2</sup>, and Anthony J. Gadient<sup>2</sup> <sup>1</sup>Toshiba Corp. 580-1, Horikawa-cho, Saiwai-ku, Kawasaki, 212-8520, JAPAN <sup>2</sup>Neolinear, Inc., 583 Epsilon Drive Pittsburgh, PA 15238

EDP 2002 Monterey, CA

#### **Overview**

- Background

- Circuit Design

- Layout Design

- Results

- Conclusion

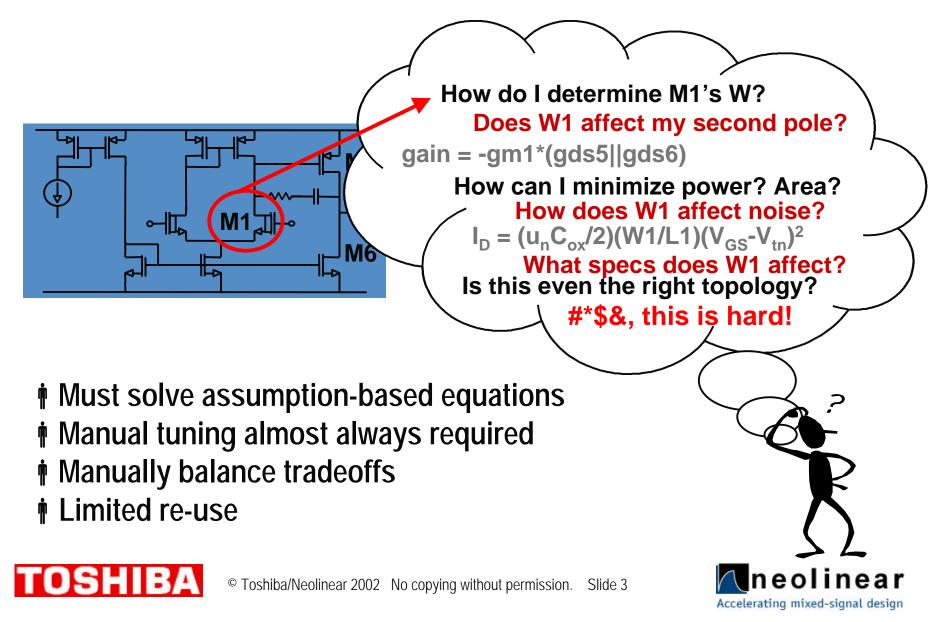

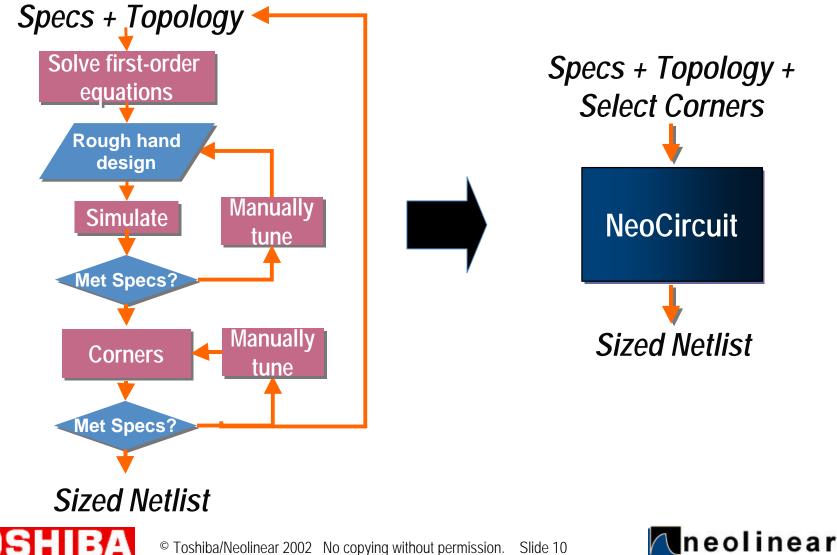

# **Analog Circuit Sizing: Manual Process**

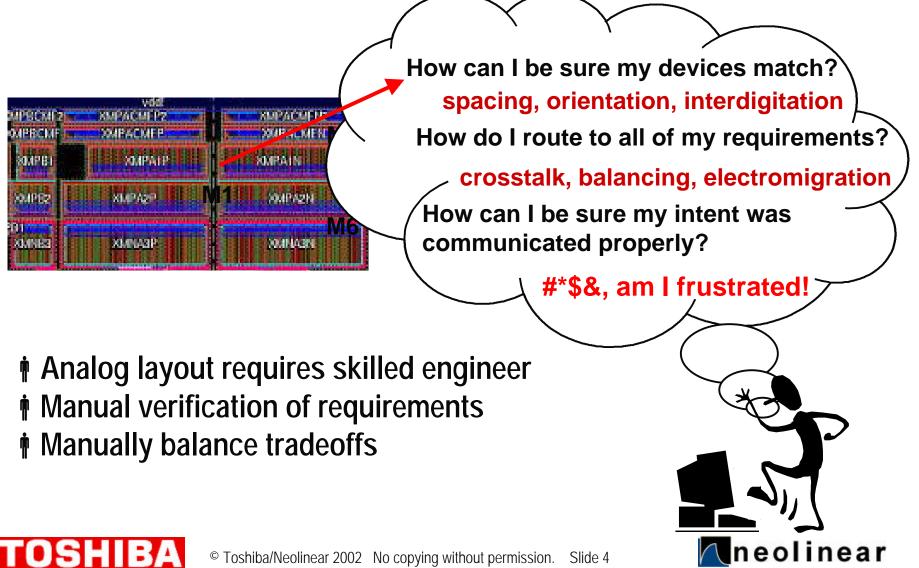

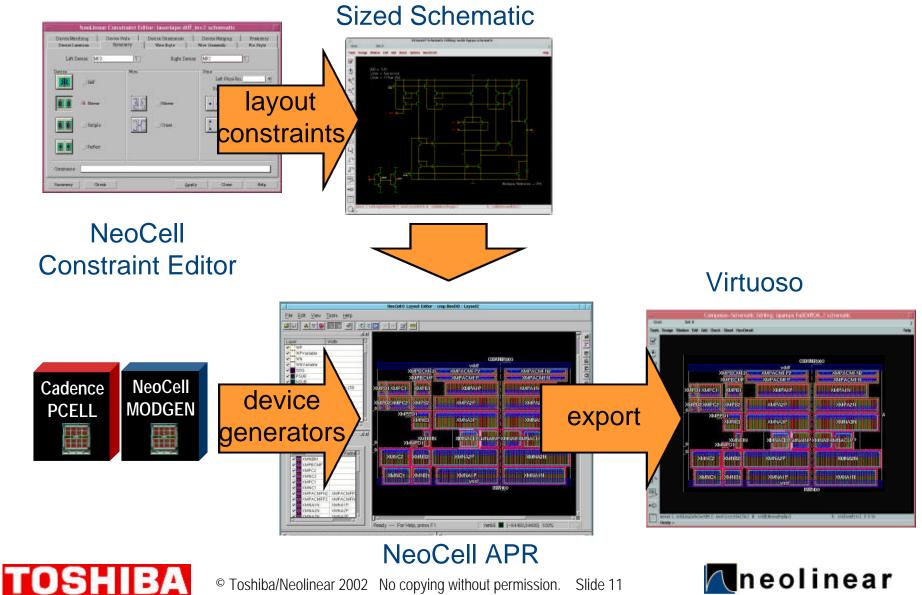

### **Analog Layout: Manual Process**

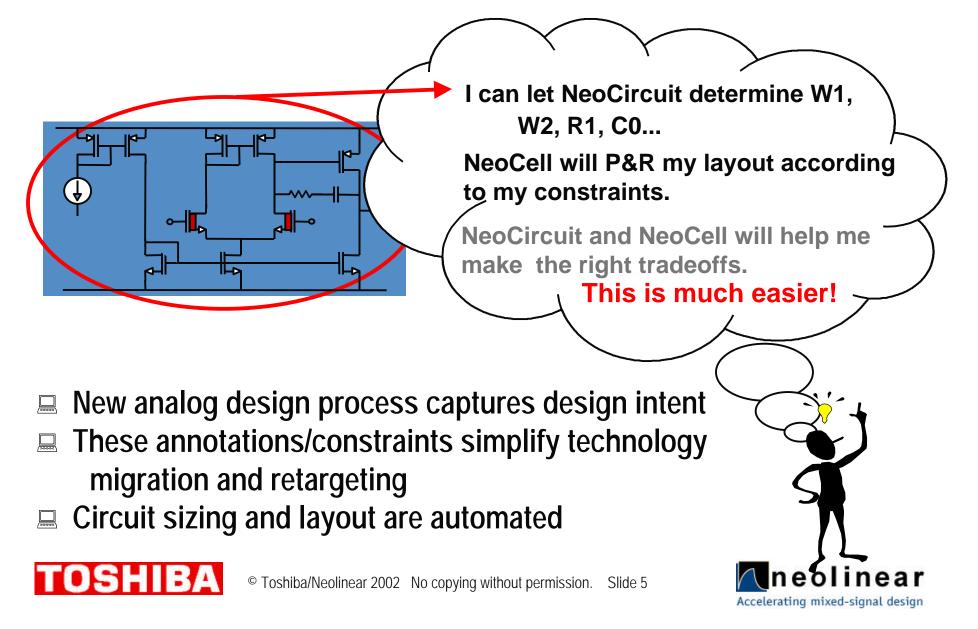

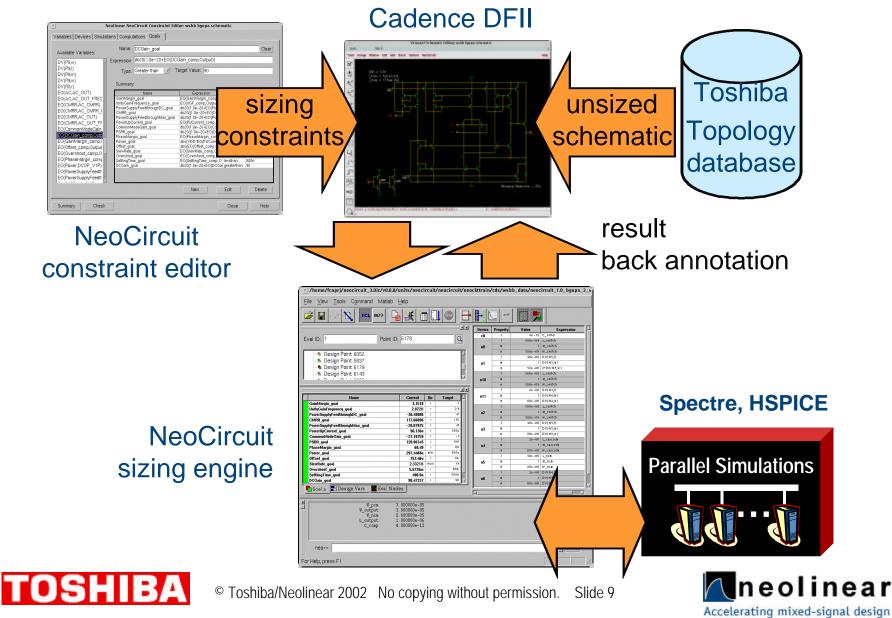

### Sizing and Layout with New Process

# Case Study: Analog-Digital Converter

- Toshiba's new analog design process is based on Neolinear's NeoCircuit and NeoCell tools.

- Toshiba used these tools to automatically size and layout all the cells for a 0.14um 10-bit 1us SAR ADC.

delay

The ADC design is based on a 0.18um 7us 10-bit SAR ADC design.

### **Circuit Design: List of Cells**

| Circuit           | Analysis  | Specification(s)       |

|-------------------|-----------|------------------------|

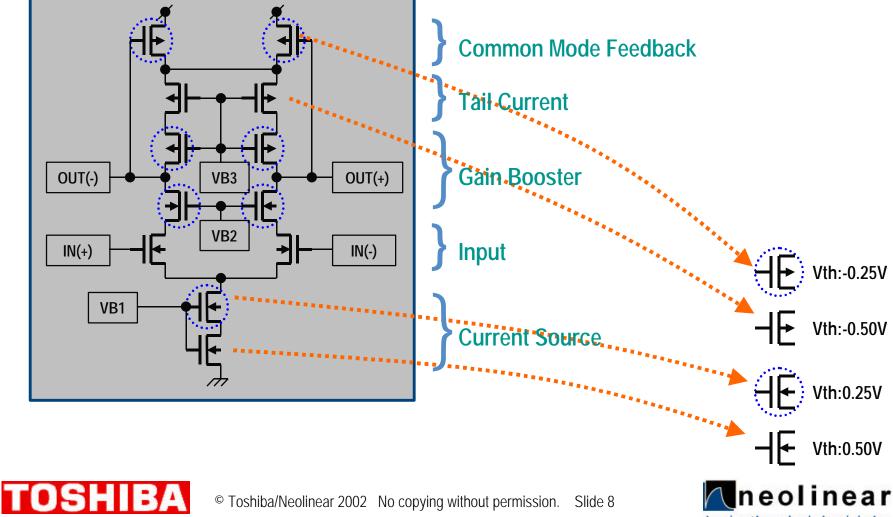

| Full-Diff Chopper | AC        | DC-Gain, ft, Idd, CMFB |

| Comparator        | Transient | Auto-zero, gain        |

| Resistor ladder   | DC        | DC Accuracy, Idd       |

| DAC               | Transient | Settling time.         |

| Constant Current  | DC        | lout, Idd              |

| Source            | Transient | Start-up time.         |

| Level Shifter     | Trasient  | Delay, Idd             |

| Gate Delay        | Transient | Delay, Idd             |

hard to design manually

......

# Circuit Design: Comparator Circuit 7 Transistors Stacked in 2.5V Process!

# Analog Circuit Sizing with NeoCircuit

### Manual Circuit Sizing vs Automated Circuit Sizing

### Analog Circuit Layout with NeoCell

© Toshiba/Neolinear 2002 No copying without permission. Slide 11

#### Results

|                | Original<br>Design | New<br>Design   |               |

|----------------|--------------------|-----------------|---------------|

| Base Process   | 0.18um             | 0.14um          |               |

| Analog Process | 0.25um             | 0.25um          | CMP/<br>BIAS  |

| Res/Speed      | 10-bit/7us         | 10-bit/1us      |               |

| ldd            | 0.4mA              | 0.5mA           |               |

| Iref           | 0.22mA             | 0.75mA          | Level Shifter |

| Core Size      | 176800sqr<br>um    | 184500sqr<br>um | Digital       |

#### **Results**

| Cell                        |     | cuit<br>sign |     | yout<br>sign | Comments                                                                                                                                                |

|-----------------------------|-----|--------------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | Old | New          | Old | New          |                                                                                                                                                         |

| Chopper<br>Comparator       | 4w  | 1d           | 3w  | 3d           | <ul> <li>✓ Difficult design</li> <li>✓ 7 transistors stacked in<br/>2.5V process</li> </ul>                                                             |

| Resistor<br>Ladder<br>DAC   | 1 w | 1 w          | 3w  | n.a.         | <ul> <li>✓ Previous design did not<br/>meet settling time<br/>specification</li> <li>✓ New design settling time<br/>requirement is 7x faster</li> </ul> |

| Constant<br>Current<br>Bias | 3d  | 1d           | 2w  | 0.5d         | <ul> <li>Previous design not<br/>optimized for<br/>operating/process corner</li> </ul>                                                                  |

| Gate Delay                  | 2d  | 0.5d         | 1d  | n.a.         | ✓ Digital Circuit                                                                                                                                       |

| Level<br>Shifter            | 2d  | 0.5d         | 1d  | n.a.         | Digital Circuit                                                                                                                                         |

### **Conclusion: Circuit Design**

|                          | Conventional<br>(Manual Sizing)                             | New<br>(Automatic Sizing)                                                                                   |

|--------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Design<br>Effort         | High (depends on<br>engineer's skill)                       | Low (mainly computer cycles)                                                                                |

| Quality                  | Usually not optimized<br>(depends on<br>engineer's skill)   | Optimized                                                                                                   |

| Docs                     | Block specs/results<br>are usually unclear                  | Unambiguous specs,<br>designer's intent captured,<br>HTML-based<br>documentation<br>automatically generated |

| Reuse (e.g.,<br>Porting) | Same effort is needed<br>for redesign as original<br>design | Minimal effort (e.g., point to new device models)                                                           |

# **Conclusion: Layout Design**

|                          | Conventional<br>(Manual Layout)                             | New<br>(Analog P&R)                                                 |

|--------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|

| Design<br>Effort         | High (depends on<br>engineer's skill)                       | Low                                                                 |

| Layout<br>Quality        | Good                                                        | OK (manual modification<br>may be needed for<br>equivalent quality) |

| Docs                     | Layout<br>requirements are<br>usually unclear               | Unambiguous specs, layout engineer's intent captured as constraints |

| Reuse (e.g.,<br>Porting) | Same effort is<br>needed for redesign<br>as original design | Minimal effort (reuse<br>constraints and device<br>positions)       |

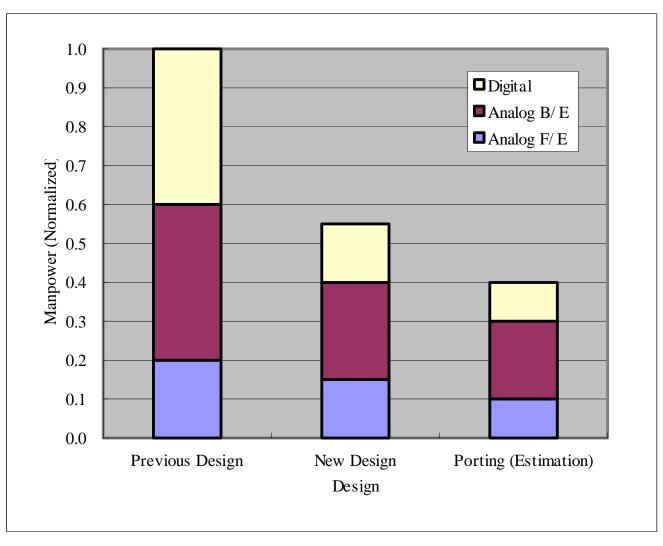

### **Conclusion: Design Effort**

© Toshiba/Neolinear 2002 No copying without permission. Slide 16

# Summary

- Reduced design time for initial design

- Equal or better design quality

- Designer intent is fully captured

- Reuse of analog/mixed-signal designs is now possible