## cādence

- Digital CMOS

- .25  $\rightarrow$  .18  $\!\mu$  technologies

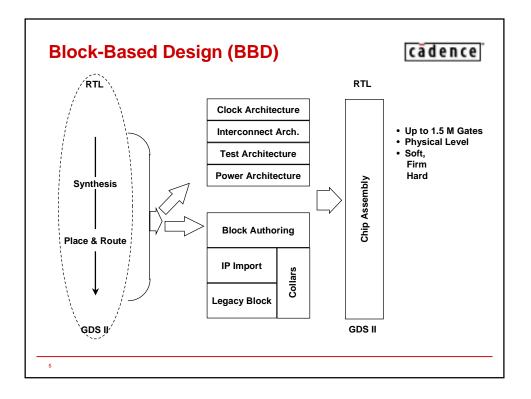

- 150K  $\rightarrow$  1.5 M gates

- A/MS blocks restricted to:

- blocks specified by VSI 1.0, A/M-S VSI Extension

- e.g., PLLs, A/D, D/A, and hard blocks

- Import cores, mc, and mp as hard or firm;

- Technology rules, cell libraries, hard blocks, memory generators and data path blocks are fully defined and qualified

- Synchronous (~ 80 MHz)

- multiple clock domains: All domains are integral multiples of the lowest freq. domain

- Multiple levels of hierarchy

- deal with only two at one time

- Embedded bus architecture

- not pre-designed

- no previous layout (I.e custom)

- single or mixed voltages for A/MS blocks only

- Blocks created using enhanced TDD process for both VHDL and Verilog

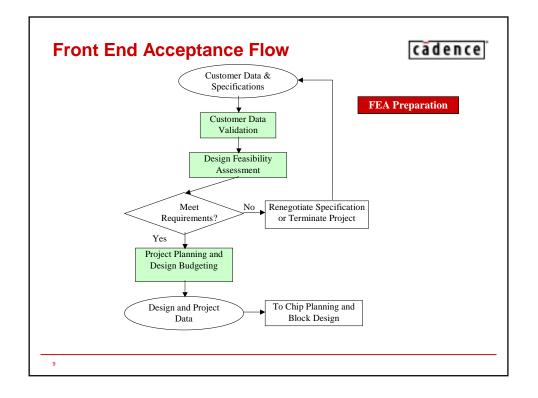

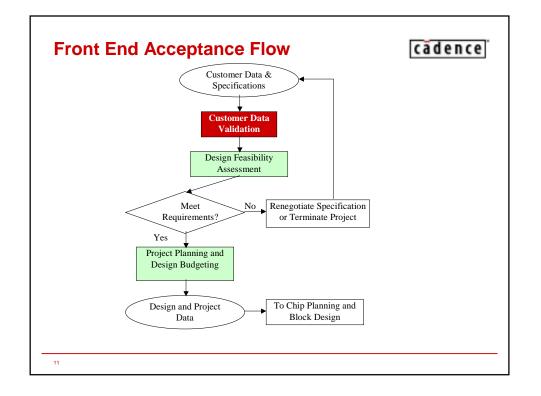

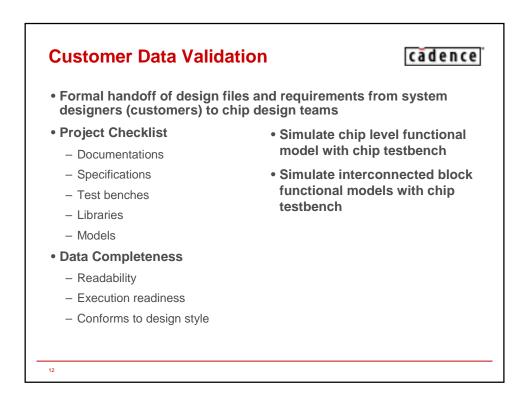

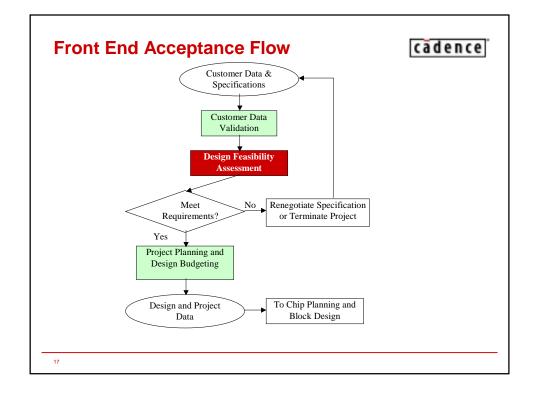

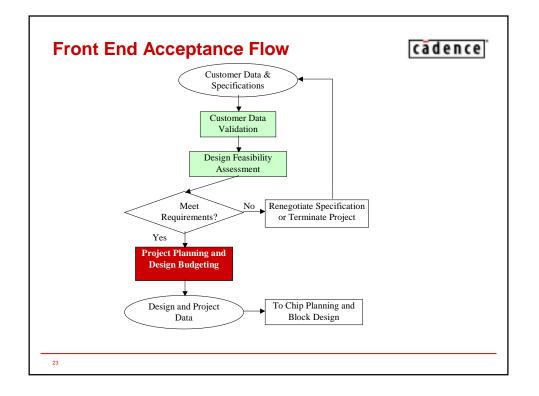

## Front End Acceptance Purposes

cadence

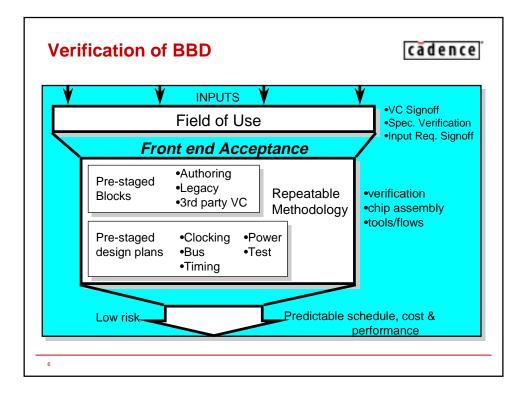

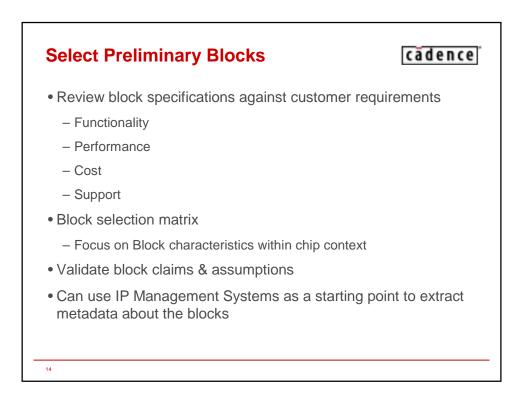

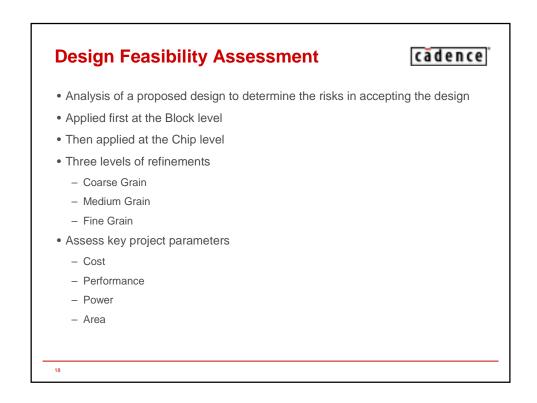

- Align expectations of system designers and chip design teams

- Ensure that all required data to complete the chip design has been assembled

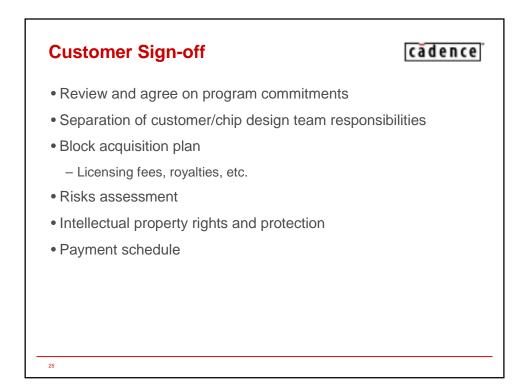

- Develop program commitments with associated risk factors :

- Cost

8

7

- Engineering & Manufacturing

- Schedule

- Functionality

- Performance, area, power

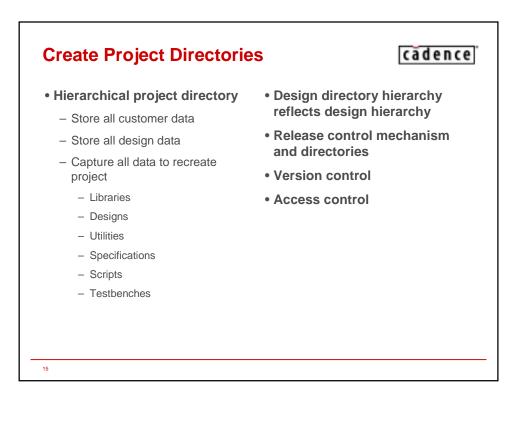

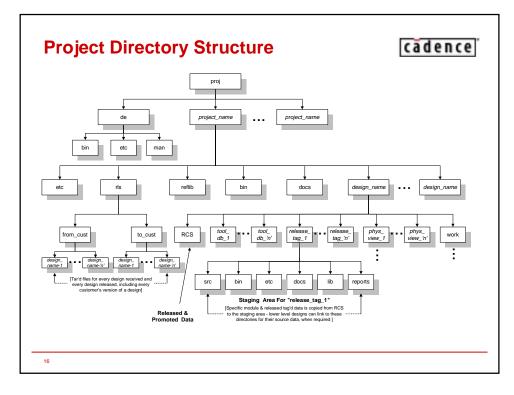

- Create project data management environment

- File structures, access control, release control, version control

## **cadence** *bow big can you dream*?™